冯诺依曼存储子系统的改进

冯诺依曼存储子系统的改进

摘要 由于冯诺依曼体系结构存在串行性特点,成为了其发展的瓶颈,针对其串行性人们提出了若干改进和改变措施,涉及到CPU子系统、存储器子系统和IO子系统.本文讨论涉及到存储子系统

关键词 冯诺依曼 串行 瓶颈 存储子系统 改进

冯·诺伊曼结构(Von Neumann architecture)是一种将程序指令存储器和数据存储器合并在一起的计算机设计概念结构.由于冯诺依曼体系结构存在串行性特点,成为了其发展的瓶颈.当今有许多计算机都采用冯诺依曼体系结构,所以对冯诺依曼体系进行改进的研究有很大的现实意义.

1 存储子系统存在的问题

1.1存储器读取的串行性:

冯诺依曼体系结构具有两个明显的特点,一是计算机以存储程序原理为基础,二是程序顺序执行.存储器是现代冯•诺依曼体系的核心,指令与数据混合存储,程序执行时, CPU 在程序计数器的指引下,线性顺序地读取下一条指令和数据.

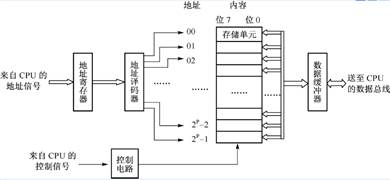

Fig. 1.Memory of Computer Model

所有对内存的读取都是独占性的,每一个瞬间,内存实体只能被一个操作对象通过片选信号占据.这就决定了内存的串行读取特性,对内存的操作无法并发进行.

1.2内存墙—存储器和CPU数据流量障碍:

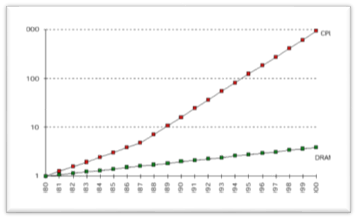

由于CPU速度远大于存储器读写速率[1],据统计,处理器的性能以每年60%的速度提高,而存储器芯片的带宽每年却只提高10%,工艺水平的发展已使两者之间的带宽间隙越来越大.

Fig. 2. Processor-memory performance gap: starting in the 1980 performance, the microprocessor and memory performance over the years

处理器从存储器取一次数的同时,将可以执行数百至数千条指令,这就意味着CPU将会在数据输入或输出存储器时闲置.在CPU与存储器之间的流量(数据传输率)与存储器的容量相比起来相当小,在现代计算机中,流量与CPU的工作效率相比之下非常小,在某些情况下(当CPU需要在巨大的数据上运行一些简单指令时),数据流量就成了整体效率非常严重的限制.CPU将会在数据输入或输出存储器时闲置,无法充分发挥计算机的运算能力.因此内存预取是一个关键的瓶颈问题,也被称为“内存墙”(Memory Wall)

2存储子系统的改进

2. 1使用并行技术:

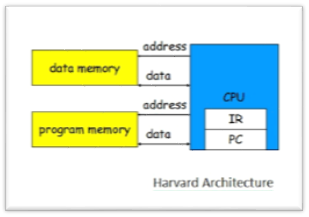

改善的出路是使用并行技术,在指令运算处理及数据存储上都巧妙地运用并行技术.比如说多端口存储器,它具有多组独立的读写控制线路,可以对存储器进行并行的独立操作.又比如:存储器的访问不再用片选控制,而是可以任意地访问单元,在读写数据时用原子操作或事务处理的思想保证数据的一致性,这就取决于所采取的仲裁策略.哈佛体系则从另一个角度改善冯诺依曼存储器串行读写效率低下的瓶颈.哈佛结构是一种将指令储存和数据储存分开的存储器结构.指令储存和数据储存分开,数据和指令的储存可以同时进行,执行时可以预先读取下一条指令.

Fig. 3. Harvard architecture

2.2分层结构:

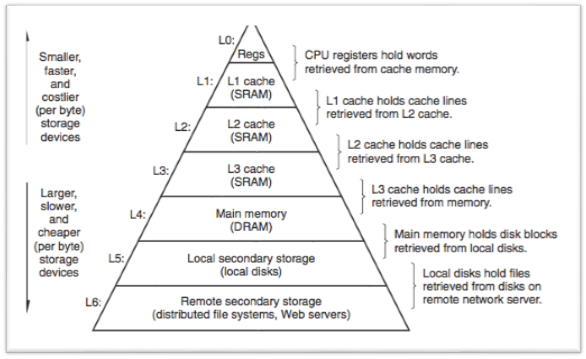

现代高性能计算机系统要求存储器速度快、容量大,并且价格合理.现代计算机常把各种不同存储容量、存取速度、价格的存储器按照一定的体系结构形成多层结构,以解决存取速度、容量和价格之间的矛盾[2].这纾解了内存墙问题.

大多数现代计算机采用三级存储系统:cache+主存+辅存.这种结构主要由以下两个主要的部分组成:

1、 cache存储器系统:cache-主存层次.cache一般由少量快速昂贵的SRAM构成,用来加速大容量但速度慢的DRAM.

2、 虚拟存储器系统:主存-辅存层次

Fig. 4.Memory hierarchy

多层存储体系结构设计想要达成一个目标,速度快、容量大、又便宜. 根据大量典型程序的运行情况的分析结果表明,在一个较短时间间隔内,程序对存储器访问往往集中在一个很小的地址空间范围内.这种对局部范围内存储器地址访问频繁,对范围以外的存储器地址较少访问的现象称为存储器访问的局部性.所以可以把近期使用的指令和数据尽可能的放在靠近CPU的上层存储器中,这样与CPU交互的数据程序就放在更快的存储器内,暂时不用的数据程序就放在下层存储器.CPU等待时间减少了,整机性能就提上来了.

把下级存储器调过来的新的页放在本级存储器的什么地方,确定需要的数据、指令是否在本级,本级存储器满了以后先把哪些页给替换掉,在给上层存储器进行写操作的时候如何保证上下层存储器数据一致等映像、查找、替换、更新操作,这些操作需要合理、高效的算法策略才能保证这种多层结构的有效性.

3 智能存储器[3]

一些研究者预测记忆行为将会优化计算系统的全局性能.他们建议将存储组件与处理核心融合在一个芯片,创造具有处理能力的存储器.这个策略包含intelligent RAM (IRAM)、Merged DRAM/Logic (MDL) 、Process in Memory (PIM) 等等.

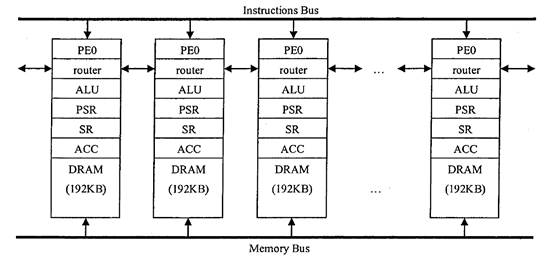

最早的智能存储器是C-RAM,一款由多伦多大学在1992年制造的PIM.这些处理元件通常集成在读出放大器的输出端,由单个控制单元控制,作为SIMD处理器.因为计算元件直接集成到 DRAM输出,这种设计策略可以大量提高DRAM的片上带宽.从结构上讲,这是一种简单的方法,理论上能够实现最高性能. 然而,这也有一些严重的缺点:虽然在结构上简单,但在实际设计和生产中出现了严重的复杂性,因为大多数DRAM核心都是高度优化的,并且很难修改, 这些类型的大规模并行SIMD设计在串行计算中很不成功;

传统的cache组织,解决的只是处理器的时间延迟问题,并不能用来解决处理器的存储带宽问题.PIM技术在DRAM芯片上集成了处理器,从而降低了存储延迟,增加了处理器与存储器之间的数据带宽.

Fig. 5.System Architecture of PIM

基于PIM技术的体系结构的优点在于处理逻辑能以内部存储器带宽(100GB/s甚至更高)直接存取访问片上存储块,从而获取高性能;功耗方面,比与具有相同功能的传统处理器相低一个数量级

参考文献

[1]Carlos, Carvalho. The Gap between Processor and Memory Speeds[J]. icca, 2010, (2): 27-34

[2]李广军,阎波等.微处理器系统结构与嵌入式系统设计.北京:电子工业出版社,2009

[3]师小丽.基于PIM技术的数据并行计算研究[D].西安理工大学,2009.

关于动态RAM和静态RAM

DRAM使用电容保存1位数据,每个电容还配备有一个晶体管控制控制读写电容的状态。由于电容会漏电,所以控制电路需要周期性读取电容状态然后回写以保持电容原本状态。

SRAM使用数个锁存器保存1位数据,所以需要更多的芯片面积。因为不需要周期性刷新,所以速度更快。相应地价格也更高。