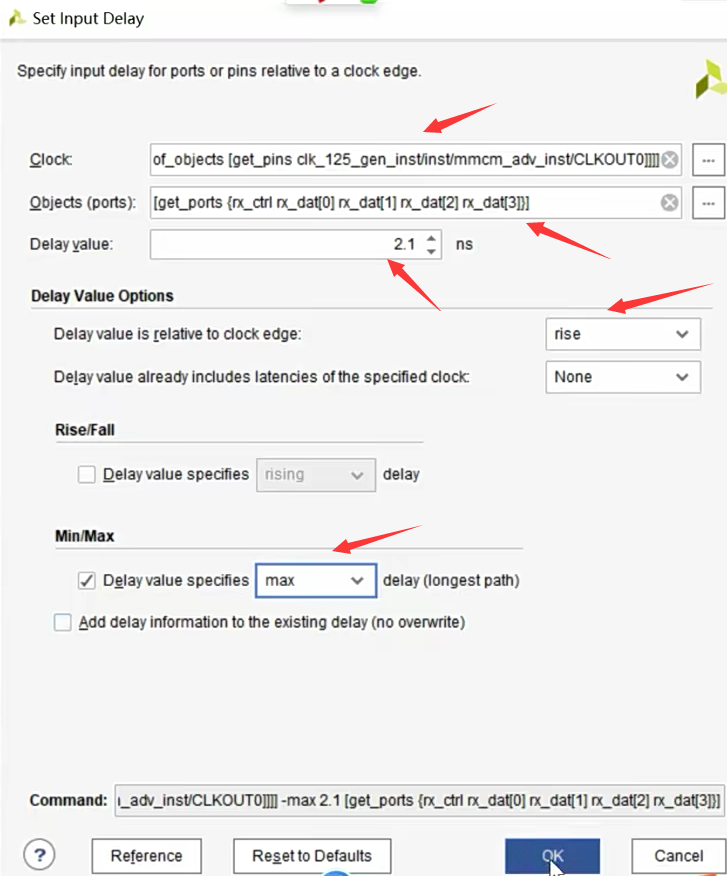

课程中对rx_clk 和 rx_data进行时序约束,实际采用时钟是经过PLL相移的rx_clk_90时钟和rx_data rx_ctrl的约束

假设时钟Tskew的偏斜 = 2 ,数据的偏斜一般都很小,大概是数据周期的1/40,假设周期为8ns, 则数据偏斜为0.2ns 注意,这里是双边沿采样

之前章节的计算方法 : dMax = 2+skew/2 = 2.1

Xilinx 官方计算方法: dMax = Tcycle/2 - dv_bfe = 4 – (2-0.1) =2.1

-------------------------------------------------------------------------

之前章节的计算方法 : dMin = 2 – skew/2 = 1.9

Xilinx 官方计算方法: dMin = dv_bre=2 – 0.1=1.9

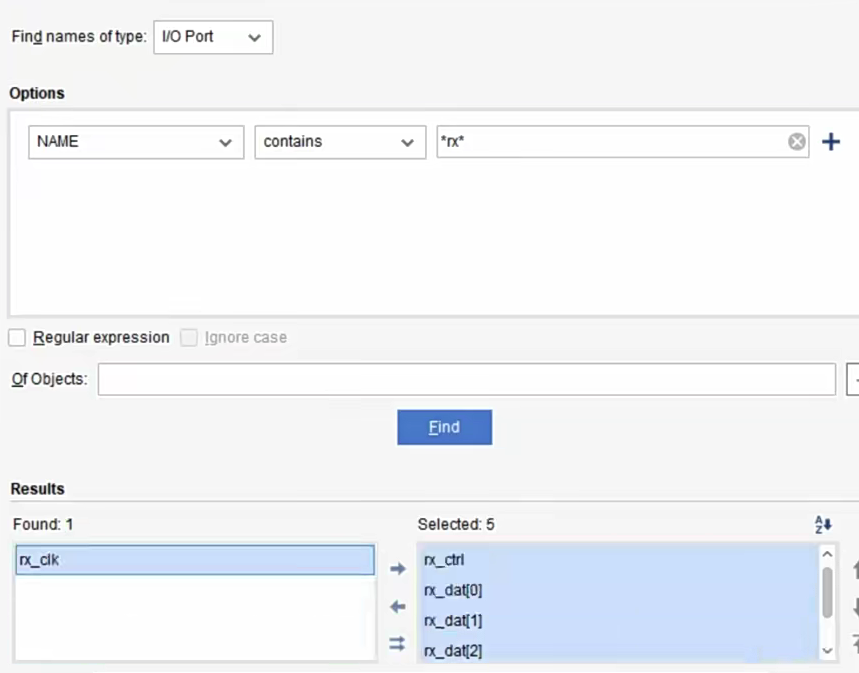

这里查看top的输入数据

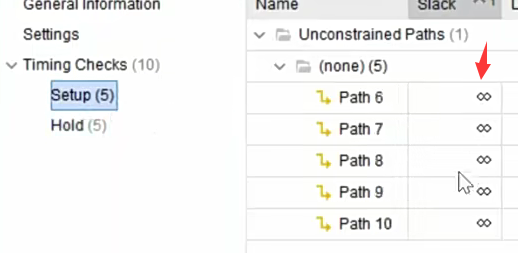

未约束时,set up 和 hold 都是无限大

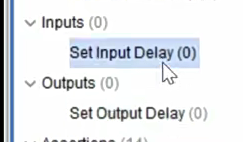

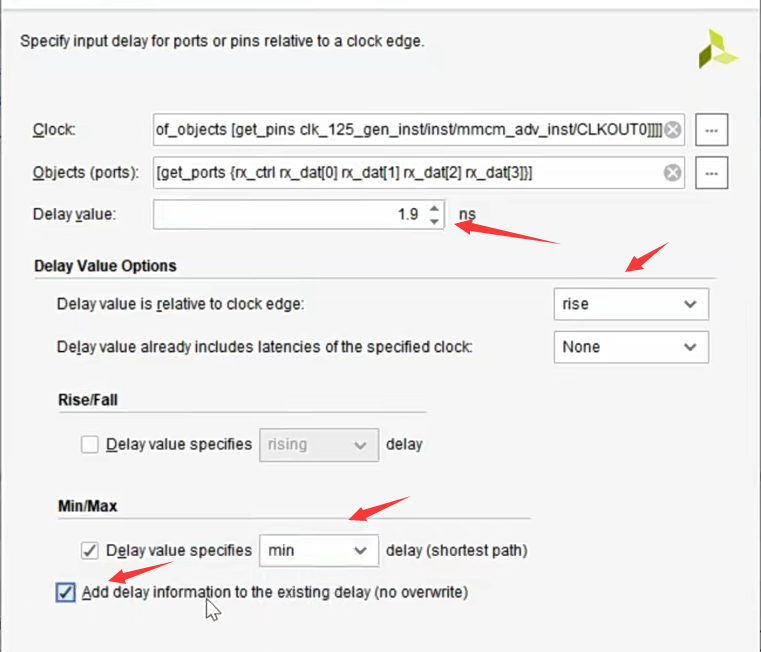

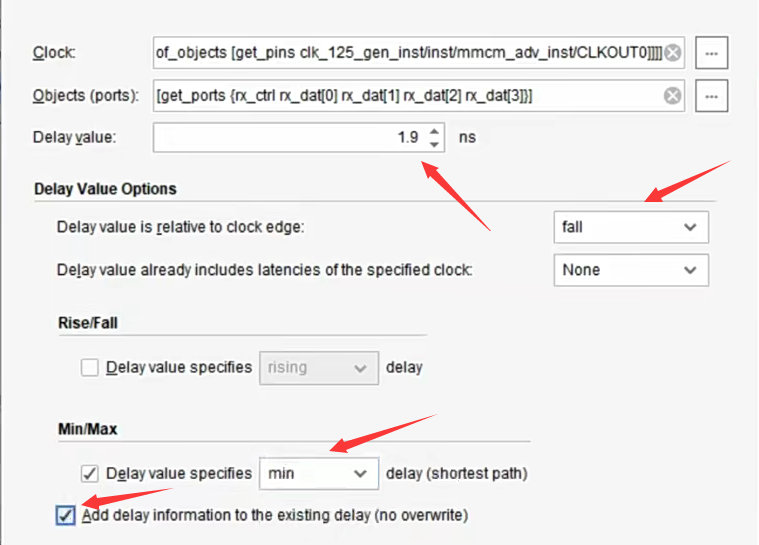

设置input delay

选择相对应的时钟,对应的数据,延迟时间,采样的边沿

再对最小值进行约束

由于是DDR,所以要对下降沿约束

input 时序优化方法之indelay control

使用这个原语可以在 select io HDL 的 user guide 找到也可以在 language template 里找到

.IDELAY_VALUE(0), // Input delay tap setting (0-31), 通过给定不同的值改变延时时间,分辨率为 1/(32x2xFREF)us,当前200M时钟的分辨率是78.125ps

1 IDELAYE2 #( 2 .CINVCTRL_SEL("FALSE"), // Enable dynamic clock inversion (FALSE, TRUE) 不使用动态配置 3 .DELAY_SRC("IDATAIN"), // Delay input (IDATAIN, DATAIN) 延时源的输入端口选择 4 .HIGH_PERFORMANCE_MODE("FALSE"), // Reduced jitter ("TRUE"), Reduced power ("FALSE") 低功耗模式 5 .IDELAY_TYPE("FIXED"), // FIXED, VARIABLE, VAR_LOAD, VAR_LOAD_PIPE FIXED模式 6 .IDELAY_VALUE(0), // Input delay tap setting (0-31), 给定延时值 7 .PIPE_SEL("FALSE"), // Select pipelined mode, FALSE, TRUE 8 .REFCLK_FREQUENCY(200.0), // IDELAYCTRL clock input frequency in MHz (190.0-210.0, 290.0-310.0). 9 .SIGNAL_PATTERN("DATA") // DATA, CLOCK input signal 对数据进行延时 10 ) 11 IDELAYE2_inst_data ( 12 .CNTVALUEOUT(), // 5-bit output: Counter value output 不使用动态配置 13 .DATAOUT(rx_dat_t[i]), // 1-bit output: Delayed data output 数据延时输出 14 .C(1'b0), // 1-bit input: Clock input 15 .CE(1'b0), // 1-bit input: Active high enable increment/decrement input 16 .CINVCTRL(1'b0), // 1-bit input: Dynamic clock inversion input 17 .CNTVALUEIN(5'd0), // 5-bit input: Counter value input 18 .DATAIN(1'b0), // 1-bit input: Internal delay data input 19 .IDATAIN(rx_dat[i]), // 1-bit input: Data input from the I/O 数据输入 20 .INC(1'b0), // 1-bit input: Increment / Decrement tap delay input 21 .LD(1'b0), // 1-bit input: Load IDELAY_VALUE input 22 .LDPIPEEN(1'b0), // 1-bit input: Enable PIPELINE register to load data input 23 .REGRST(1'b0) // 1-bit input: Active-high reset tap-delay input 24 );

此 IP 必须配合 IDELAYCTRL 使用, IDELAYCTRL 只需要引入一个 200M 时钟和复位即可,一般在顶层例化就行了 注意 REFCLK设定的值要和IDELAY里的值对应

1 IDELAYCTRL IDELAYCTRL_inst ( 2 .RDY(RDY), // 1-bit output: Ready output 3 .REFCLK(sysclk), // 1-bit input: Reference clock input 200M 4 .RST(~locked) // 1-bit input: Active high reset input 5 );

output delay约束

建立时间余量计算 Data Required time = Tcycle + Tc_d Data Arrival time = Tco+askew Setup Slack = Data Required time - Data Arrival time = Tcycle + Tc_d – Tco – askew = Tc_d – Tco + (Tcycle - askew) dMax = Tcycle - askew

保持时间余量计算 Data finish time = Tco + Tcycle - bskew Data Required finish time = Tcycle + Tc_d Hold Slack = Data finish time - Data Required finish time = Tco + Tcycle - bskew - (Tcycle + Tc_d) = Tco –Tc_d -(bskew) dMin = bskew

这里设置的 bskew 和 askew 和 input delay 是不一样的思想,input delay 是根据上游器件的参数决定的,而 output delay 是我们设置约束使得我们的时钟不要落到 skew 的区间内,这样我们可以通过调整 skew 的值使时钟在一个中心位置。

通过约束 askew 和 bskew 的值,综合工具会调整布线长度使得时钟落在 a/bskew 之间红色箭头指示的区间,如果落在了bskew 和 askew 范围内就会出现时序违例。我们设置 askew=bskew=1.5,dMax=8/2-1.5=2.5,dMin = 1.5。注意这里是ODDR输出