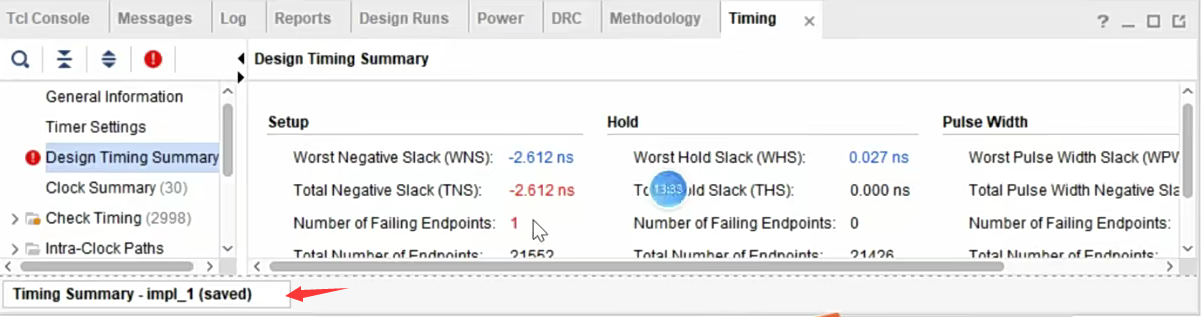

关于输入时钟的时序约束,如果输入的基准时钟没有送入PLL就直接给内部模块使用,那么需要进行时序约束,点击IMPLEMENTATION,完成后打开报告

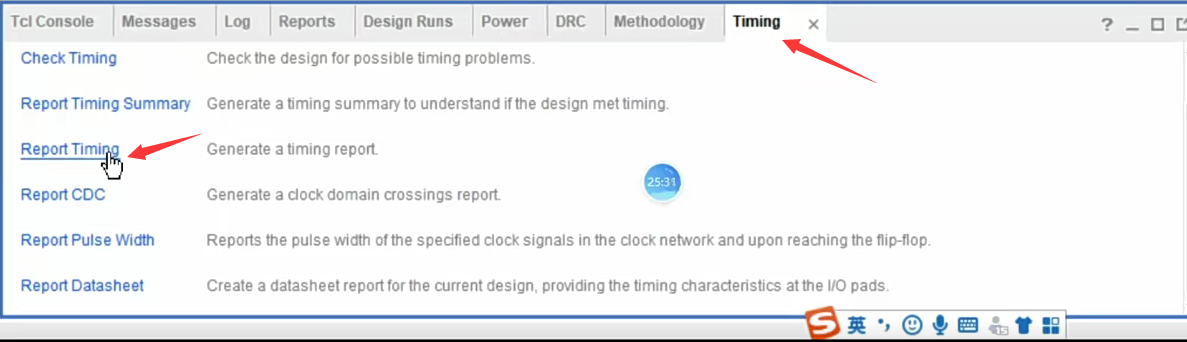

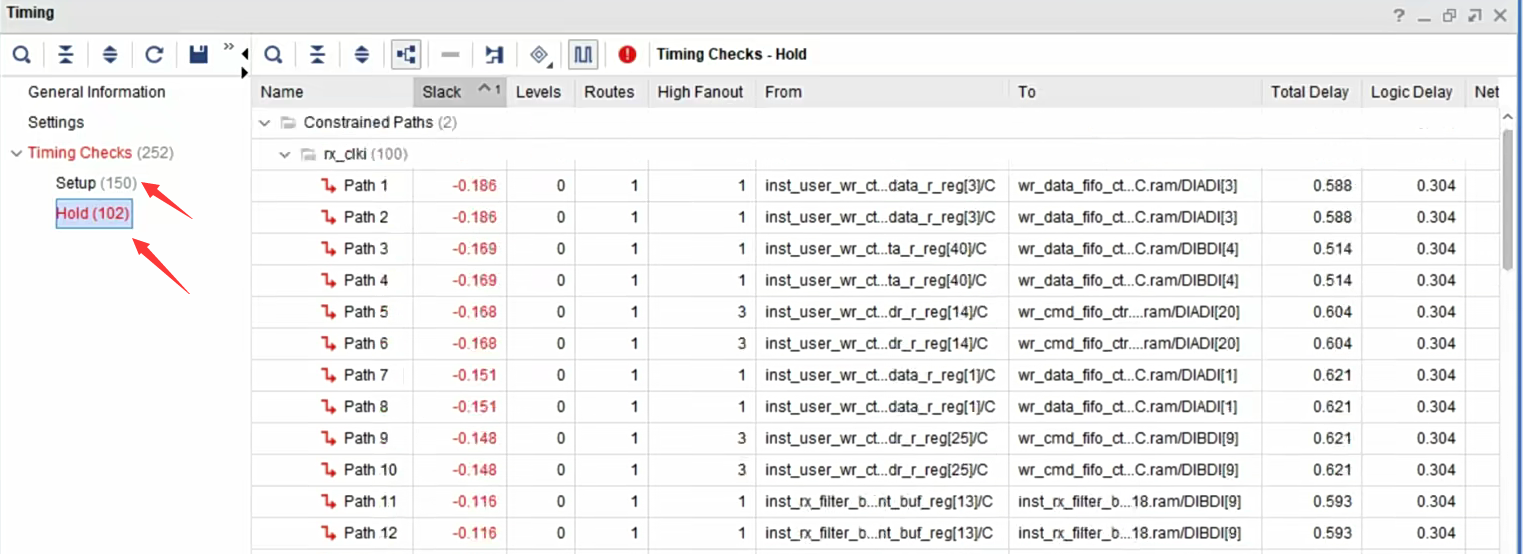

时序报告,关闭红色箭头所指的报告

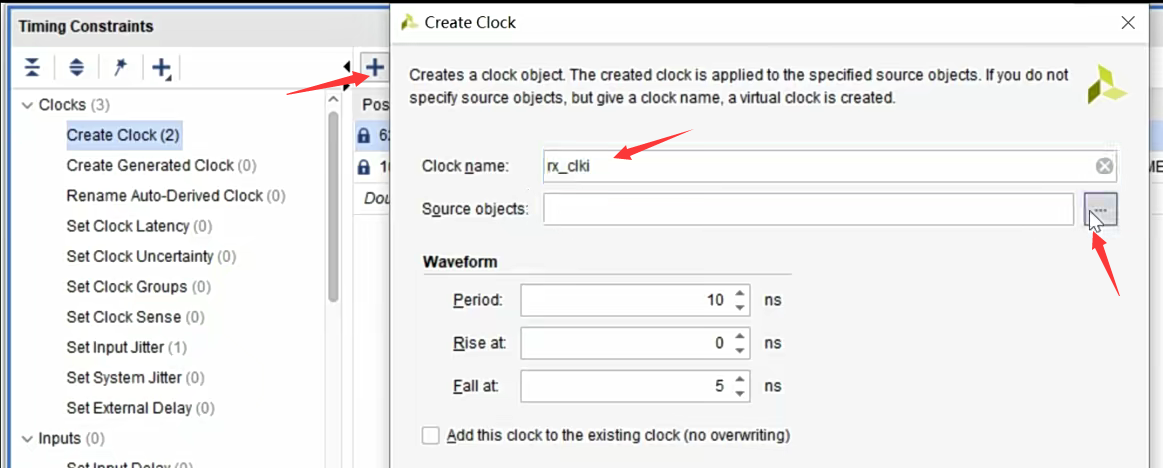

进行时钟的约束

点击加号,添加需要约束的时钟,输入时钟的名称(可自定义),添加时钟源

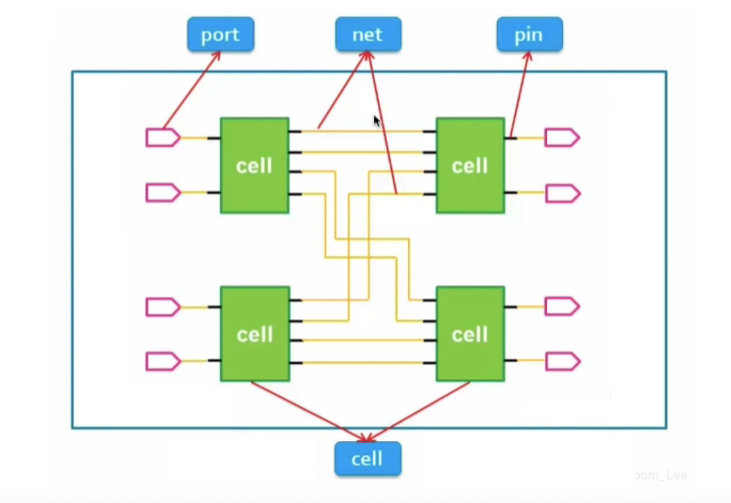

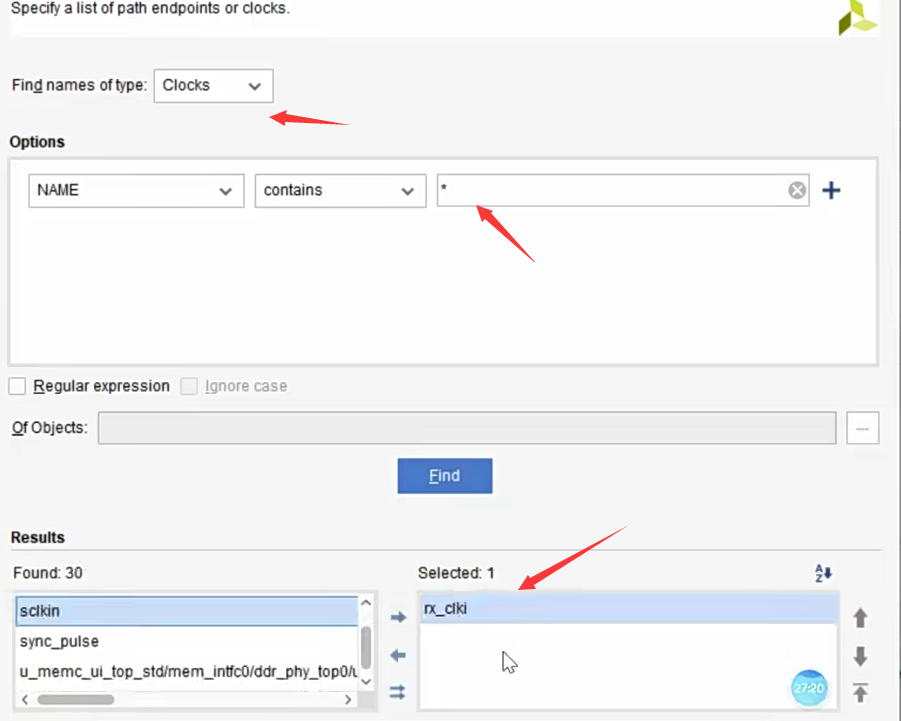

I/O Port指top层的输入输出接口,Cell Pins指 RAM PLL等的Pin ,Nets指各个Cell之间的连线,*指通配符

get_ports # I/O ports, FPGA管脚

get_pins # cell pins, 模块接口

get_nets # nets,模块内部net

查找到相应时钟后点击Set,Append指附加约束,这里不用

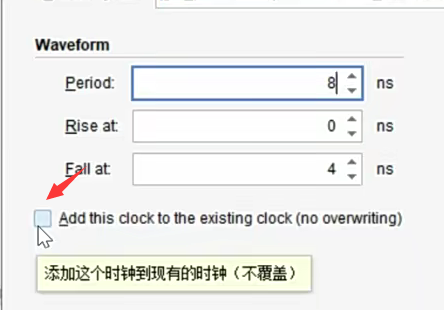

如果当前节点有两个不同的时钟,或者只是单边沿触发时钟,那么需要勾选,这里不勾选。

约束完成后,点击保存,然后重新Run Implementation

在TCL中输入report_clocks rx_clki 查看时钟约束,时钟约束后可以查看在当前时钟域的时序信息。

在Timing中查看时序报告

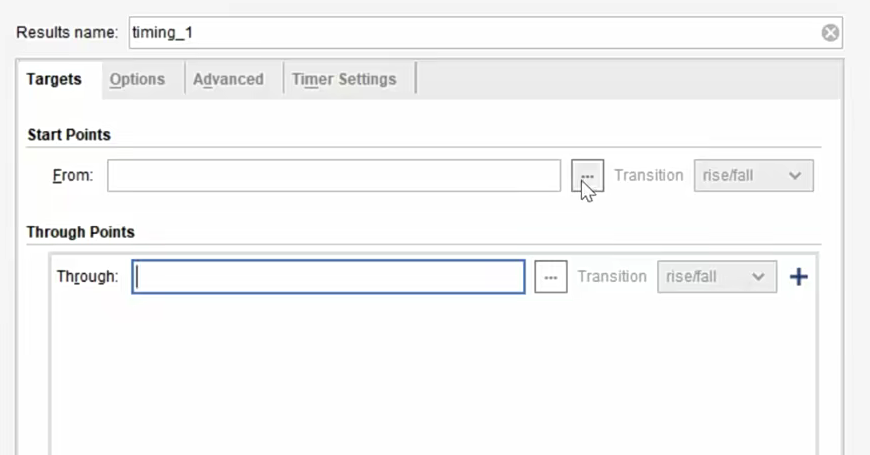

进入后,只选择From端口,那么所有的关于此时钟的都会打印出来

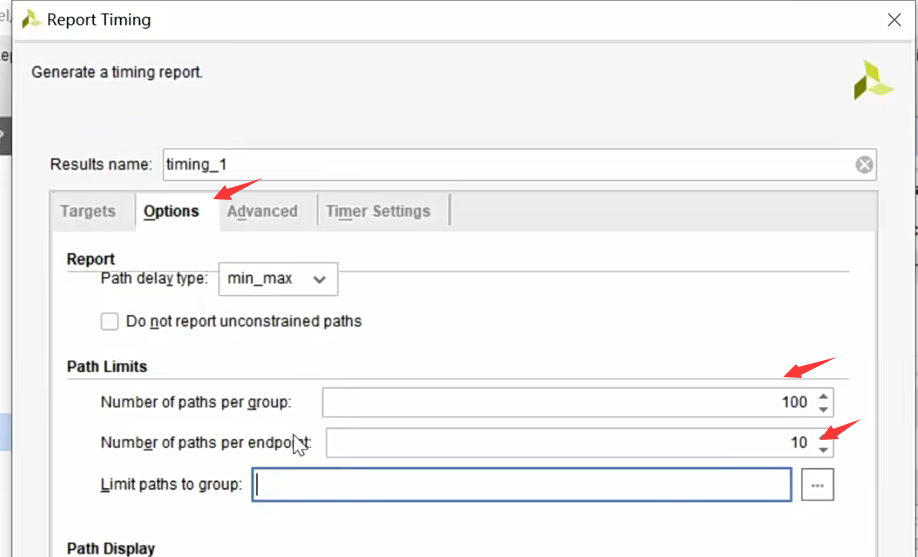

设置打印信息的路径数

设置完成后可以查看时序信息

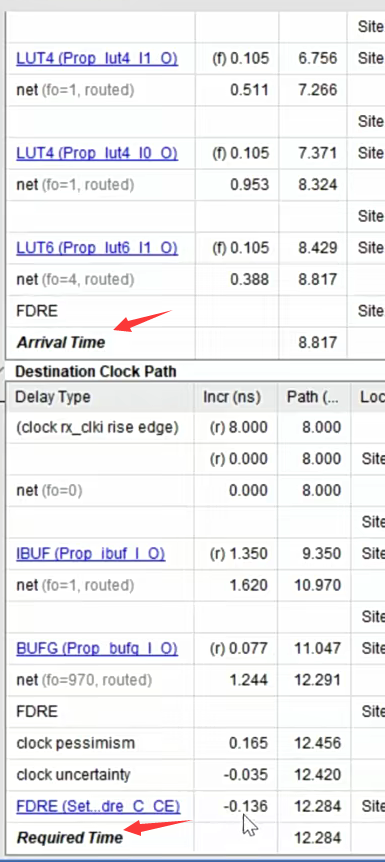

set up时序,要求Required time - arrival time > 0

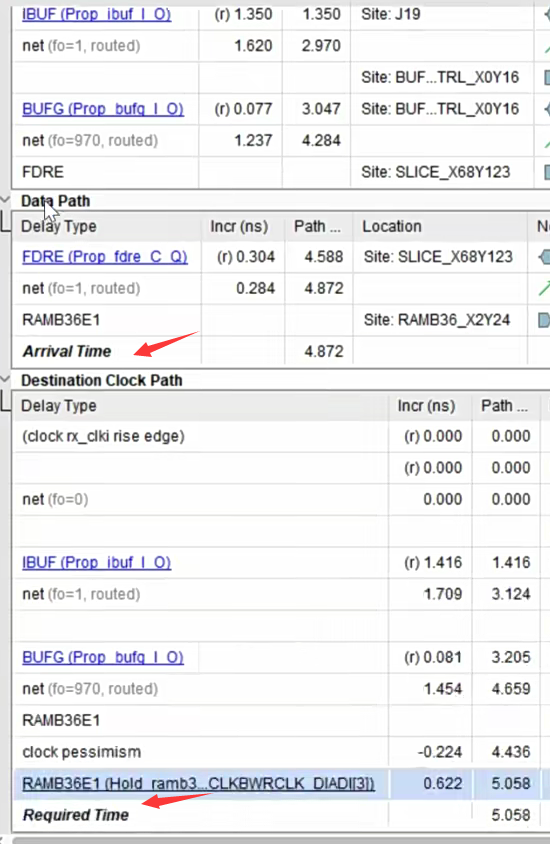

hold 时序,要求Required time - arrival time < 0,如下图则时序违例

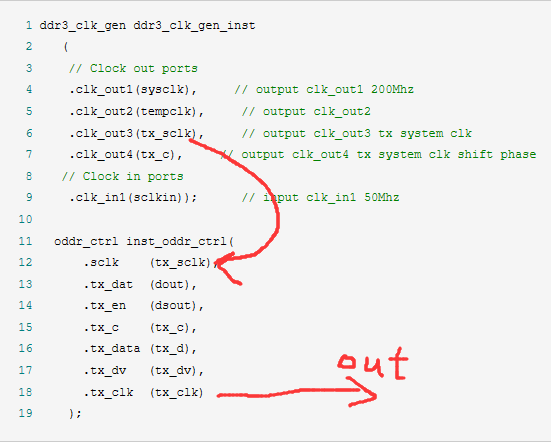

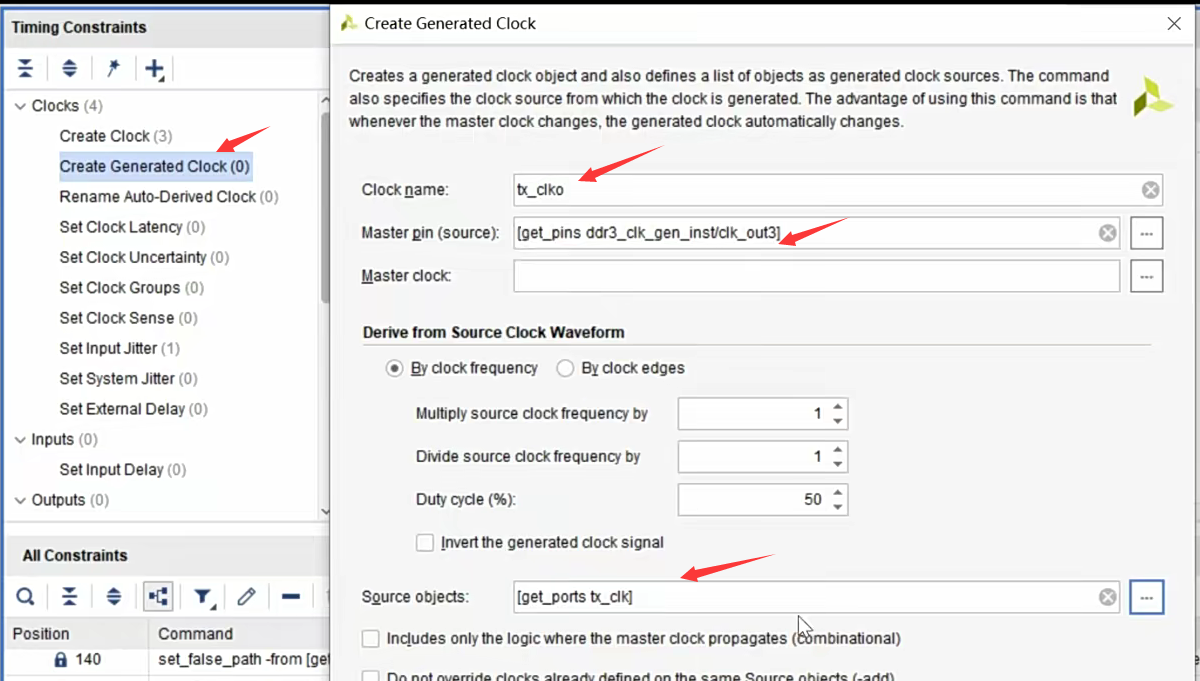

对于生成时钟的约束,从PLL的clk_out3出来,进入oddr_ctrl模块,通过内部的ODDR原语输出tx_clk

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· Manus的开源复刻OpenManus初探

· AI 智能体引爆开源社区「GitHub 热点速览」

· C#/.NET/.NET Core技术前沿周刊 | 第 29 期(2025年3.1-3.9)

· 从HTTP原因短语缺失研究HTTP/2和HTTP/3的设计差异