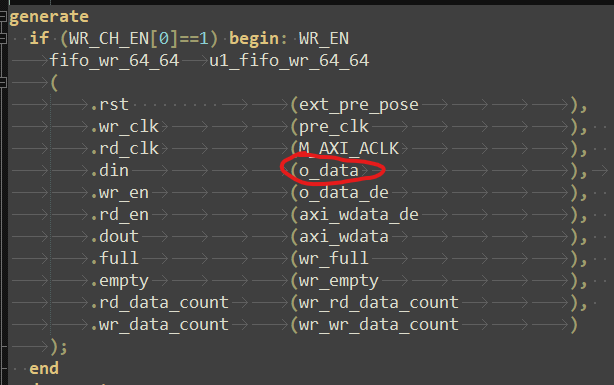

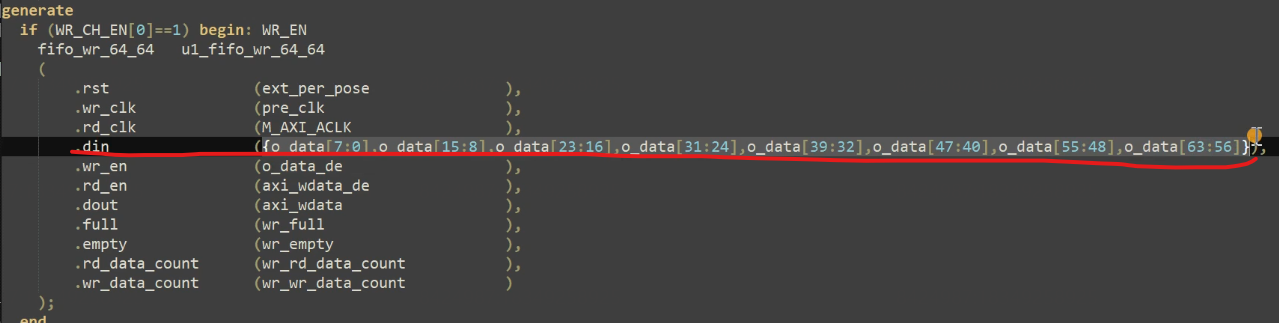

FPGA与ARM大小端的问题,在做FPGA移位拼接时,将先到的数据放到了高位,放在DDR中的数据顺序应该是按照地址 0 1 2 3 排列 0 1 2 3数据,即高位数据放在低地址,也就是所谓的大端模式,然后在SDK中,将DDR中的数据同步到ARM时,由于ARM采用的是小端模式,所以按照地址0 1 2 3存放的数据是3 2 1 0,也就是小端模式

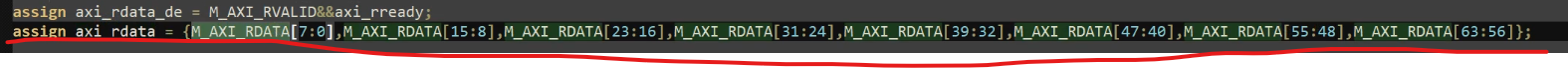

所以为了在ARM中导出数据没问题,需要对输入的数据进行换位

存的时候反位了,读的时候也要反一下位,并且对于FIFO读写位宽不同来讲,都是从高位进,从高位出。