在SDK中使用xil_DCacheDisable();

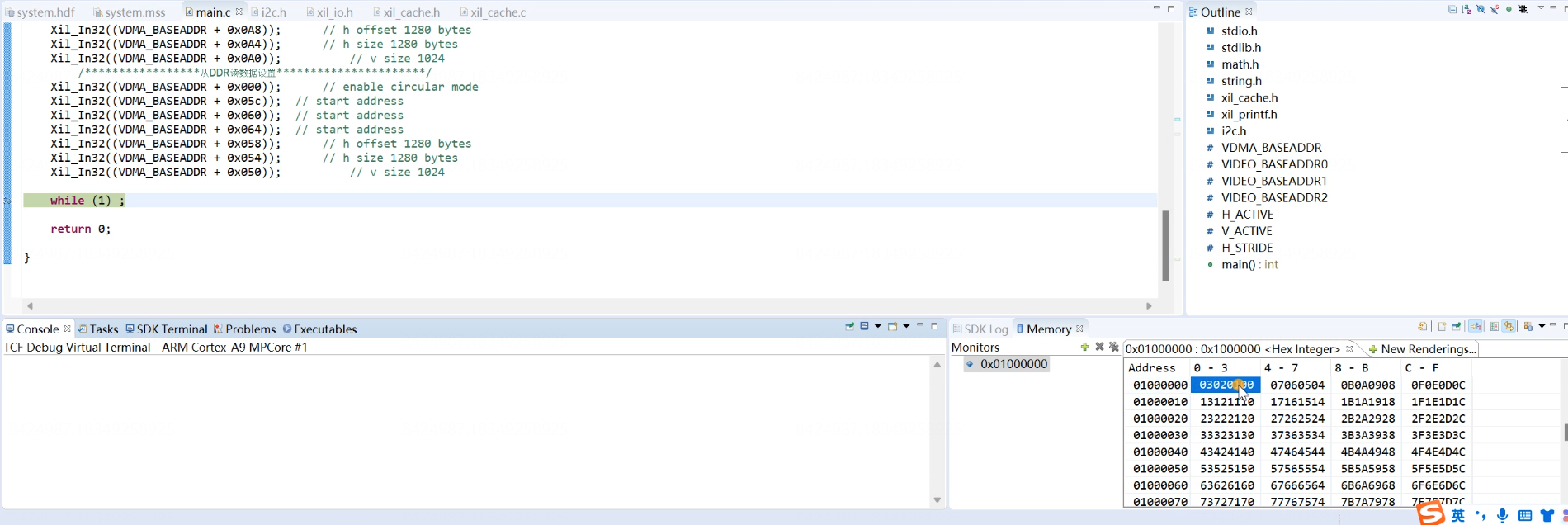

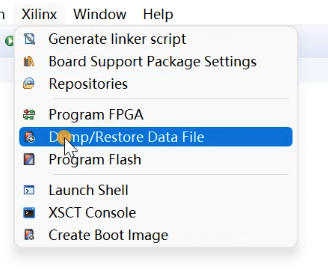

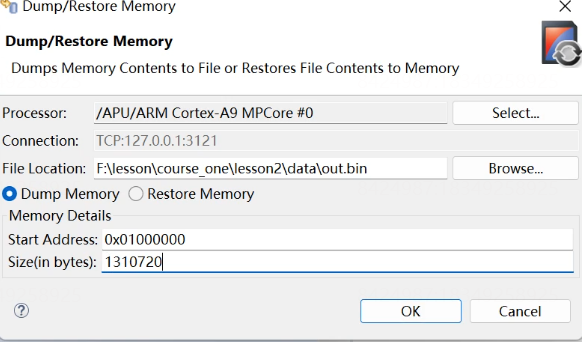

导出内存中的数据

所得的BIN文件可以用WINHEX打开

matlab代码 bin2bmp

clear; clc; close; p_fid = fopen('../data/out.bin','r'); a = fread(p_fid); col = 1280; row = 1024; IM = reshape(a,col,row); b=uint8(IM)'; imwrite(b,'../img/out.bmp'); imshow('../img/out.bmp');

bmp2bin

lear; clc; close all; a = imread('../img/out.bmp'); %a = rgb2gray(a); imshow(a); [row,col] = size(a); p_fid = fopen('../data/in.bin','w+'); fwrite(p_fid,a','uint8'); fclose(p_fid);

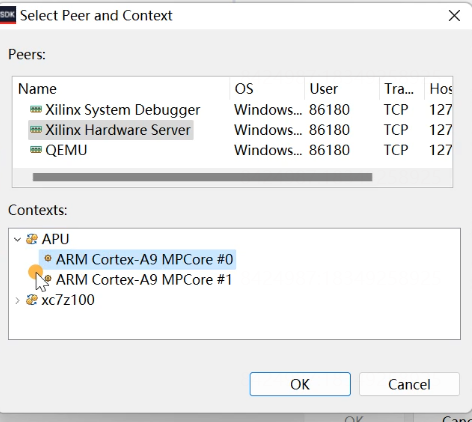

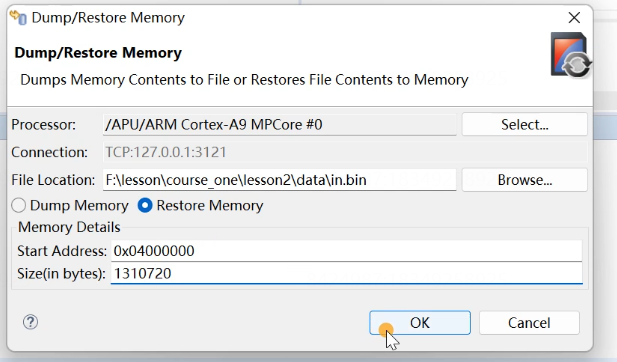

数据导入方法

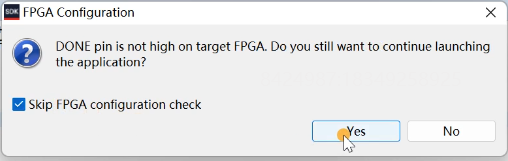

注意 应该在程序运行中再导入数据,而不是导入后再运行程序

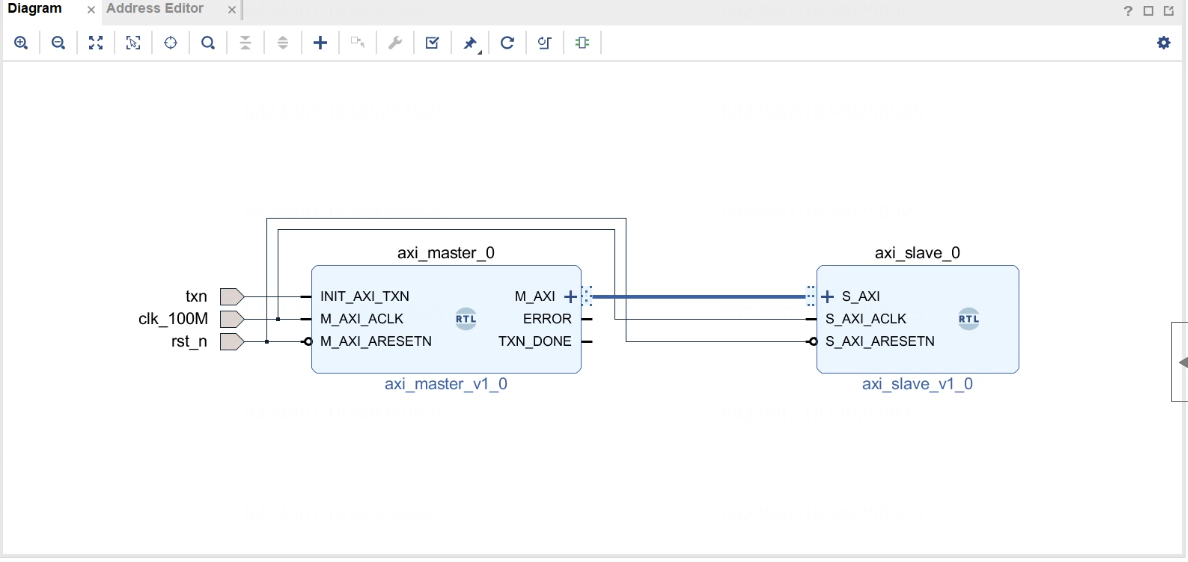

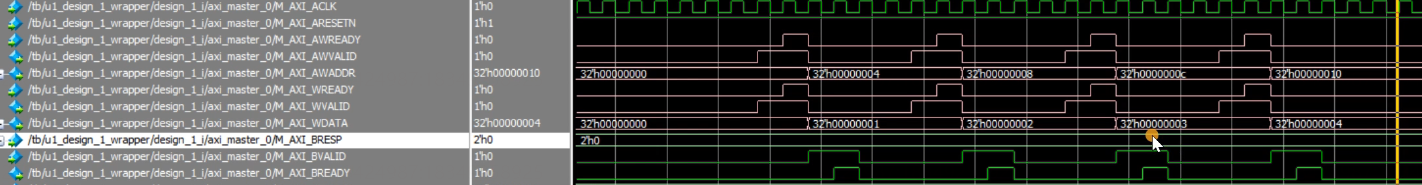

AXI_LITE仿真

写数据,写了四个数据,并且写响应正常,M_AXI_BRESP为slave输出的信号,0为没有错误,其中M_AXI_BVALID为slave输出的信号,M_AXI_BREADY为master输出的信号,M_AXI_BRESP为slave输出的信号,表明接收数据正常

读数据,读取四个数据,并且读响应正常,M_AXI_RRESP是slave输出的信号,0为没有错误

使用AXI_LITE MASTER配置寄存器代码修改示例

1 reg [7:0] cnt_axi_awaddr ; 2 3 always @(posedge M_AXI_ACLK) 4 5 if (M_AXI_ARESETN == 0 || init_txn_pulse == 1'b1) 6 cnt_axi_awaddr <= 'd0; 7 else if(cnt_axi_awaddr == C_M_TRANSACTIONS_NUM) 8 cnt_axi_awaddr <= 'd0; 9 else if(M_AXI_AWREADY && axi_awvalid) 10 cnt_axi_awaddr <= cnt_axi_awaddr + 1; 11 else 12 cnt_axi_awaddr <= cnt_axi_awaddr; 13 14 always @(*) 15 begin 16 case(cnt_axi_awaddr) 17 0: axi_awaddr = 'h030 ; 18 1: axi_awaddr = 'h0AC ; 19 2: axi_awaddr = 'h0B0 ; 20 3: axi_awaddr = 'h0B4 ; 21 4: axi_awaddr = 'h0A8 ; 22 5: axi_awaddr = 'h0A4 ; 23 6: axi_awaddr = 'h0A0 ; 24 25 7: axi_awaddr = 'h000 ; 26 8: axi_awaddr = 'h05c ; 27 9: axi_awaddr = 'h060 ; 28 10: axi_awaddr = 'h064 ; 29 11: axi_awaddr = 'h058 ; 30 12: axi_awaddr = 'h054 ; 31 13: axi_awaddr = 'h050 ; 32 33 default : axi_awaddr = 'h030 ; 34 endcase 35 end 36 37 reg [7:0] cnt_axi_wdata ; 38 39 always @(posedge M_AXI_ACLK) 40 41 if (M_AXI_ARESETN == 0 || init_txn_pulse == 1'b1) 42 cnt_axi_wdata <= 'd0; 43 else if(cnt_axi_wdata == C_M_TRANSACTIONS_NUM) 44 cnt_axi_wdata <= 'd0; 45 else if(M_AXI_WREADY && axi_wvalid) 46 cnt_axi_wdata <= cnt_axi_wdata + 1; 47 else 48 cnt_axi_wdata <= cnt_axi_wdata; 49 50 always @(*) 51 begin 52 case (cnt_axi_wdata) 53 0: axi_wdata = 'h108B ; 54 1: axi_wdata = addr0 ; 55 2: axi_wdata = addr1 ; 56 3: axi_wdata = addr2 ; 57 4: axi_wdata = IW*num ; 58 5: axi_wdata = IW*num ; 59 6: axi_wdata = IH ; 60 61 7: axi_wdata = 'h8B ; 62 8: axi_wdata = addr0 ; 63 9: axi_wdata = addr1 ; 64 10: axi_wdata = addr2 ; 65 11: axi_wdata = IW*num ; 66 12: axi_wdata = IW*num ; 67 13: axi_wdata = IH ; 68 default :axi_wdata <= 'h108B ; 69 endcase 70 end 71 72 reg [7:0] cnt_axi_araddr; 73 74 always @(posedge M_AXI_ACLK) 75 if (M_AXI_ARESETN == 0 || init_txn_pulse == 1'b1) 76 cnt_axi_araddr <= 'd0; 77 else if(cnt_axi_araddr==C_M_TRANSACTIONS_NUM) 78 cnt_axi_araddr <= 'd0; 79 else if (M_AXI_ARREADY && axi_arvalid ) 80 cnt_axi_araddr <= cnt_axi_araddr + 'd1; 81 else 82 cnt_axi_araddr <= cnt_axi_araddr; 83 84 always @(*) 85 begin 86 case (cnt_axi_araddr) 87 0: axi_araddr = 'h030 ; 88 1: axi_araddr = 'h0AC ; 89 2: axi_araddr = 'h0B0 ; 90 3: axi_araddr = 'h0B4 ; 91 4: axi_araddr = 'h0A8 ; 92 5: axi_araddr = 'h0A4 ; 93 6: axi_araddr = 'h0A0 ; 94 95 7: axi_araddr = 'h000 ; 96 8: axi_araddr = 'h05c ; 97 9: axi_araddr = 'h060 ; 98 10: axi_araddr = 'h064 ; 99 11: axi_araddr = 'h058 ; 100 12: axi_araddr = 'h054 ; 101 13: axi_araddr = 'h050 ; 102 103 default :axi_araddr <= 'h030; 104 endcase 105 end 106 107 108 109 110 //Address/Data Stimulus 111 112 //Address/data pairs for this example. The read and write values should 113 //match. 114 //Modify these as desired for different address patterns. 115 116 //Write Addresses 117 /* always @(posedge M_AXI_ACLK) 118 begin 119 if (M_AXI_ARESETN == 0 || init_txn_pulse == 1'b1) 120 begin 121 axi_awaddr <= 0; 122 end 123 // Signals a new write address/ write data is 124 // available by user logic 125 else if (M_AXI_AWREADY && axi_awvalid) 126 begin 127 axi_awaddr <= axi_awaddr + 32'h00000004; 128 129 end 130 end 131 132 // Write data generation 133 always @(posedge M_AXI_ACLK) 134 begin 135 if (M_AXI_ARESETN == 0 || init_txn_pulse == 1'b1 ) 136 begin 137 axi_wdata <= C_M_START_DATA_VALUE; 138 end 139 // Signals a new write address/ write data is 140 // available by user logic 141 else if (M_AXI_WREADY && axi_wvalid) 142 begin 143 axi_wdata <= C_M_START_DATA_VALUE + write_index; 144 end 145 end */ 146 147 //Read Addresses 148 /* always @(posedge M_AXI_ACLK) 149 begin 150 if (M_AXI_ARESETN == 0 || init_txn_pulse == 1'b1) 151 begin 152 axi_araddr <= 0; 153 end 154 // Signals a new write address/ write data is 155 // available by user logic 156 else if (M_AXI_ARREADY && axi_arvalid) 157 begin 158 axi_araddr <= axi_araddr + 32'h00000004; 159 end 160 end */

使用AXI_LITE SLAVE 使得 PS 与 PL互相通信示例

assign slv_reg_rden = axi_arready & S_AXI_ARVALID & ~axi_rvalid; always @(*) begin // Address decoding for reading registers case ( axi_araddr[ADDR_LSB+OPT_MEM_ADDR_BITS:ADDR_LSB] ) 6'h00 : reg_data_out <= in_data0; 6'h01 : reg_data_out <= in_data1; 6'h02 : reg_data_out <= in_data2; 6'h03 : reg_data_out <= in_data3; //PL 发数据给 PS always @( posedge S_AXI_ACLK ) if ( S_AXI_ARESETN == 1'b0 ) begin out_data0 <= 'd0; out_data1 <= 'd0; out_data2 <= 'd0; out_data3 <= 'd0; end else begin out_data0 <= slv_reg32 ; out_data1 <= slv_reg33 ; out_data2 <= slv_reg34 ; out_data3 <= slv_reg35 ; end //PS发数据给PL

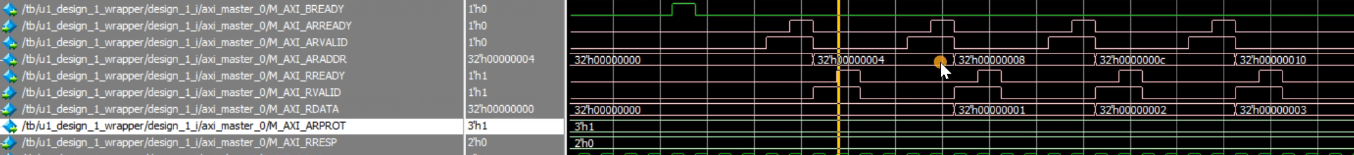

保存ZYNQ配置信息

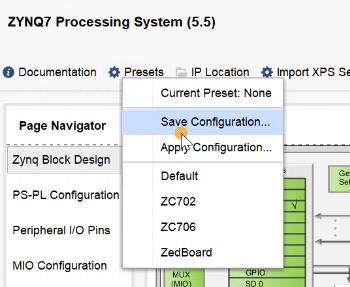

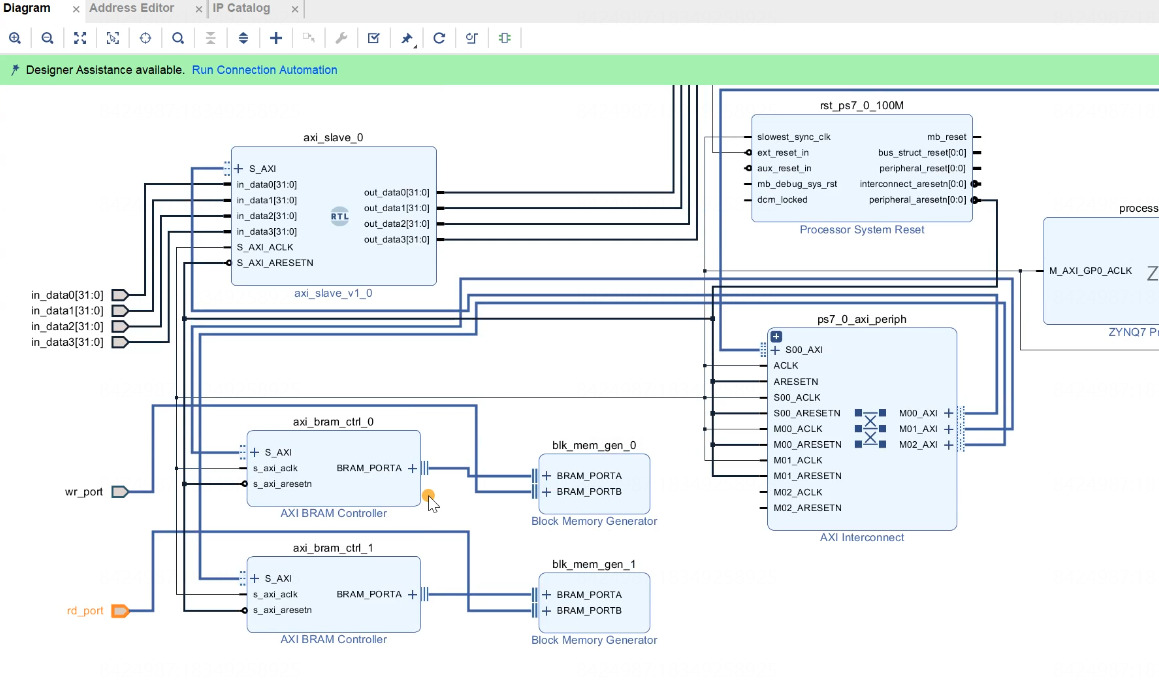

BRAM交互,关闭other options的 Enable Safety Circuit

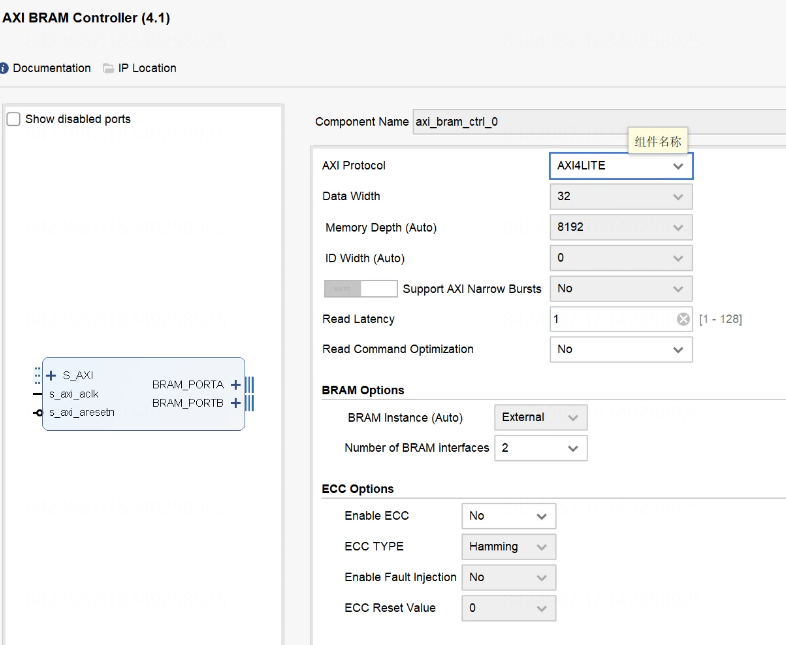

BRAM Controller设置

总体配置

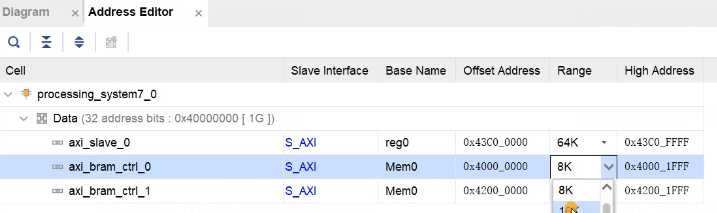

更改BRAM深度,需要在地址配置里更改

注意we信号,拉高表示写,拉低表示读

1 .wr_port_addr (wr_addr ), 2 .wr_port_clk (cpu_clk ), 3 .wr_port_din (wr_data ), 4 .wr_port_dout ( ), 5 .wr_port_en (1'b1 ), 6 .wr_port_rst (1'b0 ), 7 .wr_port_we ({4{wr_de}} ), 8 9 .rd_port_addr (rd_addr ), 10 .rd_port_clk (cpu_clk ), 11 .rd_port_din (32'd0 ), 12 .rd_port_dout (rd_data ), 13 .rd_port_en (1'b1 ), 14 .rd_port_rst (1'b0 ), 15 .rd_port_we (4'h0 ) 16 17 ); 18 19 always@(posedge cpu_clk) 20 wr_start_r <= wr_start; 21 22 always@(posedge cpu_clk) 23 rd_start_r <= rd_start; 24 25 reg wr_de = 0; 26 reg [31:0] wr_data = 0; 27 reg [31:0] wr_addr = 0; 28 29 always@(posedge cpu_clk) 30 if(wr_addr==8188) 31 wr_de <= 1'b0; 32 else if(~wr_start_r&&wr_start) 33 wr_de <= 1'b1; 34 else 35 wr_de <= wr_de; 36 37 always@(posedge cpu_clk) 38 if(wr_addr==8188) 39 wr_addr <= 'd0; 40 else if(wr_de==1'b1) 41 wr_addr <= wr_addr + 4; 42 else 43 wr_addr <= wr_addr; 44 45 always@(posedge cpu_clk) 46 if(wr_data==2047) 47 wr_data <= 'd0; 48 else if(wr_de==1'b1) 49 wr_data <= wr_data + 1'b1; 50 else 51 wr_data <= wr_data; 52 53 reg rd_de = 0; 54 wire[31:0] rd_data ; 55 reg [31:0] rd_addr = 0; 56 57 always@(posedge cpu_clk) 58 if(rd_addr==8188) 59 rd_de <= 1'b0; 60 else if(~rd_start_r&&rd_start) 61 rd_de <= 1'b1; 62 else 63 rd_de <= rd_de; 64 65 always@(posedge cpu_clk) 66 if(rd_addr==8188) 67 rd_addr <= 'd0; 68 else if(rd_de==1'b1) 69 rd_addr <= rd_addr + 4; 70 else 71 rd_addr <= rd_addr;

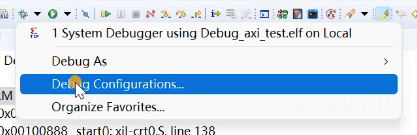

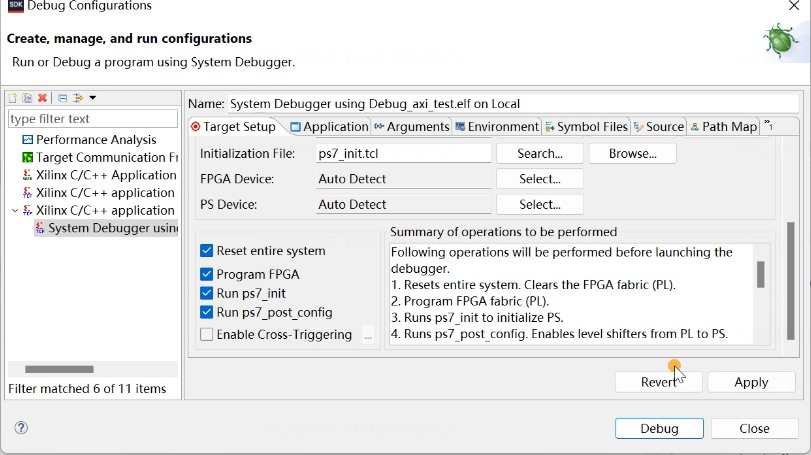

SDK使用技巧,怎么防止进入汇编语言

点击绿色三角

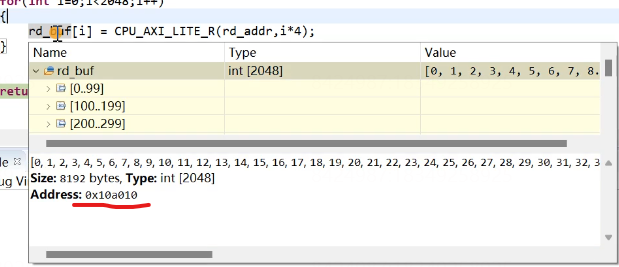

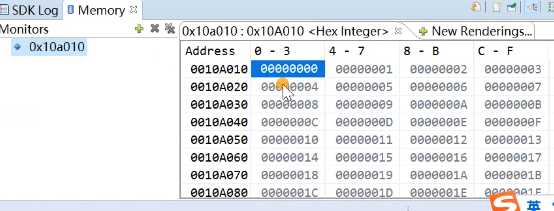

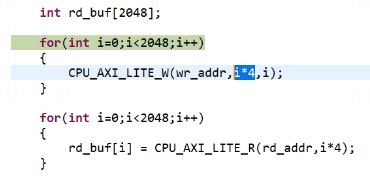

PS写入2048个数据

读取PS写入的数据,地址和数据存在一个时钟的延时

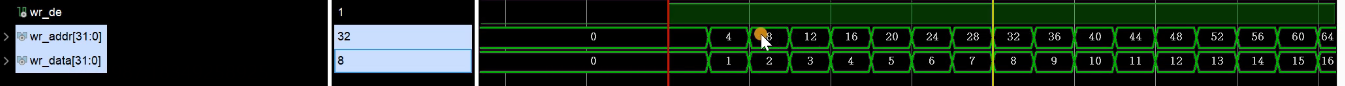

PL写入数据,地址和数据是对齐的

在PS端采集到了数据,注意Address 的地址是 0-3 4-7 8-B....实际下面显示的数据是从右到左 由小到大,和上面的地址是反着的