3W原则的实质以及20H原则最强整理

转载于: http://blog.csdn.net/times_poem/article/details/51839823

需求说明:Cadence基本知识

内容 :第一部分 PCB设计之3W原则

第二部分 PCB设计之3W原则与20H原则图示

第三部分 3W原则的实质详解

来自 :时间的诗

第一部分 PCB设计之3W原则

原文:http://www.mr-wu.cn/3w-rule-pcb-design/

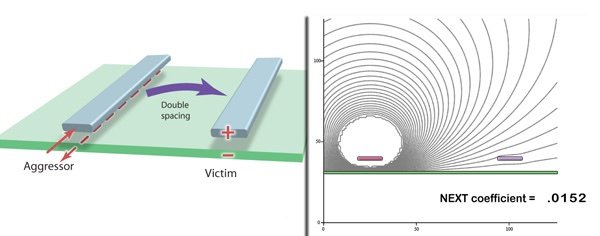

在PCB设计中为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持大部分电场不互相干扰,这就是3W规则。如下图所示。

满足3W原则能使信号间的串扰减少70%,而满足10W则能使信号间的串扰减少近98%.

3W原则虽然易记,但要强调一点,这个原则成立是有先前条件的。从串扰成因的物理意义考量,要有效防止串扰,该间距与叠层高度、导线线宽相关。对于四层板,走线与参考平面高度距离(5~10mils),3W是够了;但兩层板,走线与参考层高度距离(45~55mils),3W对高速信号走线可能不够。3W原则一般是在50欧姆特征阻抗传输线条件下成立。

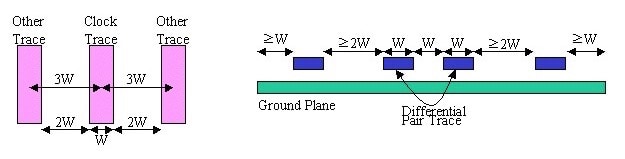

3W原则是指多个高速信号线长距离走线的时候,其间距应该遵循3W原则,例如时钟线,差分线,视频、音频信号线,复位信号线及其他系统关键电路需要遵循3W原则,而并不是板上所有的布线都要强制符合3W原则。

第二部分 PCB设计之3W原则与20H原则图示

3w就是两条线的间距是线宽的两倍 。

20H是电源层内缩地层20H , H表示电源层与地层的距离。

3W规则:

为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持70%的电场不互相干扰,称为3W规则。如要达到98%的电场不互相干扰,可使用10W的间距。

画电脑主板用3W原则比较多,南桥北桥芯片出来的线用5mil,间距用10mil,通俗的说:就是走5隔10。.

20H规则:

由于电源层与地层之间的电场是变化的,在板的边缘会向外辐射电磁干扰。称为边沿效应。

解决的办法是将电源层内缩,使得电场只在接地层的范围内传导。以一个H(电源和地之间的介质厚度)为单位,若内缩20H则可以将70%的电场限制在接地层边沿内;内缩100H则可以将98%的电场限制在内。要求地平面大于电源或信号层,这样有利于防止对外辐射干扰和屏蔽外界对自身的干扰。电源层比地层内缩1mm基本上就可以。

第三部分 3W原则的实质详解

原文:http://blog.sina.com.cn/s/blog_56d7464c0100zipt.html

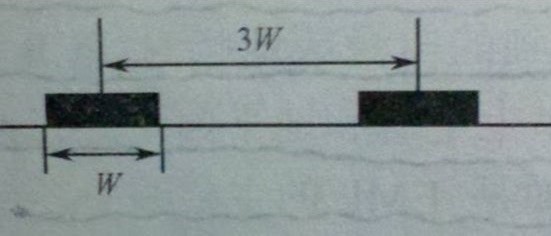

3W原则是一种设计者无须其他设计技术就可以遵守PCB布局的原则。但这种设计方法占用了很多面积,可能会使布线更加困难。使用3W原则的基本出发点是使走线间的耦合最小。这种原则可表示为:走线的距离间隔(走线中心间的距离)必须是单一走线宽度的三倍。另一种表示是:两个走线的距离间隔必须大于单一走线宽度的二倍。比如,时钟线为6mil宽,则其他走线只能在距这条走线2×6mil以外的地方布线,或者保证边到边的距离大于12mil。图7-25是使用3W原则的实例。

注意:3W原则代表的是逻辑电流中近似70%的通量边界,要想得到98%边界的近似,应该用10W原则。

【注】3W原则是一种防止串扰的一种方法,该方法仅作为一种参考,并作为理解如何防止串扰的一种启发。实际PCB设计中,3W原则并不能完全满足避免串扰的要求。按实践经验,如果没有屏蔽地线的话,印制信号线之间大于lcm以上的距离才能很好地防止串扰,因此在PCB线路布线时,就需要在噪声源信号(如时钟走线)与非噪声源信号线之间,及受EFTlB、ESD等干扰的“脏“线与需要保护的“干净”线之间,不但要强制使用3W原则,而且还要进行屏蔽地线包地处理,以防止串扰的发生。另外,不是所有的PCB上的走线都必须遵照3W布线原则。使用这一设计指导原则,在PCB布线前,决定哪些条走线必须使用3W原则是十分重要的。

两条走线中间的印制线3有一个过孔。这个过孔通常与第三条走线相连,这条走线中可能通过一个易产生电磁破坏的信号。例如,复位线、音频或视频走线、模拟电乎控制走线或者I/O接口线等,它将以电感或电容的形式感受额外的电磁能量干扰。为最小化走线对过孔的串扰,相邻走线的距离间隔必须包括过孔直径和间隙间隔,如图7-25中所描述的那样,距离时钟线的2W范围内没有其他信号过孑L。对富含RF能量的走线的距离间隔也有同样的要求,这种走线上的能量可能会耦合到元件的引脚(管脚外露)上。

3W原则的使用不只局限于时钟或周期信号走线,差分对(平衡的、ECL及类似敏感走线)也是3W主要的代表。对差分走线来说,走线对间的距离应为1W。电源层噪声和单端信号可能通过容性或感性耦合进差分对的走线。如果那些与差分对无关的走线的物理间隔不到3W,则干扰可能会引起数据的破坏。图7-26为在一个PCB结构中差分财走线布线的例子。

除上述技术之外,为在PCB中避免串扰,也应从PCB设计和布局方面来考虑,例如:

(1)根据功能分类逻辑器件系列,保持总线结构被严格控制。

(2)最小化元器件之间的物理距离。

(3)高速信号线及元器件(如晶振)要远离I/()互连接口及其他易受数据干扰及耦合

影响的区域。

(4)对高速线提供正确的终端。

(5)避免长距离互相平行的走线布线,提供走线间足够的间隔以最小化电感耦合。

(6)相临层(微带或带状线)上的布线要互相垂直,以防止层间的电容耦合。

(7)降低信号到地平面的距离间隔。

(8)分割和隔离高噪声发射源(时钟、I/O、高速互连),不同的信号分布在不同的层中。

(9)尽可能地增大信号线间的距离,这可以有效地减少容性串扰。

(10)降低引线电感,避免电路使用具有非常高阻抗的负载和非常低阻抗的负载,尽量使模拟电路负载阻抗稳定在loQ~lokQ之间。因为高阻抗的负载将增加容性串扰,在使用非常高阻抗负载的时候,由于工作电压较高,导致容性串扰增大,而在使用非常低阻抗负载的时候,由于工作电流很大,感性串扰将增加。

(11)将高速周期信号布置在PCB酌内层。

(12)使用阻抗匹配技术,以保BT证信号完整性,防止过冲。

(13)注意对具有快速上升沿(tr≤3ns)的信号,进行包地等防串扰处理,将一些受EFTlB或ESD干扰且未经滤波处理的信号线布置在PCB的边缘。

(14)尽量采用地平面,使用地平面的信号线相对于不使用地平面的信号线来说将获得15~20dB的衰减。

(15)信号高频信号和敏感信号进行包地处理,双面板中使用包地技术将获得10~15dB

的衰减。

(16)使用平衡线,屏蔽线或同轴线。

(17)对骚扰信号线和敏感线进行滤波处理。

(18)合理设置层和布线,合理设置布线层和布线间距,减小并行信号长度,缩短信号层与平面层的间距,增大信号线间距,减小并行信号线长度(在关键长度范围内),这些措施都可以有效减小串扰。

浙公网安备 33010602011771号

浙公网安备 33010602011771号