存储器MEM

1.概述(What)

存储器用来存储指令和数据。因为计算机是人类告诉机器一系列的操作步骤去解决问题,那么这一系列的操作步骤需要保存在某个地方,然后CPU去读操作步骤来执行操作,解决问题。那么存储这些步骤的地方就是存储器。

2.演进(Why)

如何能够经济,速度,规模的存取操作步骤这个问题?那么存储器是个三维的评价体系:速度,容量,每位价格。一般来说速度越高,位价格就越高;容量越大,位价位就越低,而且容量越大,速度必定越低。所以这三者的矛盾,构成了缓存、主存、辅存三级存储系统。

提高效率,一般是两种方法,一种是更换更快的组件,这种是不更改系统架构,而在同一层面的解决方法;第二种是调整架构,重新组合每个部分,达到更高要求。这是从更高层面去解决问题。

3.组成结构(How)

3.1 主存储器

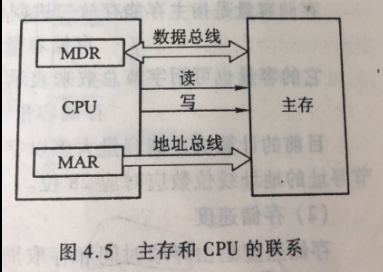

- 当要从存储器读取某一信息字时,首先由CPU将该字的地址送到MAR,经地址总线送至主存,然后发出读命令。主存接到读命令后,将该地址单元的内容读出,送到数据总线上,再存储到MDR中。

- 向主存写入一个信息字时,首先由CPU将该字所在主存单元地址经MAR送到地址总线上,并将信息字送入到MDR,然后向主存发出写命令,主存接到写命令后,将数据总线上的信息写入到指定地址的主存单元中。

注意:总线通信逻辑可参考总线一章中的同步通信时序。当然实际计算机我不知道是不是这么通信的,但是同步通信方式可以实现这个流程。

3.2 高速缓冲存储器

3.2.1 基本框架

- Why

(1)CPU速度越来越快,而主存速度提高有限,需要更快的存储设备。

(2)IO和CPU竞争主存。可将部分信息提前放入CPU,缓解竞争。 - How

(1)程序运行存在局部性特点,即在某一小段时间内,CPU读取指令和数据会相对的簇聚。

(2)将内存的字节数组分成小块,每次从内存读取小块放入缓存中,有很大几率CPU下次读取数据时,可以直接从缓存拿到数据。 - What

![]()

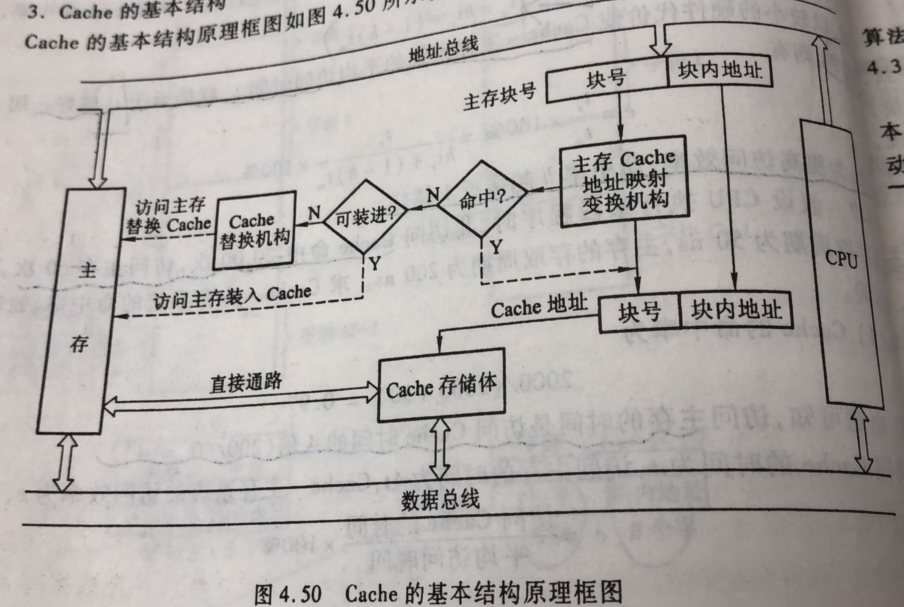

- Cache存储体,以块为单位与主存交换数据

- 地址映射变换机构,将主存地址转换为Cache地址

- 替换机构,将Cache内的块按照一定算法替换

以前CPU直接访问主存,现在储存结构分层了,对CPU透明。首先将内存地址替换为缓存地址,判断缓存是否有请求数据。有就直接返回缓存数据,没有就访问内存。

3.2.2 细节

这里再深入Cache的细节。

- Cache架构的改进

一是增加Cache的级数,从一级缓存增加到二级、三级缓存。

二是从统一缓存分立为多个缓存,将指令和数据分开存储。 - 地址映射的多个方案

(1)直接映射,每个缓存块对应固定位置的主存块,缺点是命中率不高

(2)全相联映射,每个缓存快对应任意位置的主存块,缺点是逻辑电路复杂成本较高

(3)组相联映射,将Cache块分组,每组有N块,主存块可以分配到某一组的任意块,成本比较均衡 - 替换策略

先进先出,LRU,随机

第一个是架构改进,第二第三是优化组件方式。

3.3辅助存储器

3.3.1 磁盘

- What

磁盘由磁盘驱动器,磁盘控制器和盘片三个部分组成。 - How

(1)磁盘驱动器主要负责磁头的位置移动,以及磁场与电信号的转换。

(2)磁盘控制器作用是接收主机发来的命令,将它转换成为磁盘驱动器的控制命令,实现指令与磁头之间的数据转换。

浙公网安备 33010602011771号

浙公网安备 33010602011771号