系统架构师:计算机组成与体系结构

1. CISC 复杂指令集计算机 和 RISC 精简指令集计算机 的特点:

CISC:指令数量众多;指令使用频率相差悬殊;支持很多种寻址方式;变长的指令;指令可以对主存单元中的数据直接进行处理;以微程序控制为主。

RISC:指令数量少;指令的寻址方式少;指令长度固定、指令格式种类少;以硬布线逻辑控制为主;单周期指令执行、采用流水线技术;优化的编译器;CPU通用寄存器数量多。

--------------------------------------------------------------------------------------------------------------------------------------

2. 流水线

流水线周期:流水线处理工作中最耗时的阶段所消耗的时间。

1)执行时间

1条指令取指2ms、分析4ms、执行1ms,执行100条指令需要多长时间?

理论公式:Nt+(k-1)t ==> 2+4+1+(100-1)*4=403ms

实际公式:考虑到处理的复杂性,会将指令的每个执行阶段的时间统一为流水线周期,即 4+4+4+(100-1)*4=408

2)吞吐率 Though Put rate ,TP

概念:在单位时间内流水线所 完成的任务数量 或 输出结果的数量 。

公式:指令条数/流水线执行时间

最大吞吐率:即指令条数趋向无穷大时的吞吐率。

3)加速比

公式:不用流水线的执行时间/使用流水线的执行时间

--------------------------------------------------------------------------------------------------------------------------------------

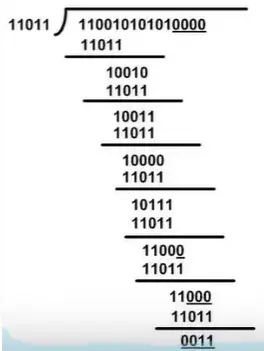

3. CRC校验码计算

原始报文:11001010101

生成多项式:X^4+ X^3+X+1 ==> 11011

CRC编码结果:异或运算 110010101010011

--------------------------------------------------------------------------------------------------------------------------------------

4. 移臂调度算法

某磁盘200个柱面,访问143号柱面后接着访问125号柱面,等待服务的柱面号为:86、147、91、177、94、150、102、175、130

1)先来先服务算法:根据访问请求的先后次序来决定执行次序。125、86、147、91、177、94、150、102、175、130

2)最短寻找时间优先调度算法:从等待访问者中挑选寻找时间最短的执行。125、130、147、150、175、177、102、94、91、86

3)电梯调度算法:从当前移动方向选择最近的柱面执行,该方向无请求时,改变移动方向再选择。125、102、94、91、86、130、147、150、175、177

4)单向扫描调度算法:由当前位置从小到大排列,再将剩下的由小到大排。125、130、147、150、175、177、86、91、94、102

--------------------------------------------------------------------------------------------------------------------------------------

5. 总线

一组为多个部件分时共享的信息传送线

通过总线复用可以减少总线中信号线的数量

分类:

- 数据总线:双向,在CPU与RAM之间来回传送数据

- 地址总线:单向,指定在RAM中存储的数据地址

- 控制总线:微处理器控制单元的信号传递到周边设备

按数据传输方式划分:

并行总线

串行总线

数据是一位一位传输的,每一位占一个固定时间长度。

串行总线适宜长距离传输数据。但串行总线有半双工、全双工之分,全双工是一条线发一条线收,可在两个方向上同时传输数据。半双工只能在两个方向轮流传输数据。

串行总线传输的波特率在使用中可以改变。

串行总线的数据发送和接收可以使用多种方式,程序查询方式和中断方式都可以。

--------------------------------------------------------------------------------------------------------------------------------------

6.嵌入式硬件

1. SoC System on Chip

全称:系统级芯片(片上系统)

定义:它是一个产品,一个专用目标的集成电路。包含完整系统并有嵌入软件。

同时也是一种技术,用以实现从确定系统功能开始,到软/硬件划分,并完成设计的整个过程。

从狭义角度讲,它是信息系统核心的芯片集成,是将系统关键部件集成在一块芯片上;

从广义角度讲, SoC是一个微小型系统,如果说中央处理器(CPU)是大脑,那么SoC就是包括大脑、心脏、眼睛和手的系统。

国内外学术界一般倾向将SoC定义为将微处理器、模拟IP核、数字IP核和存储器(或片外存储控制接口)集成在单一芯片上,它通常是客户定制的,或是面向特定用途的标准产品。

优点:实现了软硬件无缝结合,直接在微处理片内嵌入操作系统代码模块。减小了系统体积和功耗,提高了可靠性和生产效率。

2. AI芯片的特点:新型的计算范式、训练和推断、大数据处理能力、数据精度、可重构的能力、开发工具。

3. DSP芯片:专门用于信号处理

- 哈佛结构:指令与数据分开存储,可以并行读取,数据吞吐率高

- 4条总线:指令和数据的数据总线,地址总线

- 流水线:采用2-6级流水线以减少指令执行时间,使指令执行能完全重叠,在每个指令周期内,不同的指令都处于激活状态。

- 独立的硬件乘法器:DSP芯片有一个专用的硬件乘法器,乘法可以在一个周期内完成。

- 特殊的DSP指令:专为数字信号处理中的一些常用算法优化。这些特殊指令为一些典型的数字处理提供加速,可以大幅提高处理器的执行效率。

- 独立的DMA总线和控制器:有一组或多组DMA总线,与CPU程序、数据总线并行工作。在不影响CPU工作的条件下,DMA的速度已经达到800MB/S以上。这在需要大数据量进行交换的场合可以减小CPU的开销,提高数据的吞吐率。提高系统的并行执行能力。

- 多处理器接口:使多个处理器可以很方便地并行或串行工作以提高处理速度。

- JTAG标准测试接口:便于对DSP做片上的在线仿真和多DSP条件下的调试。

- 快速的指令周期:10ns以内。

4. EMPU 微处理器 (单板机)

仅保留和嵌入式应用紧密相关的功能硬件。

5. MCU 微控制器 (单片机)

片上外设资源丰富,适合用于控制

冯诺依曼结构(普林斯顿结构):一般用于PC;指令与数据合并在一起;指令与数据都通过相同数据总线传输

嵌入式实时系统调度算法

- 优先级调度算法:系统分配相对固定的优先顺序

- 抢占式优先级调度算法:根据紧急程度确定优先级

- 最早截止期调度算法(EDF算法):根据截止时间确定优先级

- 最晚截止期调度算法

--------------------------------------------------------------------------------------------------------------------------------------

7. CPU的工作频率(主频)= 外频(系统总线频率) * 倍频

--------------------------------------------------------------------------------------------------------------------------------------

8.性能评价

--------------------------------------------------------------------------------------------------------------------------------------

浙公网安备 33010602011771号

浙公网安备 33010602011771号