ibert测试说明

xilinx对于高速收发接口gth有专门的验证方案ibert,FPGA的引脚按bank划分,gth类似不过是按Quad来算,每个Quad的结构如下:

一共有4组收发对。每个Qual和管脚的位置都是绑定的,所以在例化ip核时只要指定Quad的位置即可,不需要再对管脚做约束了。

以UV440为例:可以整理出对应的位置表格

| BANK | lane0 | lane1 | lane2 | lane3 |

| Bank229 | X0Y40 | X0Y41 | X0Y42 | X0Y43 |

| Bank230 | X0Y44 | X0Y45 | X0Y46 | X0Y47 |

| Bank231 | X0Y48 | X0Y49 | X0Y50 | X0Y51 |

| Bank232 | X0Y52 | X0Y53 | X0Y54 | X0Y55 |

| Bank219 | X0Y0 | X0Y1 | X0Y2 | X0Y3 |

| Bank220 | X0Y4 | X0Y5 | X0Y6 | X0Y7 |

| Bank221 | X0Y8 | X0Y9 | X0Y10 | X0Y11 |

| Bank224 | X0Y20 | X0Y21 | X0Y22 | X0Y23 |

| Bank225 | X0Y24 | X0Y25 | X0Y26 | X0Y27 |

| Bank226 | X0Y28 | X0Y29 | X0Y30 | X0Y31 |

| Bank227 | X0Y32 | X0Y33 | X0Y34 | X0Y35 |

Ibert配置介绍:

新建一个临时Temp工程:芯片选择

![]()

在ip Catalog搜索ibert:

根据连接进行配置GTH的选项:

选择一个系统使用,一般选择板卡上的一个全局时钟即可:

生成Example:

会在指定目录生成一个新的示例工程:

直接点生成bit即可:

板卡上电,设置对应的时钟频率,(此例中:参考时钟及系统时钟)下载bit到FPGA,

使用FPGA vivado扫描Hardware,

set xil_newLinks [list]

set xil_newLink [create_hw_sio_link -description {Link 1} [lindex [get_hw_sio_txs localhost:3121/xilinx_tcf/Digilent/210251AC2FD0/0_1_0_1/IBERT/Quad_227/MGT_X0Y32/TX] 0] [lindex [get_hw_sio_rxs localhost:3121/xilinx_tcf/Digilent/210251AC2FD0/2_1_0_1/IBERT/Quad_224/MGT_X0Y20/RX] 0] ]

lappend xil_newLinks $xil_newLink

set xil_newLink [create_hw_sio_link -description {Link 2} [lindex [get_hw_sio_txs localhost:3121/xilinx_tcf/Digilent/210251AC2FD0/0_1_0_1/IBERT/Quad_227/MGT_X0Y33/TX] 0] [lindex [get_hw_sio_rxs localhost:3121/xilinx_tcf/Digilent/210251AC2FD0/2_1_0_1/IBERT/Quad_224/MGT_X0Y21/RX] 0] ]

lappend xil_newLinks $xil_newLink

set xil_newLink [create_hw_sio_link -description {Link 3} [lindex [get_hw_sio_txs localhost:3121/xilinx_tcf/Digilent/210251AC2FD0/0_1_0_1/IBERT/Quad_227/MGT_X0Y34/TX] 0] [lindex [get_hw_sio_rxs localhost:3121/xilinx_tcf/Digilent/210251AC2FD0/2_1_0_1/IBERT/Quad_224/MGT_X0Y22/RX] 0] ]

lappend xil_newLinks $xil_newLink

set xil_newLink [create_hw_sio_link -description {Link 4} [lindex [get_hw_sio_txs localhost:3121/xilinx_tcf/Digilent/210251AC2FD0/0_1_0_1/IBERT/Quad_227/MGT_X0Y35/TX] 0] [lindex [get_hw_sio_rxs localhost:3121/xilinx_tcf/Digilent/210251AC2FD0/2_1_0_1/IBERT/Quad_224/MGT_X0Y23/RX] 0] ]

lappend xil_newLinks $xil_newLink

set xil_newLink [create_hw_sio_link -description {Link 5} [lindex [get_hw_sio_txs localhost:3121/xilinx_tcf/Digilent/210251AC2FD0/2_1_0_1/IBERT/Quad_224/MGT_X0Y20/TX] 0] [lindex [get_hw_sio_rxs localhost:3121/xilinx_tcf/Digilent/210251AC2FD0/0_1_0_1/IBERT/Quad_227/MGT_X0Y32/RX] 0] ]

lappend xil_newLinks $xil_newLink

set xil_newLink [create_hw_sio_link -description {Link 6} [lindex [get_hw_sio_txs localhost:3121/xilinx_tcf/Digilent/210251AC2FD0/2_1_0_1/IBERT/Quad_224/MGT_X0Y21/TX] 0] [lindex [get_hw_sio_rxs localhost:3121/xilinx_tcf/Digilent/210251AC2FD0/0_1_0_1/IBERT/Quad_227/MGT_X0Y33/RX] 0] ]

lappend xil_newLinks $xil_newLink

set xil_newLink [create_hw_sio_link -description {Link 7} [lindex [get_hw_sio_txs localhost:3121/xilinx_tcf/Digilent/210251AC2FD0/2_1_0_1/IBERT/Quad_224/MGT_X0Y22/TX] 0] [lindex [get_hw_sio_rxs localhost:3121/xilinx_tcf/Digilent/210251AC2FD0/0_1_0_1/IBERT/Quad_227/MGT_X0Y34/RX] 0] ]

lappend xil_newLinks $xil_newLink

set xil_newLink [create_hw_sio_link -description {Link 8} [lindex [get_hw_sio_txs localhost:3121/xilinx_tcf/Digilent/210251AC2FD0/2_1_0_1/IBERT/Quad_224/MGT_X0Y23/TX] 0] [lindex [get_hw_sio_rxs localhost:3121/xilinx_tcf/Digilent/210251AC2FD0/0_1_0_1/IBERT/Quad_227/MGT_X0Y35/RX] 0] ]

lappend xil_newLinks $xil_newLink

set xil_newLinkGroup [create_hw_sio_linkgroup -description {Link Group 0} [get_hw_sio_links $xil_newLinks]]

unset xil_newLinks

……

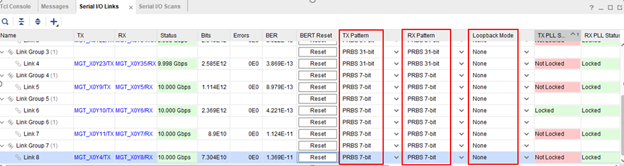

再手动添加link,link有时需要刷新(先切换到近端或远端,这些是自环选项,就是tx和rx在FPGA内部已经连接在一起了,再切换到none:外部连接的方式)才能正确显示成绿色(添加及刷新link可以在Tcl Console看到对应的脚本,这个脚本可以保存成文件,方便下次操作)。

看link时首先看PLL,PLL若没有锁住一般是频率设置不对,需要检查频率设置,PLL锁住后一般link都没有问题,只要link的rx能收到数据,不管是哪个quad的哪路tx lane发送的,都会正常显示绿色(应该是因为每个lane的伪随机数序列都是一样的),serdes的收发两端是不一定需要同源时钟的(只要数据lane对接上即可),非同源时钟只要收发两端的频率精度控制在一定范围即可,时钟是通过CDR电路从数据中恢复出来的。

双击ip核,点击Documentation->Product Guide可以看到ibert的使用说明文档。

浙公网安备 33010602011771号

浙公网安备 33010602011771号