2. UVM -- phase机制与UVM验证平台的运行

2. UVM -- phase机制与UVM验证平台的运行

2.1. UVM phase机制

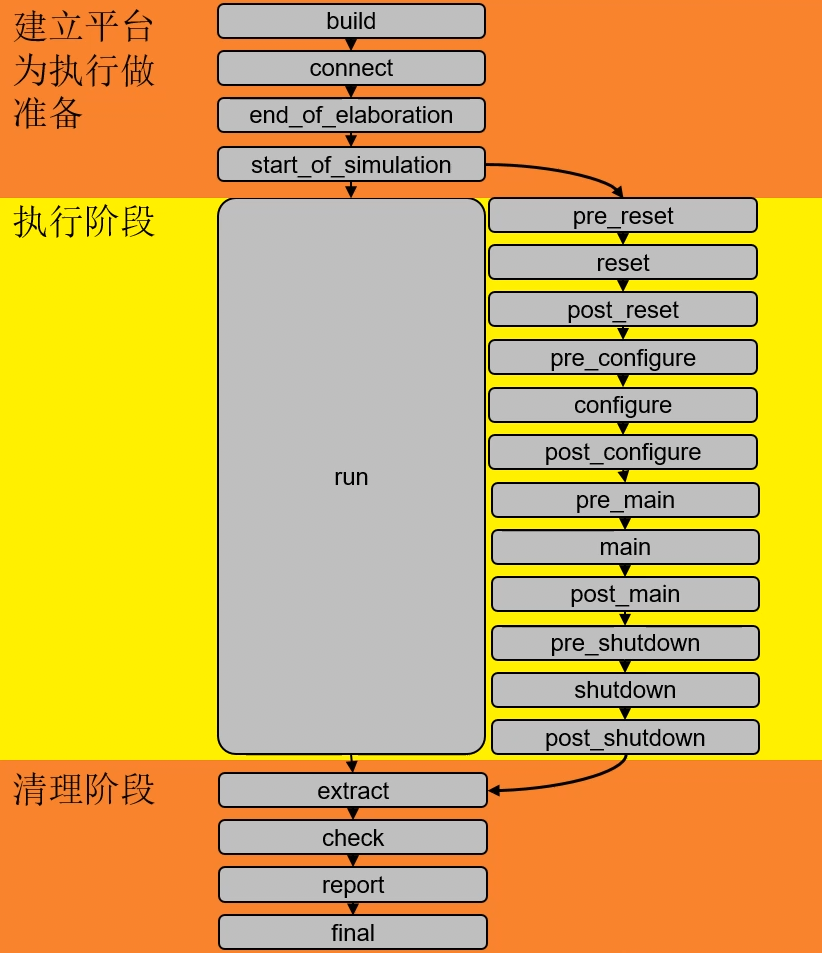

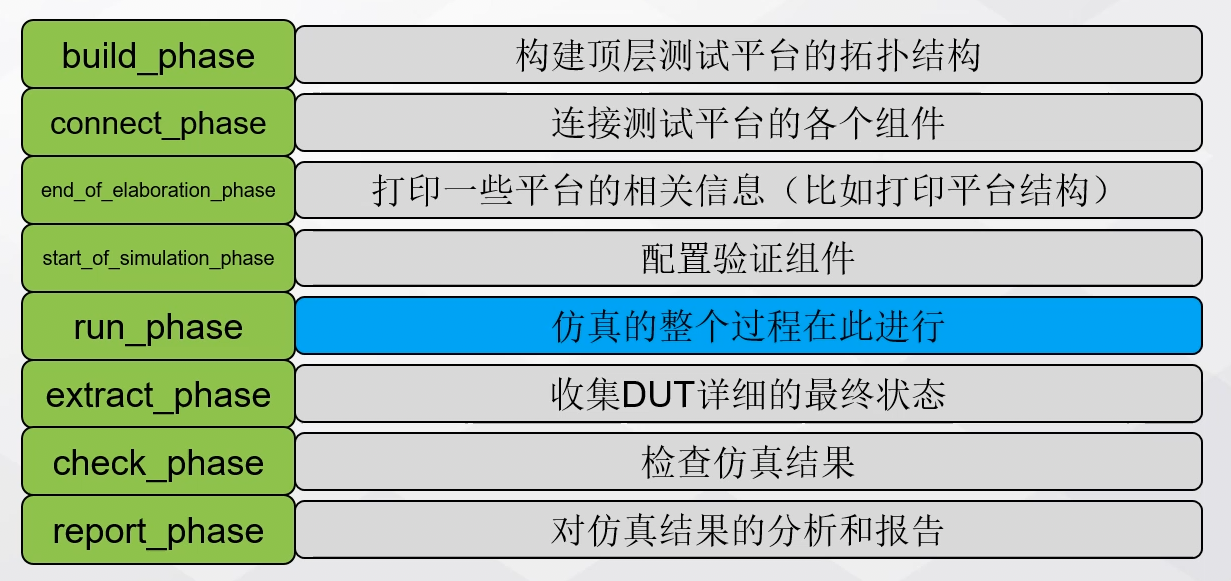

phase机制可以将 UVM仿真阶段 层次化,即 使各个phase按先后顺序执行,同时也使处于同一phase中的层次化组件之间按顺序执行 ,达到同步仿真过程的效果。

phase机制主要包括以下三个主要部分,并按如下顺序进行:

- Build Phases —— 验证平台的

创建、连接、配置;包含3个子phase; - Run Phases ——

产生激励并运行仿真,该阶段会消耗时间; 包含12个子phase 和 - start_of_simulation phase; - Clean up Phases —— 测试用例结果的收集与报告 ; 包含4个子phase;

2.2. UVM验证平台的启动及执行流程

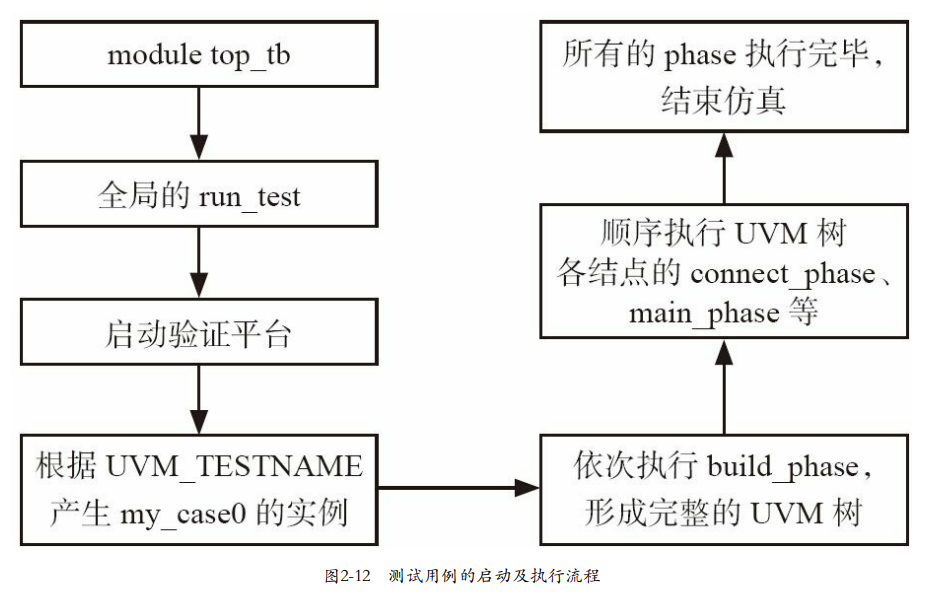

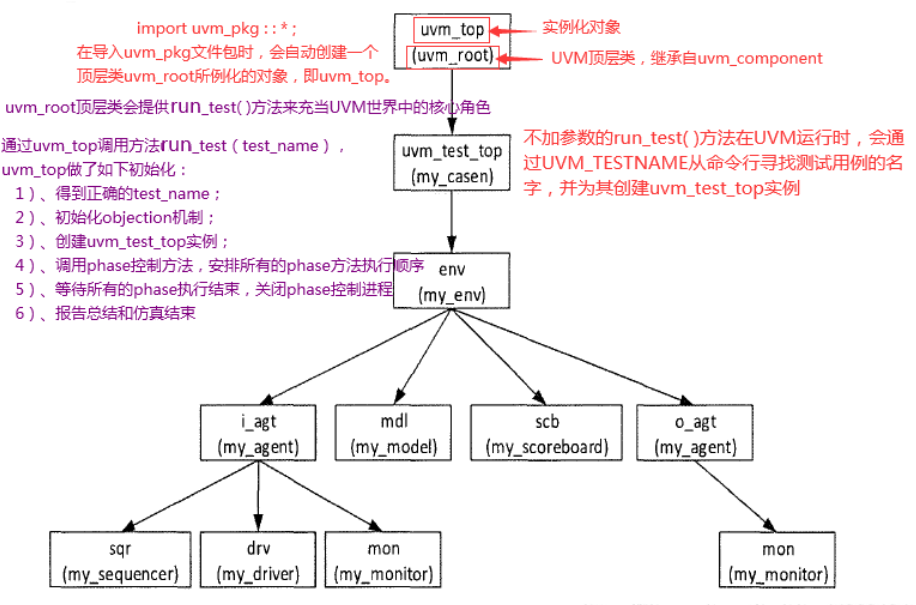

- UVM 平台会自动调用test_top中的run_test语句,创建一个my_case0的实例;

- UVM 依次执行build_phase、connect_phase:test_case内例化有平台env,env内又例化agent, agent内又例化了driver、monitor、sequencer等,这样就形成完整验证平台UVM树;

- UVM会根据 objection 机制来安排所有组件phase执行顺序,UVM会检查是否有objection被提起(raise_objection),如果有,那么会继续这个objection run_phase 直到仿真结束;如果没有,则马上结束当前phase。

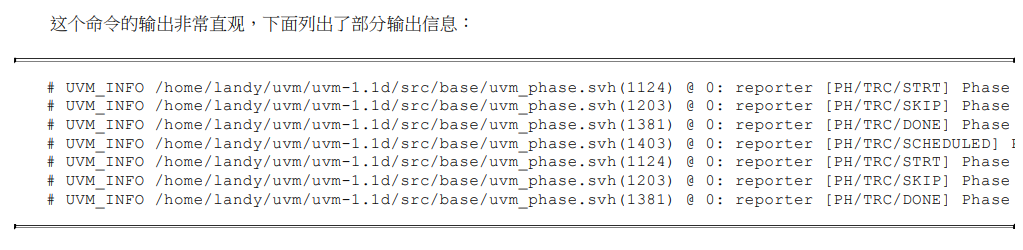

2.3. phase的调试

<sim command> +UVM_PHASE_TRACE

2.4. demo -- 平台的运行

平台的启动:自动调用test_top中的run_test

- test_top.sv

//-----------------------------------------------

//-- test_top

//-- Version : V0.1

//-- Wesley 2022.04.10

//-----------------------------------------------

module test_top;

import uvm_pkg::*;

`include "uvm_macros.svh"

import wesley_test_pkg::*;

logic clk = 0;

logic reset_n = 0;

//interface

wesley_intf MY0( .clk(clk), .reset_n(reset_n));

// DUT - a 16550 UART:

uart_16550 DUT ();

// clock/reset

always #5ns clk = ~clk;

initial begin

clk = 0;

reset_n = 0;

repeat(10) @(posedge clk);

reset_n = 1;

`uvm_info (" TEST_TOP ", $sformatf("clk = 0x%h , resetn = 0x%h", clk, reset_n), UVM_MEDIUM)

//repeat(1000) @(posedge clk);

//$finish;

end

// UVM virtual interface handling and run_test()

initial begin

// run

run_test();

end

endmodule: test_top

- test_case.sv

//-----------------------------------------------

//-- wesley_base_test

//-- Version : V0.1

//-- Wesley 2022.04.10

//-----------------------------------------------

`ifndef wesley_base_test__SV

`define wesley_base_test__SV

class wesley_base_test extends uvm_test;

`uvm_component_utils(wesley_base_test)

extern function new(string name = "wesley_base_test", uvm_component parent = null);

extern function void build_phase(uvm_phase phase);

extern function void end_of_elaboration_phase(uvm_phase phase);

extern virtual task run_phase(uvm_phase phase);

extern function void report_phase(uvm_phase phase);

extern function void final_phase(uvm_phase phase);

endclass: wesley_base_test

function wesley_base_test::new(string name = "wesley_base_test", uvm_component parent = null);

super.new(name, parent);

`uvm_info(get_type_name(), "< 000 > : new ", UVM_DEBUG)

endfunction: new

function void wesley_base_test::build_phase(uvm_phase phase);

super.build_phase(phase);

`uvm_info(get_type_name(), "< 001 > : build_phase ", UVM_DEBUG)

endfunction: build_phase

function void wesley_base_test::end_of_elaboration_phase(uvm_phase phase);

uvm_top.print_topology;

`uvm_info(get_type_name(), "< 003 > : end_of_elaboration_phase ", UVM_DEBUG)

endfunction: end_of_elaboration_phase

task wesley_base_test::run_phase(uvm_phase phase);

super.run_phase(phase);

`uvm_info(get_type_name(), "< 005 > : run_phase ", UVM_DEBUG)

phase.raise_objection(this);

`uvm_info(get_type_name(), "< 005 > : run_phase ", UVM_DEBUG)

phase.get_objection().set_drain_time(this, 1000);

phase.drop_objection(this);

endtask: run_phase

function void wesley_base_test::report_phase(uvm_phase phase);

`uvm_info(get_type_name(), "< 008 > : report_phase ", UVM_DEBUG)

endfunction: report_phase

function void wesley_base_test::final_phase(uvm_phase phase);

`uvm_info(get_type_name(), "< 009 > : final_phase ", UVM_DEBUG)

endfunction: final_phase

`endif // wesley_base_test__SV

- log:

ucli% run

UVM_INFO @ 0: reporter [RNTST] Running test wesley_base_test...

UVM_INFO /usr/synopsys/vc_static-O-2018.09-SP2-2/vcs-mx/etc/uvm-1.2/base/uvm_phase.svh(1349) @ 0: reporter [PH/TRC/STRT] Phase 'common' (id=188) Starting phase

UVM_INFO /usr/synopsys/vc_static-O-2018.09-SP2-2/vcs-mx/etc/uvm-1.2/base/uvm_phase.svh(1624) @ 0: reporter [PH/TRC/DONE] Phase 'common' (id=188) Completed phase

UVM_INFO /usr/synopsys/vc_static-O-2018.09-SP2-2/vcs-mx/etc/uvm-1.2/base/uvm_phase.svh(1659) @ 0: reporter [PH/TRC/SCHEDULED] Phase 'common.build' (id=191) Scheduled from phase common

UVM_INFO /usr/synopsys/vc_static-O-2018.09-SP2-2/vcs-mx/etc/uvm-1.2/base/uvm_phase.svh(1349) @ 0: reporter [PH/TRC/STRT] Phase 'common.build' (id=191) Starting phase

UVM_INFO /usr/synopsys/vc_static-O-2018.09-SP2-2/vcs-mx/etc/uvm-1.2/base/uvm_phase.svh(1624) @ 0: reporter [PH/TRC/DONE] Phase 'common.build' (id=191) Completed phase

UVM_INFO /usr/synopsys/vc_static-O-2018.09-SP2-2/vcs-mx/etc/uvm-1.2/base/uvm_phase.svh(1659) @ 0: reporter [PH/TRC/SCHEDULED] Phase 'common.connect' (id=194) Scheduled from phase common.build

UVM_INFO /usr/synopsys/vc_static-O-2018.09-SP2-2/vcs-mx/etc/uvm-1.2/base/uvm_phase.svh(1349) @ 0: reporter [PH/TRC/STRT] Phase 'common.connect' (id=194) Starting phase

UVM_INFO /usr/synopsys/vc_static-O-2018.09-SP2-2/vcs-mx/etc/uvm-1.2/base/uvm_phase.svh(1624) @ 0: reporter [PH/TRC/DONE] Phase 'common.connect' (id=194) Completed phase

UVM_INFO /usr/synopsys/vc_static-O-2018.09-SP2-2/vcs-mx/etc/uvm-1.2/base/uvm_phase.svh(1659) @ 0: reporter [PH/TRC/SCHEDULED] Phase 'common.end_of_elaboration' (id=197) Scheduled from phase common.connect

UVM_INFO /usr/synopsys/vc_static-O-2018.09-SP2-2/vcs-mx/etc/uvm-1.2/base/uvm_phase.svh(1349) @ 0: reporter [PH/TRC/STRT] Phase 'common.end_of_elaboration' (id=197) Starting phase

UVM_INFO /usr/synopsys/vc_static-O-2018.09-SP2-2/vcs-mx/etc/uvm-1.2/base/uvm_root.svh(589) @ 0: reporter [UVMTOP] UVM testbench topology:

-------------------------------------------

Name Type Size Value

-------------------------------------------

uvm_test_top wesley_base_test - @341

-------------------------------------------

UVM_INFO /usr/synopsys/vc_static-O-2018.09-SP2-2/vcs-mx/etc/uvm-1.2/base/uvm_phase.svh(1624) @ 0: reporter [PH/TRC/DONE] Phase 'common.end_of_elaboration' (id=197) Completed phase

UVM_INFO /usr/synopsys/vc_static-O-2018.09-SP2-2/vcs-mx/etc/uvm-1.2/base/uvm_phase.svh(1659) @ 0: reporter [PH/TRC/SCHEDULED] Phase 'common.start_of_simulation' (id=200) Scheduled from phase common.end_of_elaboration

......

UVM_INFO /usr/synopsys/vc_static-O-2018.09-SP2-2/vcs-mx/etc/uvm-1.2/base/uvm_phase.svh(1624) @ 1000000: reporter [PH/TRC/DONE] Phase 'common.common_end' (id=189) Completed phase

UVM_INFO /usr/synopsys/vc_static-O-2018.09-SP2-2/vcs-mx/etc/uvm-1.2/base/uvm_report_server.svh(894) @ 1000000: reporter [UVM/REPORT/SERVER]

--- UVM Report Summary ---

** Report counts by severity

UVM_INFO : 97

UVM_WARNING : 0

UVM_ERROR : 0

UVM_FATAL : 0

** Report counts by id

[ TEST_TOP ] 1

[PH/TRC/DONE] 27

[PH/TRC/SCHEDULED] 26

[PH/TRC/SKIP] 12

[PH/TRC/STRT] 27

[RNTST] 1

[TEST_DONE] 1

[UVM/RELNOTES] 1

[UVMTOP] 1

$finish called from file "/usr/synopsys/vc_static-O-2018.09-SP2-2/vcs-mx/etc/uvm-1.2/base/uvm_root.svh", line 527.

$finish at simulation time 1000000

本文来自博客园,作者:Thisway2014,转载请注明原文链接:https://www.cnblogs.com/thisway2014/p/16463676.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号