1. UVM -- 基础知识

1. UVM -- 基础知识

1.1. 什么是UVM

- 硬件设计主要由几个 Verilog(.v)文件和一个顶部模块组成,其中所有其他子模块都实例化以实现所需的行为和功能。

- IC验证需要 设计一个名为 testbench 的环境;用不同的刺激驱动设计,以观察其输出,并将其与预期值进行比较,以查看设计是否按照应有的方式运行。

- 为了实现 高效 和 可重用 的验证环境和验证 IP (VIP),现在通常用 SystemVerilog 编写,其是 OPP(面向对象) 语言,具有 封装、 继承、 多态 的特性;

- UVM(Universal Verification Methodology 通用验证方法)是一套基于 systemverilog 语言来实现的标准验证方法学;

1.2. UVM 能为用户提供了哪些资源

-

UVM 封装了验证环境所需的所有组件,可以很方便的让验证平台的搭建像搭积木样快速有趣。

-

不止如此

- 一个标准的验证平台的模板

- 一套完备的源码库

- 支持受约束随机激励的产生

- 支持覆盖率驱动的验证模式

- 代码可重用,平台可移植

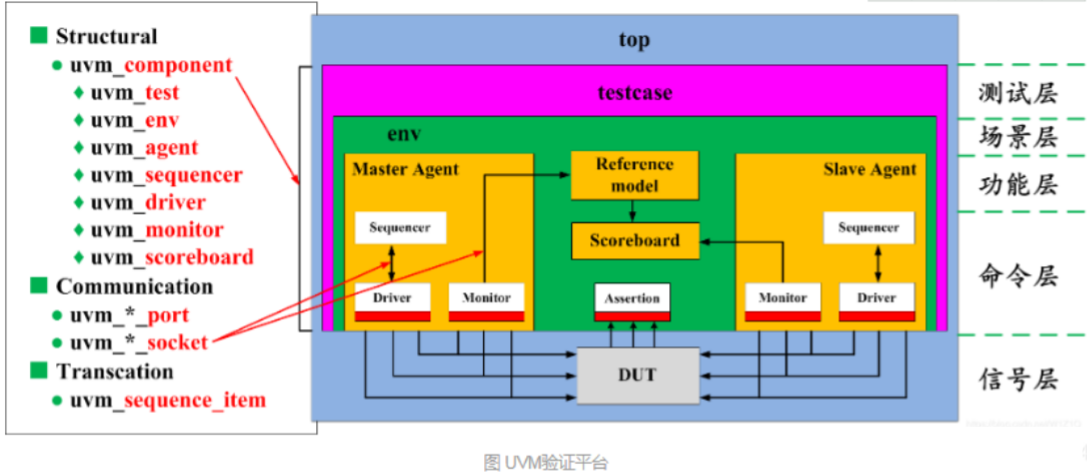

1.3. UVM 结构认识

-

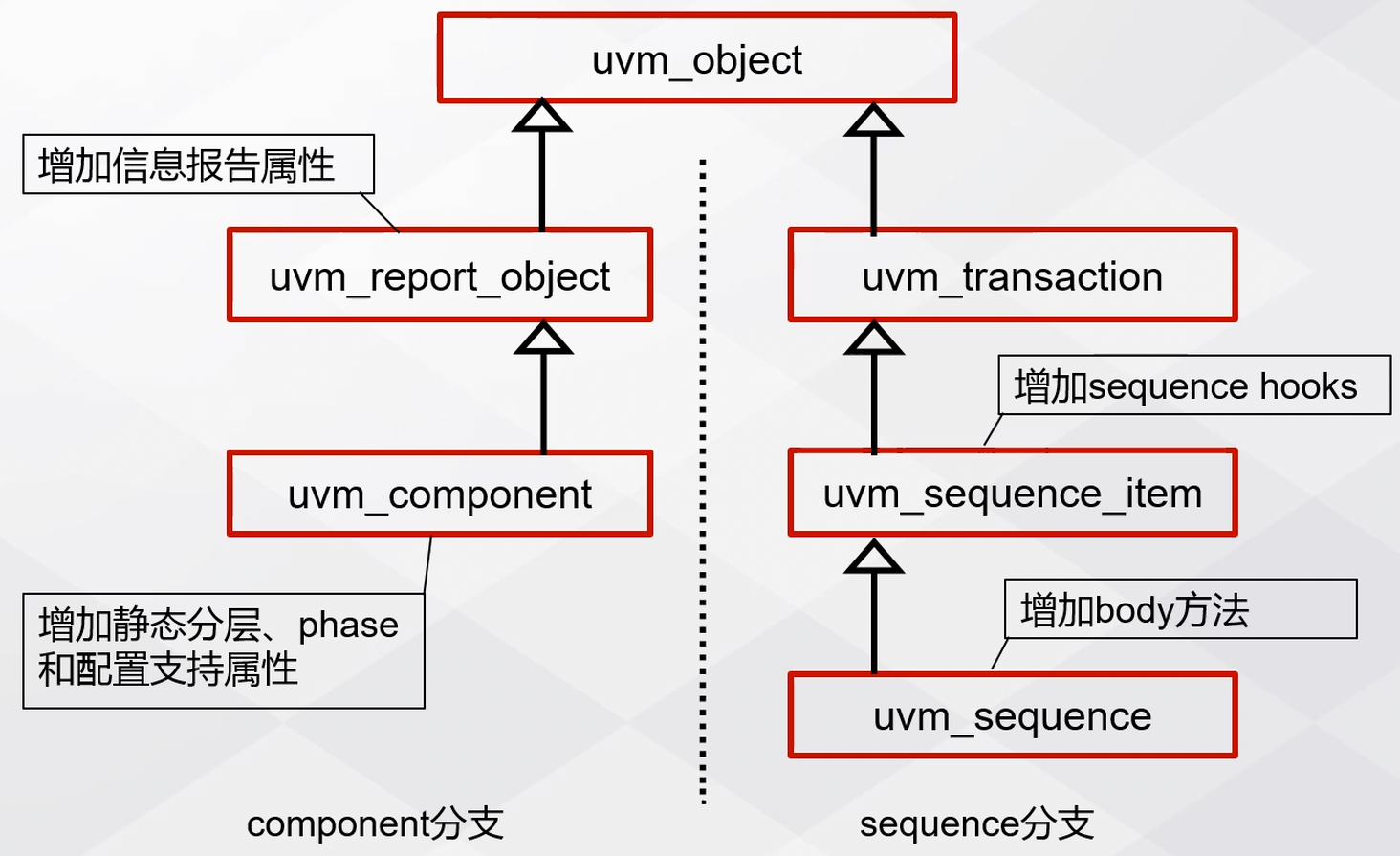

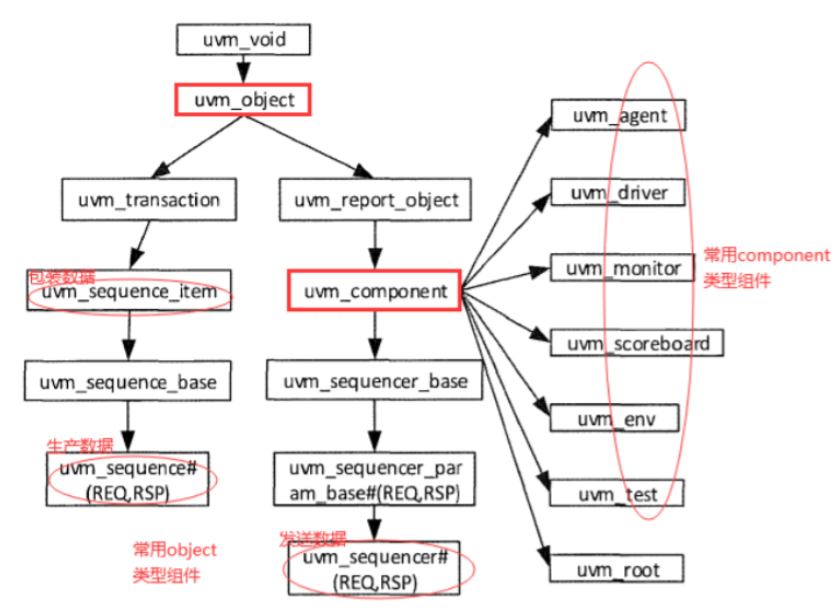

整个uvm构成主要包含uvm_component与uvm_object;uvm_object是UVM中最基本的类;

-

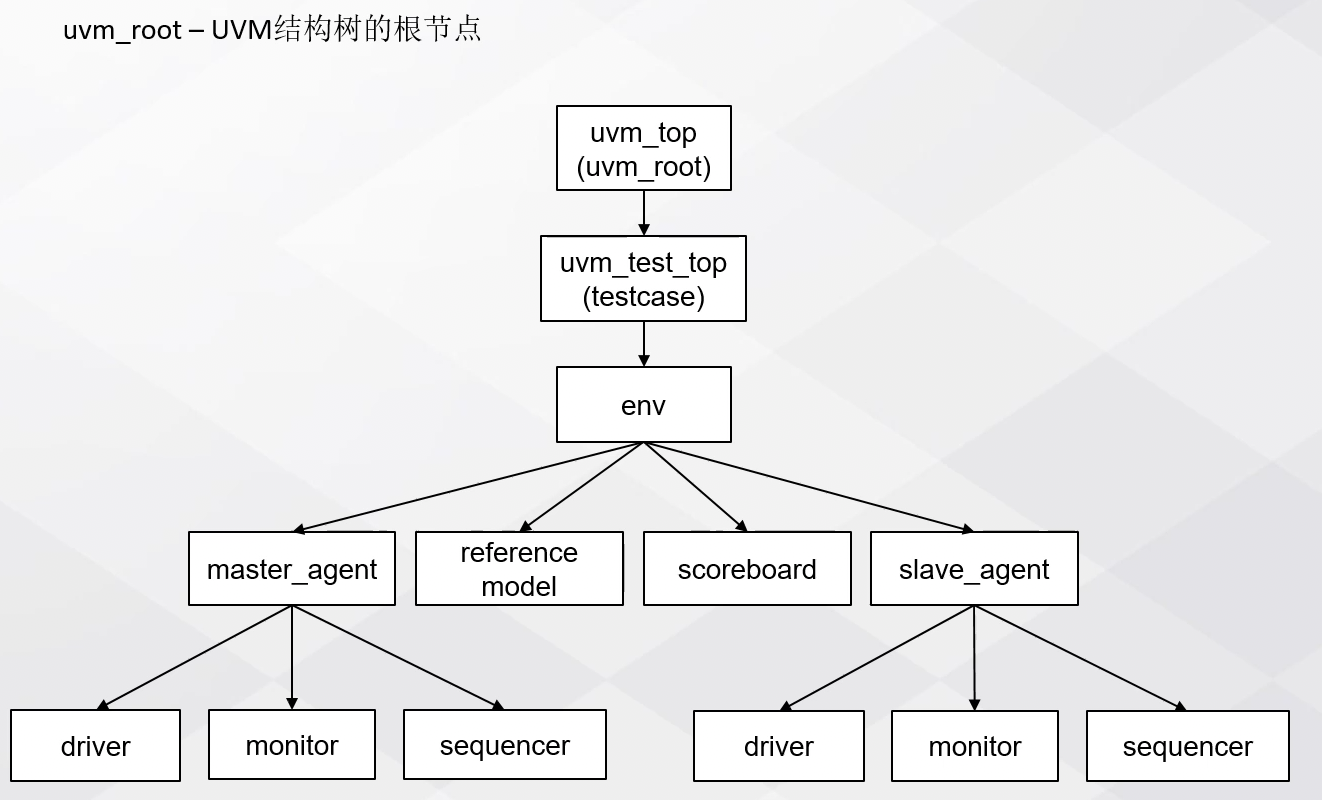

uvm_component因为在创建时有两个参数:name与parent,因此uvm_component 具有一个层次关系,它构成验证环境。uvm_root唯一实例为uvm_top,为整个uvm的根。要求在build_phase阶段完成创建(自顶向下)建立了根才能逐渐向底层创建)。

-

uvm_object创建时的参数只有一个:name,没有层次关系。它作为环境的事务或配置。它可以在整个环境的任何阶段创建。

1.3.1 UVM 结构树特点

- 为config机制提供搜索路径

- 为override机制提供搜索路径

- 是phase自动执行的需要

1.3.2 UVM 常用类

UVM中常用类的继承关系(UVM 实战):

-

uvm_component

- 是用来构建UVM testbench层次结构最基本的类

- 组件中包含了task和function phases

-

uvm_object

- 作为UVM的一种数据结构,可作为配置对象来配置测试平台

-

uvm transaction

- 用来产生激励和收集响应

本文来自博客园,作者:Thisway2014,转载请注明原文链接:https://www.cnblogs.com/thisway2014/p/16461987.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号