DDR相关概念

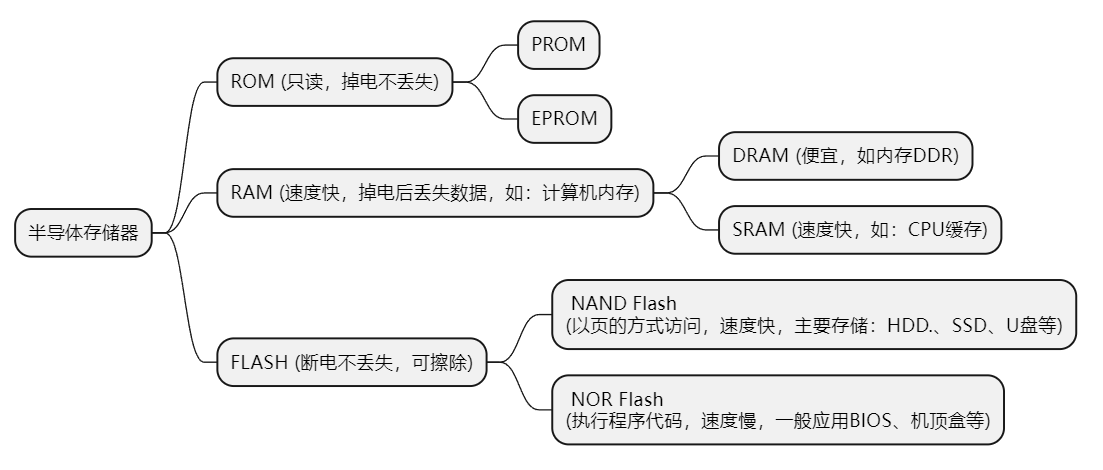

1. 半导体存储器概念

1.1. RAM如何运作

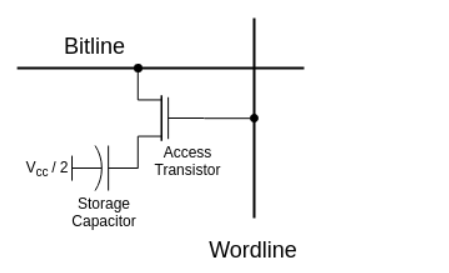

1.1.1. DRAM的结构

结构图上分析,我们可以很容易的推测出 DRAM Storage Cell 的数据读写流程:

-

读数据时,Wordline 设为逻辑高电平,打开 Access Transistor,然后读取 Bitline 上的状态

-

写数据时,先把要写入的电平状态设定到 Bitline 上,然后打开 Access Transistor,通过 Bitline 改变 Storage Capacitor 内部的状态

2. DDR SDRAM 是什么

2.1. 简介

- 全称 :Double Data Rate Synchronous Dynamic Random Access Memory

- DDR :Double Data Rate 双倍速率,

- SDRAM :Synchronous Dynamic Random Access Memory的缩写,即同步动态随机存取存储器。

- DDR SDRAM= 双倍速率 同步动态随机存储器,人们习惯称为DDR

- 中文名:双倍速率同步动态随机存储器

- 外文名:DDR SDRAM英文全称Double Data Rate

2.2. 认识DDR 内存

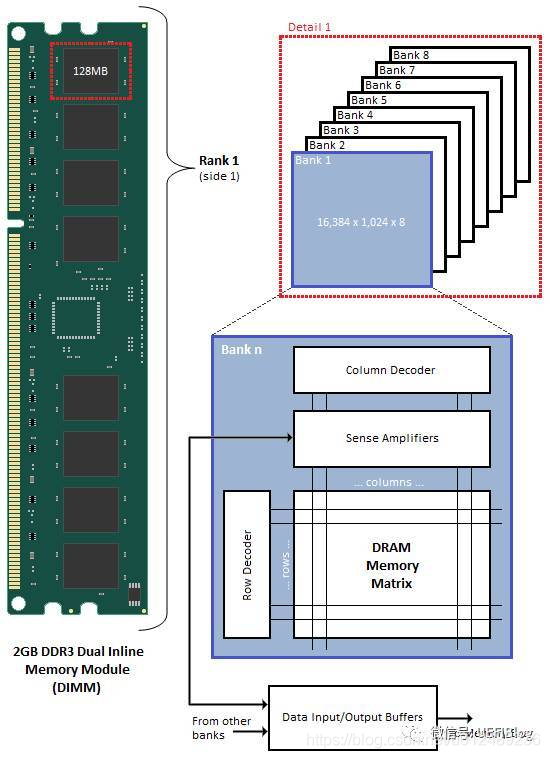

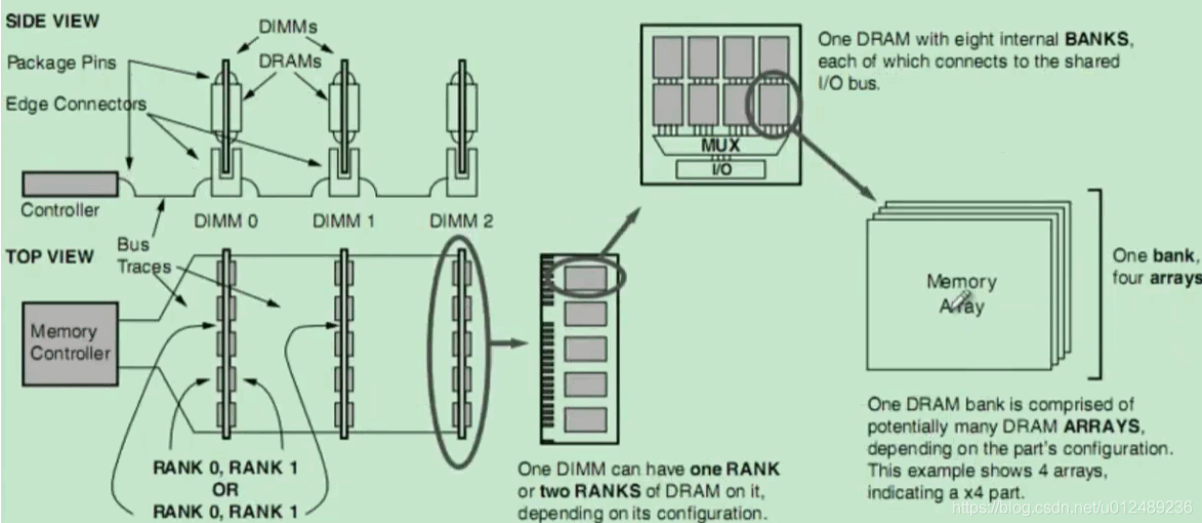

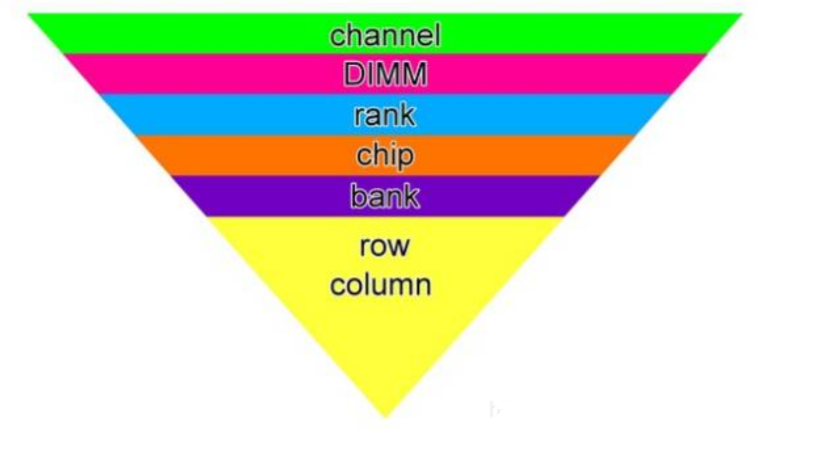

笼统上讲从大到小为:channel > DIMM > rank > chip > bank > row/column,如下图:

-

channel (对应多个DDR控制器)> DIMM(内存插槽) > rank(一次访问位宽决定,也成物理bank) > chip(1个chip大多是4bit/8bit/16bit等,组成一个rank,配合完成一次访问的位宽要求。这就是颗粒) > bank(颗粒里的logic-bank,DDR3一般对应8个bank存储体) > row/column

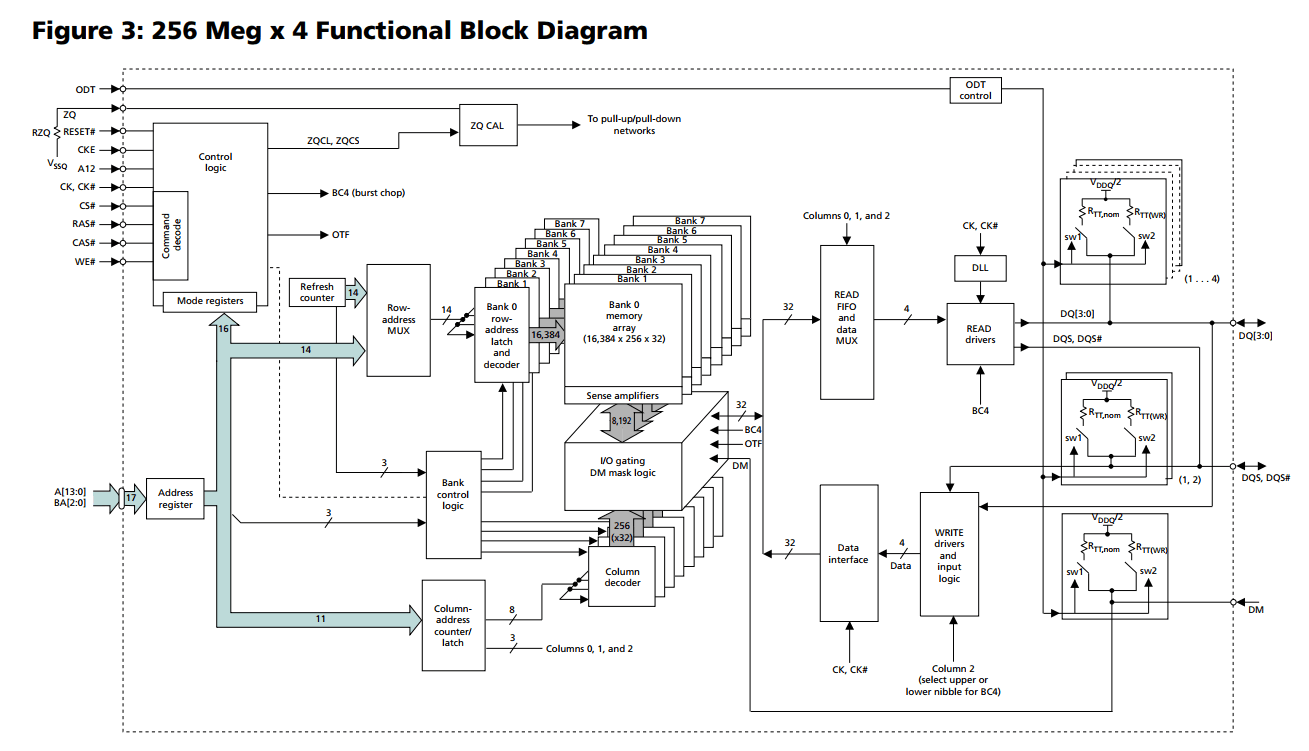

2.3. DDR SDRAM的寻址空间

- DDR SDRAM(以下简称DDR) 是一种同步DRAM,因此需要用户提供 一对 差分的时钟信号

- DDR内部架构由 bank、行row、列col 构成

2.4. 信号描述

其引脚按照功能可以分为7类:

- 前3类为 电源、地、配置;

- 后4类为:控制信号(CS_n\RAS_n\CAS_n\WE_n)、时钟信号(CK\CKE)、地址信号(BG\BA\A0-A15)、数据信号(DM\DQ\DQS)

3. DDR 相关概念

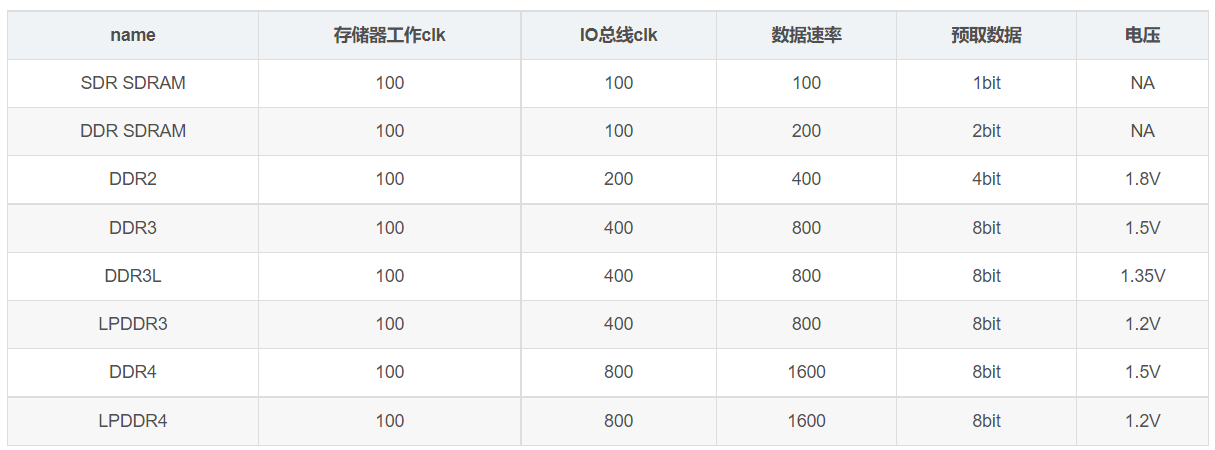

速率提升主要体现在如下两个方面:

- 双沿采数(上升沿和下降沿都取数据),数据传输是工作频率的2倍;

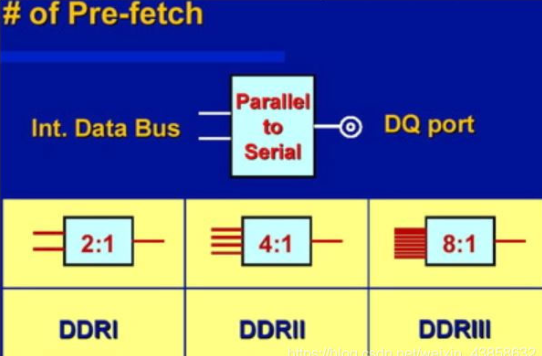

- 预取 预取2n、4n、8n的数据,则IO总线频率是记忆存储芯片工作频率的N倍;

3.1. DDR 预取技术(prefetch)

- SDRAM最开始是时钟下降沿采样,数据传输速率和频率是1:1关系,即一个周期可传输1bit数据;

- DDR1,采用时钟双边沿采样,即上升沿、下降沿都采样。一个时钟周期可传输2bit数据,这个时候,就叫预取2bit技术了(因为一拍需要预取2bit数据)。可知预取2bit技术的基础,就是双边沿采样。

- DDR2,预取4bit。

- DDR3,预取8bit。举例,DDR3-800内存的存储核心频率其实仅有100MHz,其输入/输出时钟频率为400MHz,利用双边沿采样技术,有效数据传输频率则为800MHz。

- 预取bit的意思,我理解就是一个时钟周期时间内,从DDR存储cell能够做到取出多少bit数据。如果一次预取16bit,DDR传输速率就又翻倍了。

- 一般,协议里称为8n prefetch。这个n,我理解就是DQ位宽。所以一个DDR3 16bit SDRAM内存颗粒,其一次读写访问的数据量是8*16=128bit。

3.2. DDR burst 相关概念

- BL,是burst length。对应预取bit数目,DDR3对应的BL是8。

3.3. DDR page页

- DDR logic bank的row就是行,对应行地址选中等。

- DDR页的概念,是针对刷新或者访问来说的,举例,一个rank可能有4个chip组成,一个chip里可能有8个bank,每一个bank有N个行。页指的是一个rank里每个chip,所有bank的一个行地址;注意不是一行,是多行,行数是chip数目*bank数目。

- 所以,DDR页,可以讲为一个rank里每个chip的行地址

- 在一个rank里,每个chip的地址是相同的。因为多个chip组成一个总数据位宽。DDR接口的cs信号,虽然叫chip select,其实是rank(一组chip)的 select。

- DDR页的概念,会涉及页命中、页miss等,跟cache page原理一样。

3.4. DDR 刷新 auto-refresh 和 self-refresh

刷新的目的: DDR的最小存储单元电路形式是电容,是通过充放电,实现0,1值存储。长时间存储电容电荷会漏电,故需要刷新和预充电进行补充。

刷新分为两种:

- 自动刷新(Auto Refresh,简称AR/REF,需要ck,CKE高)

- 自刷新(Self Refresh,简称SR/SRE-SRF,sdram内部产生,不依赖ck,CKE低,用于休眠模式或低功耗)。

- 自动刷新 AR 是指控制器 CTL 必须参与发起每一个自动刷新请求。适合正常工作的时候,由控制器来主导刷新操作。

- 自刷新 SR 是指控制器 CTL 只发起刷新开始和结束两个请求。适合休眠 power-down 模式,DRAM颗粒自己负责刷新操作。

- 自动刷新 AR 和自刷新 SR,接口指令是类似的,除了CKE为低表明自刷新 SR 开始 。

3.5. DDR 预充电 Precharge

预充电和刷新,都是为了保持电荷存储,做出的电路重写动作。

- 由于SDRAM的寻址具体独占性,所以在进行完读写操作后, 如果要对同一L-Bank的另一行进行寻址,就要将原来有效(工作)的行关闭,重新发送行/列地址。L-Bank关闭现有工作行,准备打开新行的操作就是预充电(Precharge)。

- 预充电可以通过命令控制,也可以通过辅助设定让芯片在 每次读写操作之后自动进行预充电 。

- 预充电是 针对一个bank或者所有bank的一行的操作;

- 刷新是同时对 所有bank的所有行 操作。

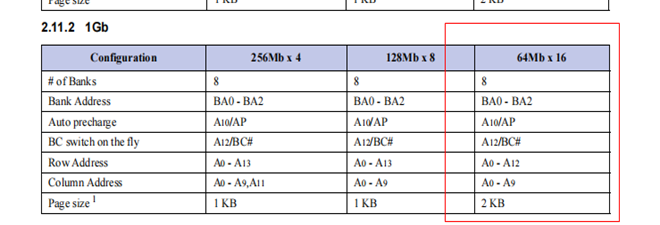

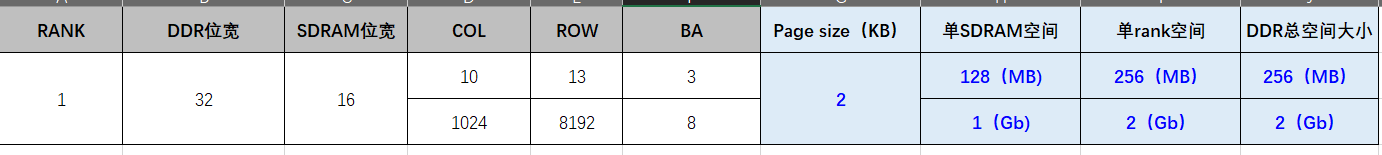

问题:DDR空间大小的计算 :256MB (16bits)

4. 参考:

https://www.cnblogs.com/sky-heaven/p/15948268.html

https://blog.csdn.net/u012489236/article/details/107730731

https://blog.csdn.net/u012489236/article/details/107750942

https://digitalasic.design/category/ddr/ddr-学习时间/

本文来自博客园,作者:Thisway2014,转载请注明原文链接:https://www.cnblogs.com/thisway2014/p/16385101.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号