详解zynq/zynqmp的gpio系统

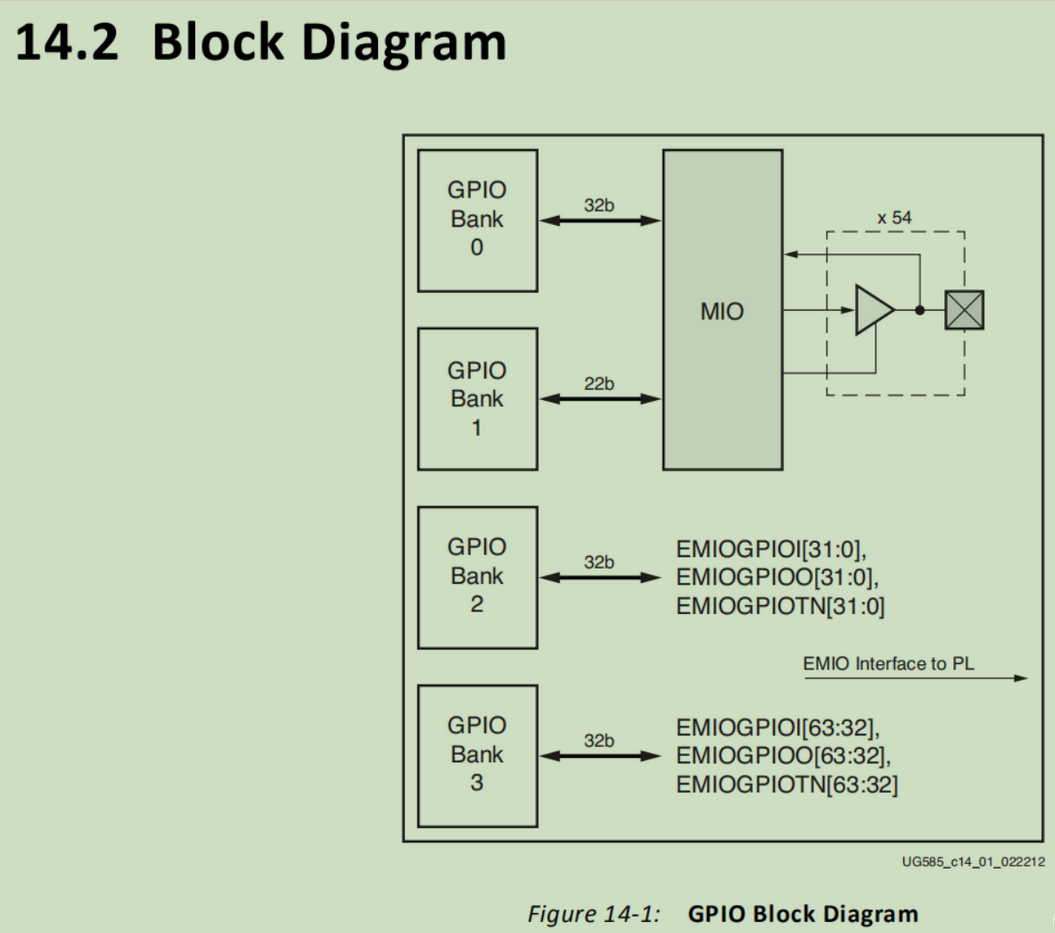

zynq7000系列拥有共计最多118个gpio的引脚控制(理论上ps+pl),其中MIO 54个,EMIO64个,其trm的框图如下

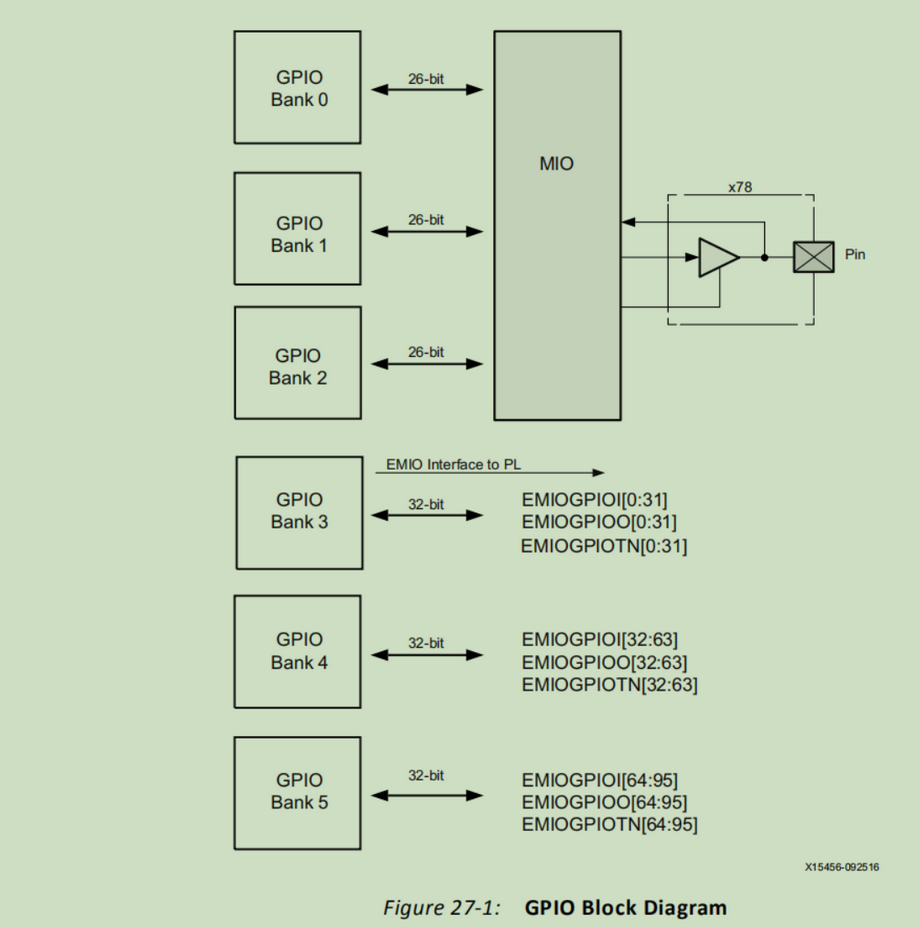

zynqmp系列同样如下 其MIO 78 EMIO 96 其trm的框图如下

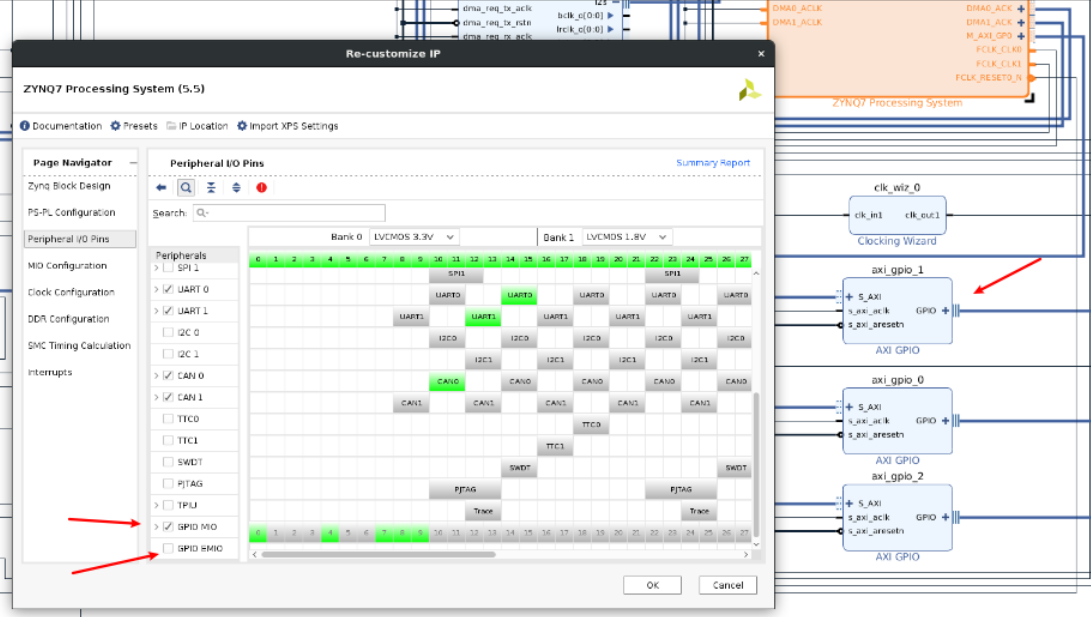

此外zynq还可以通过AXI总线进行GPIO的扩展

在vivado的框图上如下所示,这里用的是7020 的器件,zynqmp与其相似

接下来详细叙述 如何使用

这里还是以7020为例,zynqmp与其极其相似 就是位号稍有差异而已

1)首先是最简单的,在内核起来后如何使用

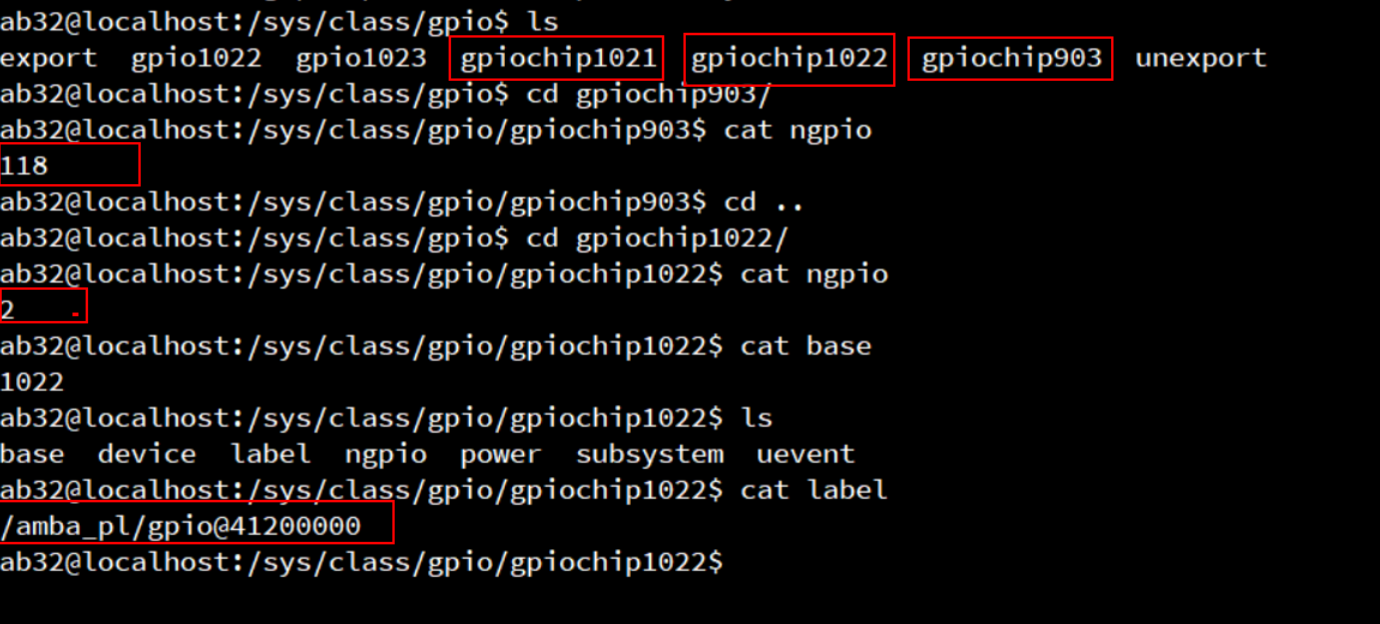

这个直接在sys文件系统的gpio下即可使用,我这边使用AXI_GPIO扩展了三组gpio,其中的两组在内核下使能了,所以gpio下可以看到三个chip组

进一步可以看到903为起始的标号对应的为MIO+EMIO的gpio

其他两个为AXI扩展的

例如:

这里面如果想使用MIO28则直接以903+28的位号导出gpio就可以,(sys下如何使用gpio,自己学一下,只是使用的网上很多)

如果使用EMIO10的话则导出的位号为903+54+10(54位MIO的个数)

如果使用41200000对应的axi_gpio[1]的话则导出的位号为1023(1022+1)(AXI的地址在vivado中可以看到)

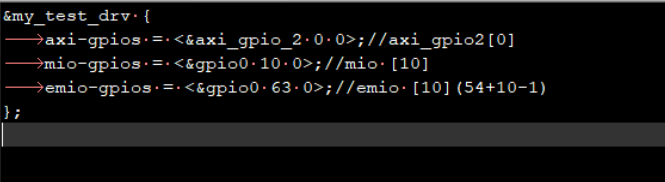

2)如果在内核驱动中使用gpio节点该怎么做

这里面主要通过dts向内核中传递,使用如下的格式进行

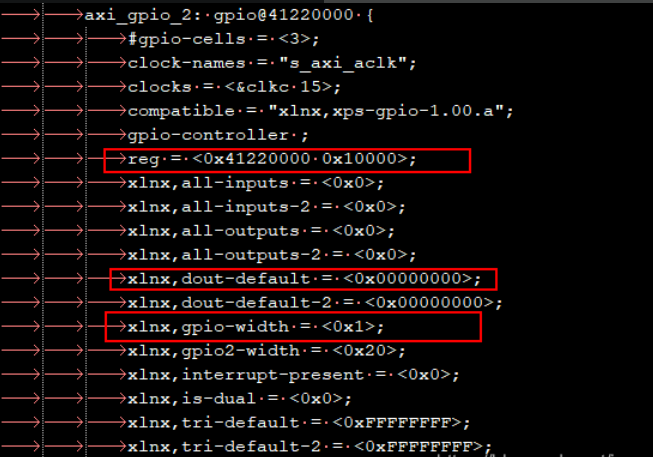

其中axi的节点说明在pl.dtsi中可以看到,包括基址,位宽,默认值,等

在uboot中使用

在uboot下使用的常用场景为对某一器件进行rest

这里直接贴出代码modify from zynq_gpio.c and xilinx_gpio.c

下面是适用于MIO/EMIO的代码

#define ZYNQ_GPIO_MAX_BANK 4

#define ZYNQMP_GPIO_MAX_BANK 6

#define ZYNQ_GPIO_BANK0_NGPIO 32

#define ZYNQ_GPIO_BANK1_NGPIO 22

#define ZYNQ_GPIO_BANK2_NGPIO 32

#define ZYNQ_GPIO_BANK3_NGPIO 32

#define ZYNQMP_GPIO_NR_GPIOS 174

#define ZYNQ_GPIO_NR_GPIOS (ZYNQ_GPIO_BANK0_NGPIO + \

ZYNQ_GPIO_BANK1_NGPIO + \

ZYNQ_GPIO_BANK2_NGPIO + \

ZYNQ_GPIO_BANK3_NGPIO)

struct zynq_platform_data

{

const char *label;

u16 ngpio;

u32 max_bank;

u32 bank_min[ZYNQMP_GPIO_MAX_BANK];

u32 bank_max[ZYNQMP_GPIO_MAX_BANK];

};

#define ZYNQ_GPIO_BANK0_PIN_MIN(str) 0

#define ZYNQ_GPIO_BANK0_PIN_MAX(str) (ZYNQ_GPIO_BANK0_PIN_MIN(str) + \

ZYNQ##str##_GPIO_BANK0_NGPIO - 1)

#define ZYNQ_GPIO_BANK1_PIN_MIN(str) (ZYNQ_GPIO_BANK0_PIN_MAX(str) + 1)

#define ZYNQ_GPIO_BANK1_PIN_MAX(str) (ZYNQ_GPIO_BANK1_PIN_MIN(str) + \

ZYNQ##str##_GPIO_BANK1_NGPIO - 1)

#define ZYNQ_GPIO_BANK2_PIN_MIN(str) (ZYNQ_GPIO_BANK1_PIN_MAX(str) + 1)

#define ZYNQ_GPIO_BANK2_PIN_MAX(str) (ZYNQ_GPIO_BANK2_PIN_MIN(str) + \

ZYNQ##str##_GPIO_BANK2_NGPIO - 1)

#define ZYNQ_GPIO_BANK3_PIN_MIN(str) (ZYNQ_GPIO_BANK2_PIN_MAX(str) + 1)

#define ZYNQ_GPIO_BANK3_PIN_MAX(str) (ZYNQ_GPIO_BANK3_PIN_MIN(str) + \

ZYNQ##str##_GPIO_BANK3_NGPIO - 1)

static const struct zynq_platform_data zynq_gpio_def = {

.label = "zynq_gpio",

.ngpio = ZYNQ_GPIO_NR_GPIOS,

.max_bank = ZYNQ_GPIO_MAX_BANK,

.bank_min[0] = ZYNQ_GPIO_BANK0_PIN_MIN(),

.bank_max[0] = ZYNQ_GPIO_BANK0_PIN_MAX(),

.bank_min[1] = ZYNQ_GPIO_BANK1_PIN_MIN(),

.bank_max[1] = ZYNQ_GPIO_BANK1_PIN_MAX(),

.bank_min[2] = ZYNQ_GPIO_BANK2_PIN_MIN(),

.bank_max[2] = ZYNQ_GPIO_BANK2_PIN_MAX(),

.bank_min[3] = ZYNQ_GPIO_BANK3_PIN_MIN(),

.bank_max[3] = ZYNQ_GPIO_BANK3_PIN_MAX(),

};

static const struct zynq_platform_data zynqmp_gpio_def = {

.label = "zynqmp_gpio",

.ngpio = ZYNQMP_GPIO_NR_GPIOS,

.max_bank = ZYNQMP_GPIO_MAX_BANK,

.bank_min[0] = ZYNQ_GPIO_BANK0_PIN_MIN(MP),

.bank_max[0] = ZYNQ_GPIO_BANK0_PIN_MAX(MP),

.bank_min[1] = ZYNQ_GPIO_BANK1_PIN_MIN(MP),

.bank_max[1] = ZYNQ_GPIO_BANK1_PIN_MAX(MP),

.bank_min[2] = ZYNQ_GPIO_BANK2_PIN_MIN(MP),

.bank_max[2] = ZYNQ_GPIO_BANK2_PIN_MAX(MP),

.bank_min[3] = ZYNQ_GPIO_BANK3_PIN_MIN(MP),

.bank_max[3] = ZYNQ_GPIO_BANK3_PIN_MAX(MP),

.bank_min[4] = ZYNQ_GPIO_BANK4_PIN_MIN(MP),

.bank_max[4] = ZYNQ_GPIO_BANK4_PIN_MAX(MP),

.bank_min[5] = ZYNQ_GPIO_BANK5_PIN_MIN(MP),

.bank_max[5] = ZYNQ_GPIO_BANK5_PIN_MAX(MP),

};

/**

* @brief copy from zynq_gpio.c

*

*/

#define ZYNQ_GPIO_DATA_LSW_OFFSET(BANK) (0x000 + (8 * BANK))

/* MSW Mask & Data -WO */

#define ZYNQ_GPIO_DATA_MSW_OFFSET(BANK) (0x004 + (8 * BANK))

/* Data Register-RW */

#define ZYNQ_GPIO_DATA_RO_OFFSET(BANK) (0x060 + (4 * BANK))

/* Direction mode reg-RW */

#define ZYNQ_GPIO_DIRM_OFFSET(BANK) (0x204 + (0x40 * BANK))

/* Output enable reg-RW */

#define ZYNQ_GPIO_OUTEN_OFFSET(BANK) (0x208 + (0x40 * BANK))

/* Interrupt mask reg-RO */

#define ZYNQ_GPIO_INTMASK_OFFSET(BANK) (0x20C + (0x40 * BANK))

/* Interrupt enable reg-WO */

#define ZYNQ_GPIO_INTEN_OFFSET(BANK) (0x210 + (0x40 * BANK))

/* Interrupt disable reg-WO */

#define ZYNQ_GPIO_INTDIS_OFFSET(BANK) (0x214 + (0x40 * BANK))

/* Interrupt status reg-RO */

#define ZYNQ_GPIO_INTSTS_OFFSET(BANK) (0x218 + (0x40 * BANK))

/* Interrupt type reg-RW */

#define ZYNQ_GPIO_INTTYPE_OFFSET(BANK) (0x21C + (0x40 * BANK))

/* Interrupt polarity reg-RW */

#define ZYNQ_GPIO_INTPOL_OFFSET(BANK) (0x220 + (0x40 * BANK))

/* Interrupt on any, reg-RW */

#define ZYNQ_GPIO_INTANY_OFFSET(BANK) (0x224 + (0x40 * BANK))

/* Mid pin number of a bank */

#define ZYNQ_GPIO_MID_PIN_NUM 16

/* GPIO upper 16 bit mask */

#define ZYNQ_GPIO_UPPER_MASK 0xFFFF0000

/**

* @brief copy and modify from zynq_gpio.c

*

* @param pin_num

* @param bank_num

* @param bank_pin_num

*/

void zynq_gpio_get_bank_pin(unsigned int pin_num, unsigned int *bank_num, unsigned int *bank_pin_num)

{

u32 bank;

for (bank = 0; bank < zynq_gpio_def.max_bank; bank++)

{

if (pin_num >= zynq_gpio_def.bank_min[bank] &&

pin_num <= zynq_gpio_def.bank_max[bank])

{

*bank_num = bank;

*bank_pin_num = pin_num -

zynq_gpio_def.bank_min[bank];

return;

}

}

if (bank >= zynq_gpio_def.max_bank)

{

printf("Invalid bank and pin num\n");

*bank_num = 0;

*bank_pin_num = 0;

}

}

#define ZYNQ_GPIO_BASEADDR 0xE000A000

static int zynq_gpio_direction_output(unsigned pin, int direction)

{

u32 reg;

unsigned int bank_num, bank_pin_num;

zynq_gpio_get_bank_pin(pin, &bank_num, &bank_pin_num);

/* set the GPIO pin as output */

reg = readl(ZYNQ_GPIO_BASEADDR + ZYNQ_GPIO_DIRM_OFFSET(bank_num));

if (direction != (u32)0)

{ /* Output Direction */

reg |= ((u32)1 << (u32)bank_pin_num);

}

else

{ /* Input Direction */

reg &= ~((u32)1 << (u32)bank_pin_num);

}

writel(reg, ZYNQ_GPIO_BASEADDR + ZYNQ_GPIO_DIRM_OFFSET(bank_num));

return 0;

}

static int zynq_gpio_enable_output(unsigned pin, int value)

{

u32 reg;

unsigned int bank_num, bank_pin_num;

zynq_gpio_get_bank_pin(pin, &bank_num, &bank_pin_num);

/* set the GPIO pin as output */

reg = readl(ZYNQ_GPIO_BASEADDR + ZYNQ_GPIO_OUTEN_OFFSET(bank_num));

if (value != (u32)0)

{ /* Output Direction */

reg |= ((u32)1 << (u32)bank_pin_num);

}

else

{ /* Input Direction */

reg &= ~((u32)1 << (u32)bank_pin_num);

}

writel(reg, ZYNQ_GPIO_BASEADDR + ZYNQ_GPIO_OUTEN_OFFSET(bank_num));

return 0;

}

static int zynq_gpio_set_value(unsigned pin, int value)

{

unsigned int reg_offset, bank_num, bank_pin_num;

zynq_gpio_get_bank_pin(pin, &bank_num, &bank_pin_num);

if (bank_pin_num >= ZYNQ_GPIO_MID_PIN_NUM)

{

/* only 16 data bits in bit maskable reg */

bank_pin_num -= ZYNQ_GPIO_MID_PIN_NUM;

reg_offset = ZYNQ_GPIO_DATA_MSW_OFFSET(bank_num);

}

else

{

reg_offset = ZYNQ_GPIO_DATA_LSW_OFFSET(bank_num);

}

/*

* get the 32 bit value to be written to the mask/data register where

* the upper 16 bits is the mask and lower 16 bits is the data

*/

value = !!value;

value = ~(1 << (bank_pin_num + ZYNQ_GPIO_MID_PIN_NUM)) &

((value << bank_pin_num) | ZYNQ_GPIO_UPPER_MASK);

writel(value, ZYNQ_GPIO_BASEADDR + reg_offset);

return 0;

}

在使用时采用如下的例子

eg:

zynq_gpio_direction_output(i, 1);//i的选择与上述的dts下的选择一致

zynq_gpio_enable_output(i , 1);

zynq_gpio_set_value(i, 0);

下面是适用于AXI_GPIO的代码

#define XILINX_GPIO_MAX_BANK 2

/* Gpio simple map */

struct gpio_regs

{

u32 gpiodata;

u32 gpiodir;

};

struct xilinx_gpio_privdata

{

u32 output_val[XILINX_GPIO_MAX_BANK];

};

struct xilinx_gpio_platdata

{

struct gpio_regs *regs;

int bank_max[XILINX_GPIO_MAX_BANK];

int bank_input[XILINX_GPIO_MAX_BANK];

int bank_output[XILINX_GPIO_MAX_BANK];

u32 dout_default[XILINX_GPIO_MAX_BANK];

struct xilinx_gpio_privdata priv;

};

struct xilinx_gpio_platdata axi_gpio_1;

struct xilinx_gpio_platdata axi_gpio_2;

static int xilinx_gpio_init()

{

axi_gpio_1.regs = (struct gpio_regs *)0x41210000;

axi_gpio_1.bank_max[0] = 2;

axi_gpio_1.bank_input[0] = 0;

axi_gpio_1.bank_output[0] = 0;

axi_gpio_1.dout_default[0] = 0;

axi_gpio_1.priv.output_val[0] = axi_gpio_1.dout_default[0];

}

static int xilinx_gpio_get_bank_pin(unsigned offset, u32 *bank_num,

u32 *bank_pin_num, struct xilinx_gpio_platdata *platdata)

{

u32 bank, max_pins;

/* the first gpio is 0 not 1 */

u32 pin_num = offset;

for (bank = 0; bank < XILINX_GPIO_MAX_BANK; bank++)

{

max_pins = platdata->bank_max[bank];

if (pin_num < max_pins)

{

debug("%s: found at bank 0x%x pin 0x%x\n", __func__,

bank, pin_num);

*bank_num = bank;

*bank_pin_num = pin_num;

return 0;

}

pin_num -= max_pins;

}

return -EINVAL;

}

static int xilinx_gpio_set_value(struct xilinx_gpio_platdata *platdata, unsigned offset,

int value)

{

struct xilinx_gpio_privdata *priv = &(platdata->priv);

int val, ret;

u32 bank, pin;

ret = xilinx_gpio_get_bank_pin(offset, &bank, &pin, platdata);

if (ret)

return ret;

val = priv->output_val[bank];

debug("%s: regs: %lx, value: %x, gpio: %x, bank %x, pin %x, out %x\n",

__func__, (ulong)platdata->regs, value, offset, bank, pin, val);

if (value)

val = val | (1 << pin);

else

val = val & ~(1 << pin);

writel(val, &platdata->regs->gpiodata + bank * 2);

priv->output_val[bank] = val;

return 0;

};

static int xilinx_gpio_get_value(struct xilinx_gpio_platdata *platdata, unsigned offset)

{

struct xilinx_gpio_privdata *priv = &(platdata->priv);

int val, ret;

u32 bank, pin;

ret = xilinx_gpio_get_bank_pin(offset, &bank, &pin, platdata);

if (ret)

return ret;

debug("%s: regs: %lx, gpio: %x, bank %x, pin %x\n", __func__,

(ulong)platdata->regs, offset, bank, pin);

if (platdata->bank_output[bank])

{

debug("%s: Read saved output value\n", __func__);

val = priv->output_val[bank];

}

else

{

debug("%s: Read input value from reg\n", __func__);

val = readl(&platdata->regs->gpiodata + bank * 2);

}

val = !!(val & (1 << pin));

return val;

};

static int xilinx_gpio_direction_output(struct xilinx_gpio_platdata *platdata, unsigned offset,

int value)

{

int val, ret;

u32 bank, pin;

ret = xilinx_gpio_get_bank_pin(offset, &bank, &pin, platdata);

if (ret)

return ret;

/* can't change it if all is input by default */

if (platdata->bank_input[bank])

return -EINVAL;

xilinx_gpio_set_value(platdata, offset, value);

if (!platdata->bank_output[bank])

{

val = readl(&platdata->regs->gpiodir + bank * 2);

val = val & ~(1 << pin);

writel(val, &platdata->regs->gpiodir + bank * 2);

}

return 0;

}

static int xilinx_gpio_direction_input(struct xilinx_gpio_platdata *platdata, unsigned offset)

{

int val, ret;

u32 bank, pin;

ret = xilinx_gpio_get_bank_pin(offset, &bank, &pin, platdata);

if (ret)

return ret;

/* Already input */

if (platdata->bank_input[bank])

return 0;

/* can't change it if all is output by default */

if (platdata->bank_output[bank])

return -EINVAL;

val = readl(&platdata->regs->gpiodir + bank * 2);

val = val | (1 << pin);

writel(val, &platdata->regs->gpiodir + bank * 2);

return 0;

}

在使用时采用如下的例子

这里需要注意的是init时的地址!!!一定要与vivado中的进行对应

eg:

xilinx_gpio_init();

xilinx_gpio_direction_output(&axi_gpio_1, 0, 1); //

xilinx_gpio_set_value(&axi_gpio_1, 0, 0);

4)fsbl中使用gpio

这个直接采用sdk中关于gpio的API即可,主要也是位号的选择及确认