DDR3 SDRAM 底层逻辑

一.DDR3 SDRAM

1.基本介绍

DDR3 SDRAM 英 文 全 称 “ Double-Data-Rate Three Synchronous Dynamic Random Access Memory”,译为“第三代双倍速率同步动态随机存取内存”或“同步动态随机存储器”,是动态随机存储器(Dynamic Random Access Memory,简称 DRAM)家族的一份子。

同步、动态、随机是其性能特点的外在说明,也是其区别其他存储器的特色标签。这三个概念性的标签,我们要好好理解掌握。

双倍速率(Double-Data-Rate):DDR3 SDRAM 存储器与 SDRAM 有一个很大的不同,DDR3 SDRAM 或者说带 DDR 开头的。包括 DDR1、DDR2、DDR3、DDR4、DDR4,他们都有一个很大的相似点,就是双边沿输出输入数据,通俗来讲就是在一个周期内输出 2 次数据,上升沿输出一次数据,下降沿输出一次数据。而 SDRAM 则是在一个周期内的上升沿输出一次数据,下降沿不输出,所以同频率的 DDR3 SDRAM 与 SDRAM 相比速度快一倍。

同步(Synchronous):与通常的异步 DRAM 不同,DDR3 SDRAM 存在一个同步接口,其工作时钟的时钟频率与对应控制器(CPU/FPGA)的时钟频率相同,并且 SDRAM 内部的命令发送与数据传输均以此时钟为基准,实现指令或数据的同步操作;

动态(Dynamic):DDR3 SDRAM 需要不断的刷新来保证存储阵列内数据不丢失;

随机(Random):数据在 DDR3 SDRAM 中并不是按照线性依次存储,而是可以自由指定地址进行数据的读写。

空间存储量大、读写速度快以及价格相对便宜等优点使其在存储界屹立不倒、经久不衰,广泛应用在计算机中。

2.存储原理

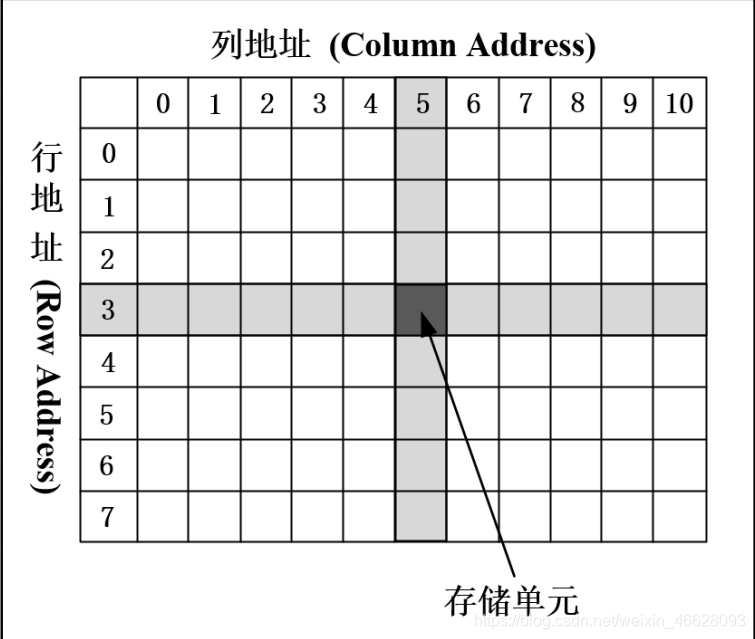

简单来说,DDR3 SDRAM 内部可以理解为一个存储阵列,这是 DDR3 SDRAM 区别于管道式存储,实现随机地址存取的结构特点。为方便读者理解,我们将 DDR3 SDRAM 内部存储阵列类比于一张表格,表格中的每一个单元格可以类比为存储阵列的单个存储单元。若想要实现存储阵列中的某一存储单元的数据读写操作,我们要通过行地址(RowAddress)和列地址(Column Address)(先行后列)精确定位到这一存储单元,进而进行数据的

读写操作,这就是所谓的随机地址存取。DDR3 SDRAM 存储阵列类比图,如下图所示:

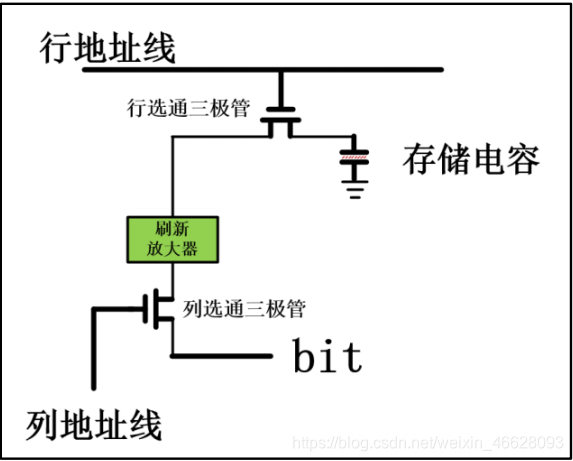

DDR3 SDRAM 的基本存储单位是存储单元,而一个存储单元的容量为若干个 Bit,对于 DDR3 SDRAM 而言就是芯片的位宽,每个 Bit 存放于一个单独的存储体中,存储体是利用电容能够保持电荷以及可充放电的特性制成,主要由行选通三极管、列选通三极管、存储电容以及刷新放大器构成。电容所存储的电荷会随时间慢慢释放,这就需要不断刷新为电容充电,以保证存储数据可靠性。

如图所示:

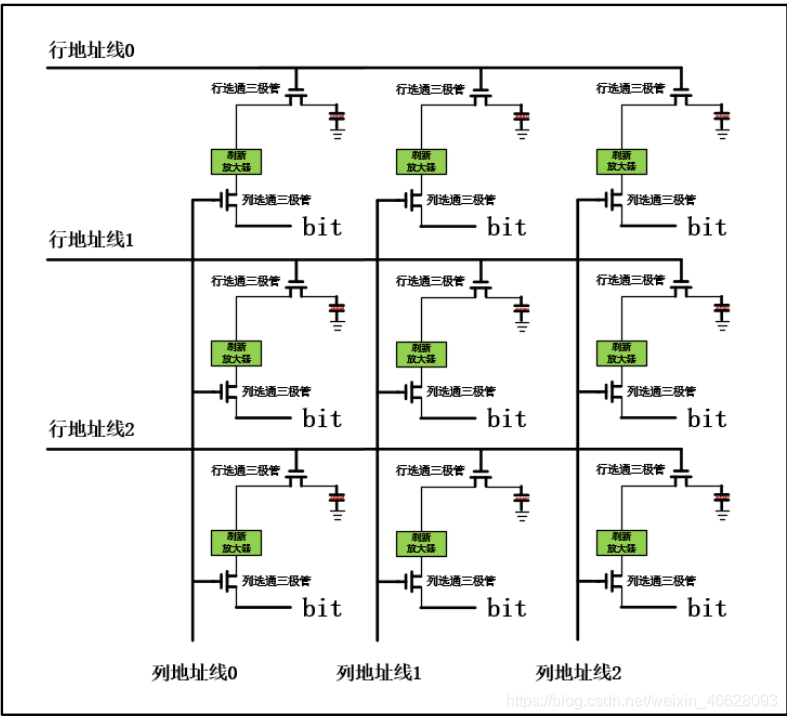

将每个存储单元简化为单 Bit 的存储体,再将若干存储体排列为矩阵,同一行将行地址线相连,同一列将列地址线相连,就构成了一个存储阵列的简化模型。DDR3 SDRAM:内部存储阵列的简化模型,具体见图:

3.内部逻辑功能图

由图 可知,DDR3 SDRAM 内部包含一个逻辑控制单元,内部包含模式寄存器和命令解码器。外部通过 CS_N、RAC_N、CAS_N、WE_N 以及地址总线向逻辑控制单元输入命令,命令经过命令解码器进行译码后,将控制参数保存到模式寄存器中,逻辑控制单元进而控制逻辑运行。外部通过地址总线输入地址信息,地址信息在逻辑控制单元进行逻辑控制时起到辅助作用,除此之外,复用的地址总线与 Bank 控制逻辑、行地址复用器、列地址计数锁存器、列地址解码器等内部器件共同作用,精确选定存储阵列中与行列地址相对应的存储单元,进而进行数据存取操作。

4.AXI接口介绍

AXI 的英文全称是 Advancede Xtensible Interface,即高级可扩展接口。之所以要采用 AXI4 接口对 ddr 进行读写是因为 Xilinx 的 migddrIp 核,无论是 6 系列还是 7 系列还是最新的 FPGA,都集成了 AXI4 接口,为了采用 AXI4 接口进行读写,后续可以兼容 xilinx的其他 fpga,可复用性更强。

AXI 协议是一种高性能、高带宽、低延迟的片内总线,具有如下特点:

1、总线的地址/控制和数据通道是分离的;

2、支持不对齐的数据传输;

3、支持突发传输,突发传输过程中只需要首地址;

4、具有分离的读/写数据通道;

5、支持显著传输访问和乱序访问;

6、更加容易进行时序收敛。

在数字电路中只能传输二进制数 0 和 1,因此可能需要一组信号才能高效地传输信息,这一组信号就组成了接口。AXI4 协议支持以下三种类型的接口:

1、AXI4:高性能存储映射接口。

2、AXI4-Lite:简化版的 AXI4 接口,用于较少数据量的存储映射通信。

3、AXI4-Stream:用于高速数据流传输,非存储映射接口。

在这里我们首先解释一下存储映射(Meamory Map)这一概念。如果一个协议是存储映射的,那么主机所发出的会话(无论读或写)就会标明一个地址。这个地址对应于系统存储空间中的一个地址,表明是针对该存储空间的读写操作。AXI4 协议支持突发传输,主要用于处理器访问存储器等需要指定地址的高速数据传输场景。AXI-Lite 为外设提供单个数据传输,主要用于访问一些低速外设中的寄存器。而 AXI-Stream 接口则像 FIFO 一样,数据传输时不需要地址,在主从设备之间直接连续读写数据,主要用于如视频、高速AD、PCIe、DMA 接口等需要高速数据传输的场合。

参考文献:

1.https://blog.csdn.net/weixin_46628093/article/details/115558116

posted on 2024-07-05 10:10 taylorrrrrrrrrr 阅读(65) 评论(0) 编辑 收藏 举报

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· 开源Multi-agent AI智能体框架aevatar.ai,欢迎大家贡献代码

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· AI技术革命,工作效率10个最佳AI工具