Altera三速以太网IP核使用(上篇)之快速仿真

对于比较高级的ip核,altera一般都会提供仿真案例,网上有关于这个IP核的各种仿真方法,但都比较繁琐,前几日,朋友跟我分享了一个比较快速高效的仿真方法,这个方法也是他摸索折腾了一段时间才总结出来的,在此,也谢谢他这种毫无保留的分享奉献精神,估计此套方法可以针对Altera的大多数复杂ip核仿真。

新建工程,生成ip核的步骤我就省略了,直接进入ip核调用仿真部分。

在生成的工程里找到“testbench”文件夹,里面有一个README.txt,打开按照里面的步骤操作即可。

根据上面的步骤,首先是打开“testbench”文件夹里的"generate_sim.qpf"工程

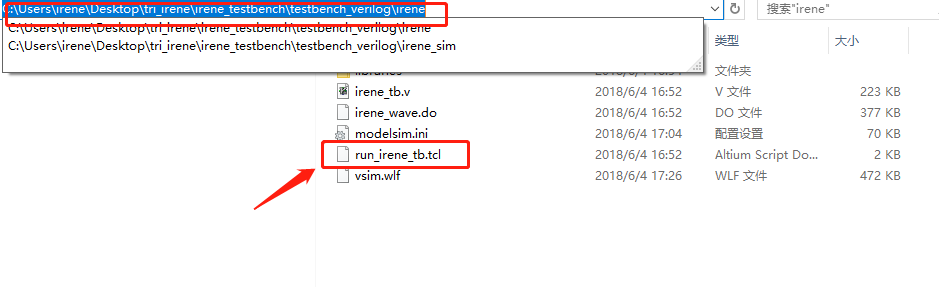

然后运行 “generate_sim_verilog.tcl”或者“generate_sim_vhdl.tcl”,到这里可以关闭quartus这个工程了,然后去打开modelsim,将路径“Change Directory”到“run_irene_tb.tcl”所在的路径

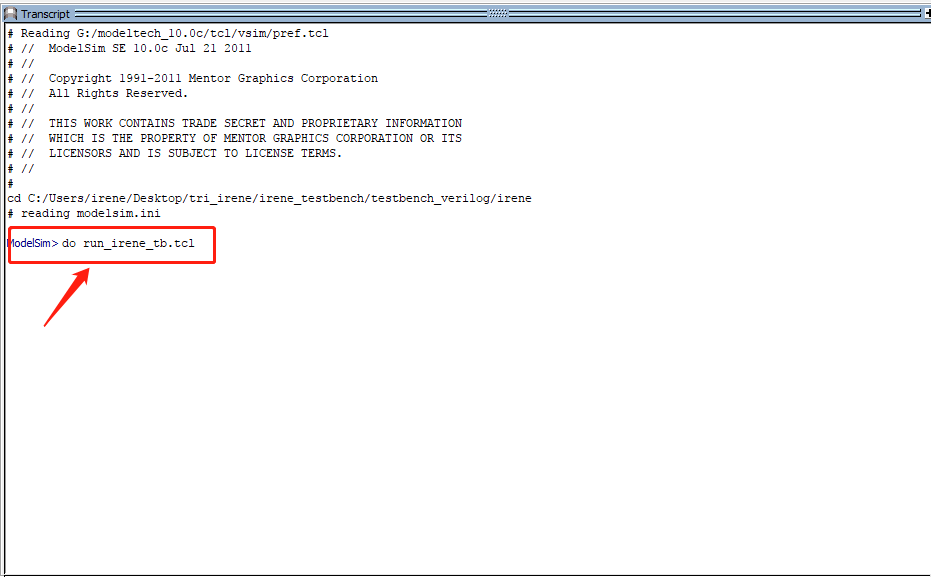

接着在modelsim运行命令框输入“do run_irene_tb.tcl”,按回车键

接下来就不用人为干预了,modelsim 会自动执行直到仿真波形自动输出

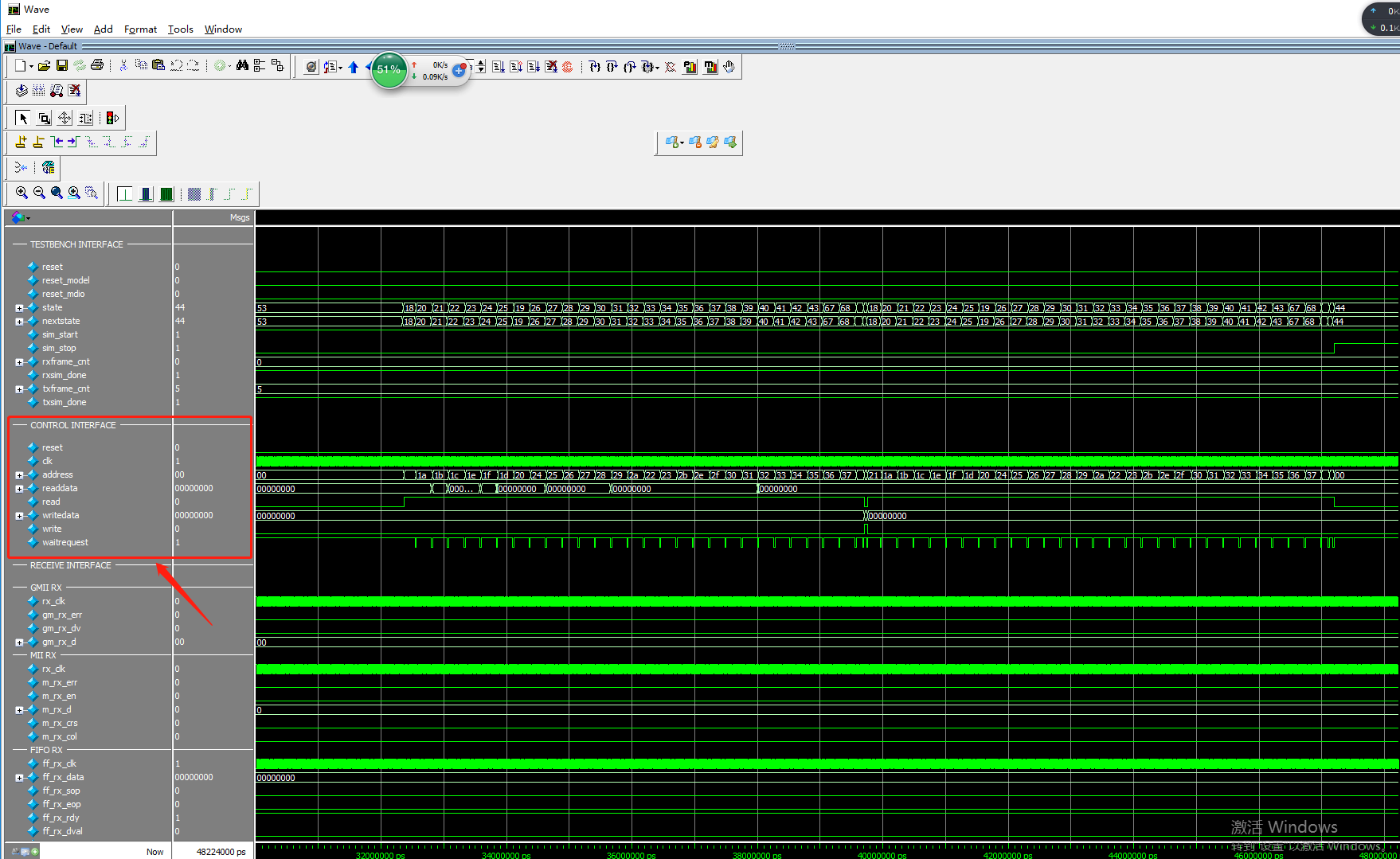

可以重点关注下它的“control interface”时序以及它的用户侧时钟,MAC IP的工作时钟。

至于control interface接口时序比较简单,通过仿真我们可以看到

在waitrequest拉低的时候可以进行读写操作。

接下来简单说一下它的工作时钟:

1)ff_tx_clk:用户侧发送端时钟,

2)ff_rx_clk:用户侧接收端时钟;

MAC IP核工作时钟是125M,接口是8 bit,但是由于IP核内部fifo的隔离,因此ff_tx_clk与ff_rx_clk无须配置为125M,只要满足125M X 8bit = 1G的速率即可。

3)rx_clk: MAC IP RX测时钟125M,是PHY芯片发给IP核的,PHY芯片跟据工作速率从网络中恢复成125M时钟,给IP核。

4)tx_clk: MAC IP TX测时钟125M, 这个时钟可以由PLL产生。

5)gtx_clk: 由pll产生的125M 时钟,送给MAC芯片。

假设时钟源clk是50M,可用一个pll产生两路时钟,一路100M给用户侧ff_tx_clk与ff_rx_clk,一路125M给 MAC IP核tx_clk,然后PHY芯片从网络中恢复成125M时钟给rx_clk。

至此,altera三速以太网IP核仿真结束,后续会陆续补充关于这个ip核的使用。

注:本文未经允许,禁止转载,违者必究。