(原创)Quartus硬件工程路径改变,nios工程该怎么办?

操作系统:Win7 64 bit

开发环境:Quartus II 12.0 (64-Bit) + Nios II 12.0 Software Build Tools for Eclipse

使用Quartus 时,有时候出于备份的考虑,或者从网上下载别人的硬件工程, 硬件工程目录会改变,导致NIOS工程不能找到sopcinfo文件,从而不能进行下一步软件开发。比较笨重的方法是新建一个NIOS工程,然后将原始的NIOS工程源文件添加到这个新工程中。这样的做法比较繁琐,而且新建的新工程需要重新编译BSP工程,带来不必要的麻烦。比较这里介绍一种较为简单的方法。

例如:

原始硬件工程目录(sopcinfo文件所在目录)

D:\_prj\Altera\DE2_70_NIOS_VGA\

NIOS工程目录

D:\_prj\Altera\DE2_70_NIOS_VGA\Software

修改之后的:

新的硬件工程目录(新sopcinfo文件所在目录)

E:\_prjbak\Altera\DE2_70_NIOS_VGA\

新的NIOS工程目录

E:\_prjbak\Altera\DE2_70_NIOS_VGA\Software

1、发现问题

启动NIOS ECLIPSE,将workspace切换到新的NIOS工程目录下,即E:\_prjbak\Altera\DE2_70_NIOS_VGA\Software。这个时候,如果直接编译原工程,会提示找不到sopcinfo文件:

make all Info: Building ../VGA_bsp/ make --no-print-directory -C ../VGA_bsp/ makefile:580: Warning: SOPC File D:\_prj\Altera\DE2_70_NIOS_VGA\DE2_70_SOPC.sopcinfo could not be found.

[BSP build complete]

[VGA build complete]

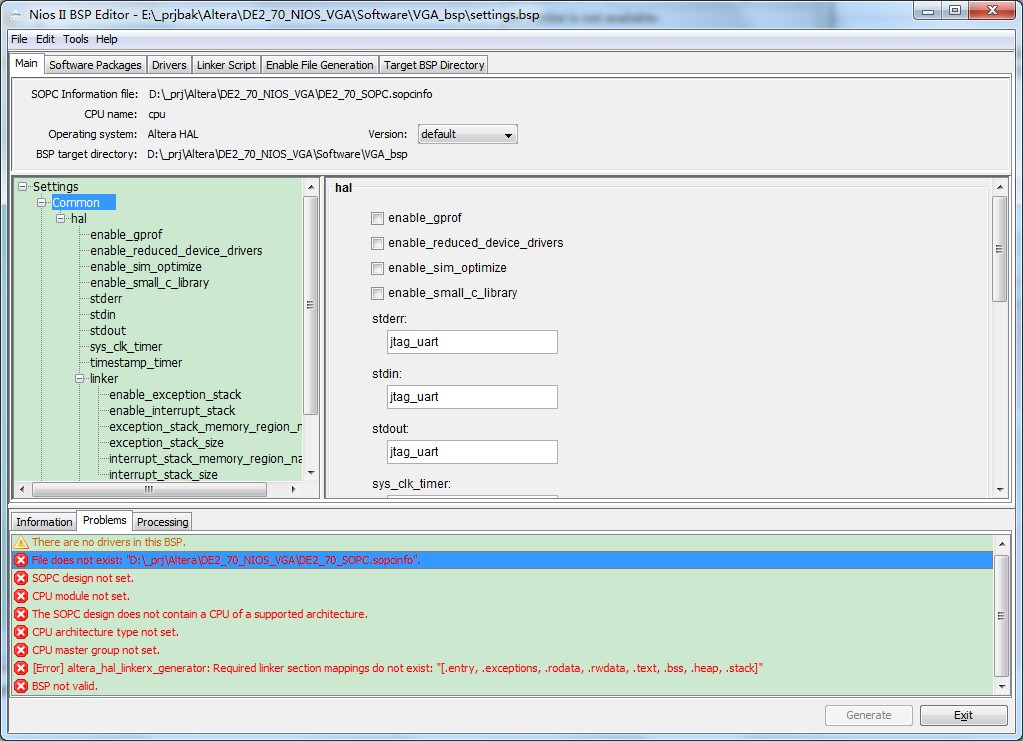

这个时候,如果查看bsp信息,会提示bsp找不到sopcinfo文件和sopc设计,CPU之类的信息同样不会找到了

2、解决问题

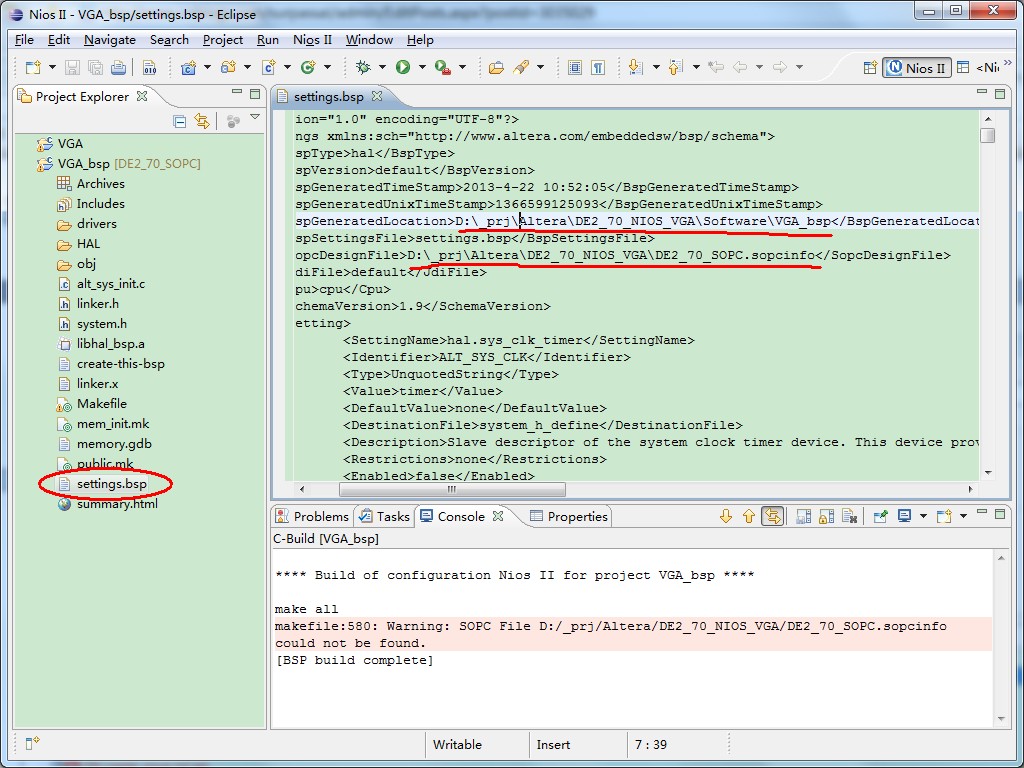

打开bsp工程的settings.bsp文件,这是一个xml格式的配置文件。发现BspGeneratedLocation节点和SopcDesignFile节点分别所指示的BSP生成路径和SOPC设计文件路径均是原有软件工程路径和硬件工程路径:

1 <?xml version="1.0" encoding="UTF-8"?> 2 <sch:Settings xmlns:sch="http://www.altera.com/embeddedsw/bsp/schema"> 3 <BspType>hal</BspType> 4 <BspVersion>default</BspVersion> 5 <BspGeneratedTimeStamp>2013-4-22 10:52:05</BspGeneratedTimeStamp> 6 <BspGeneratedUnixTimeStamp>1366599125093</BspGeneratedUnixTimeStamp> 7 <BspGeneratedLocation>D:\_prj\Altera\DE2_70_NIOS_VGA\Software\VGA_bsp</BspGeneratedLocation> 8 <BspSettingsFile>settings.bsp</BspSettingsFile> 9 <SopcDesignFile>D:\_prj\Altera\DE2_70_NIOS_VGA\DE2_70_SOPC.sopcinfo</SopcDesignFile> 10 <JdiFile>default</JdiFile> 11 <Cpu>cpu</Cpu> 12 <SchemaVersion>1.9</SchemaVersion> 13 <Setting>

...

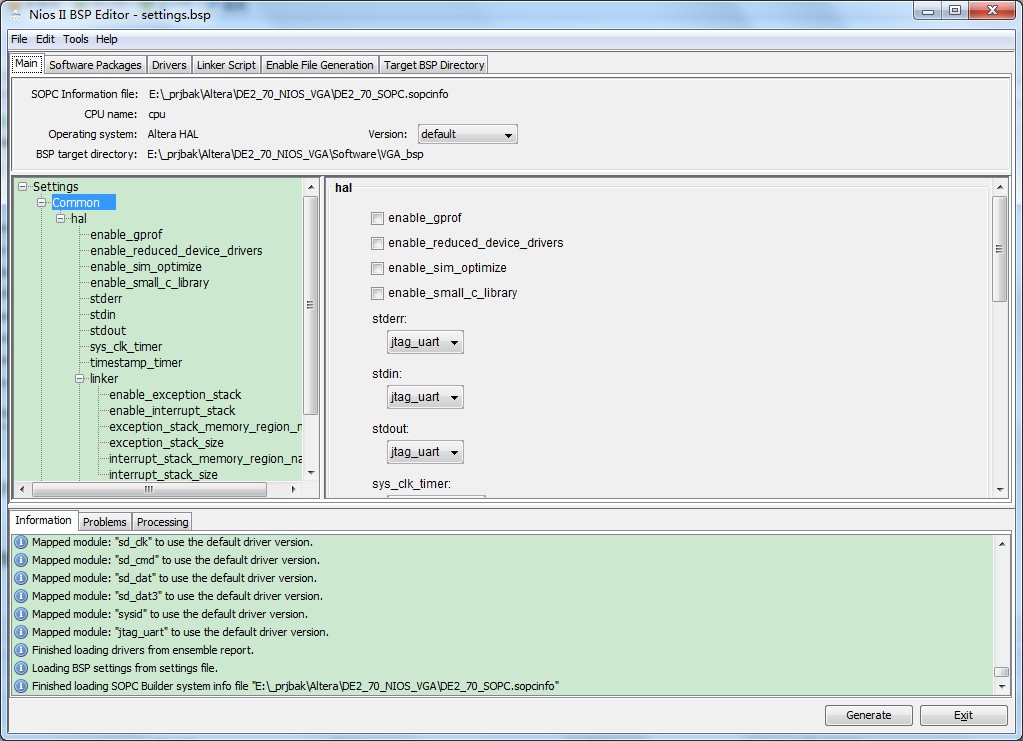

图示:

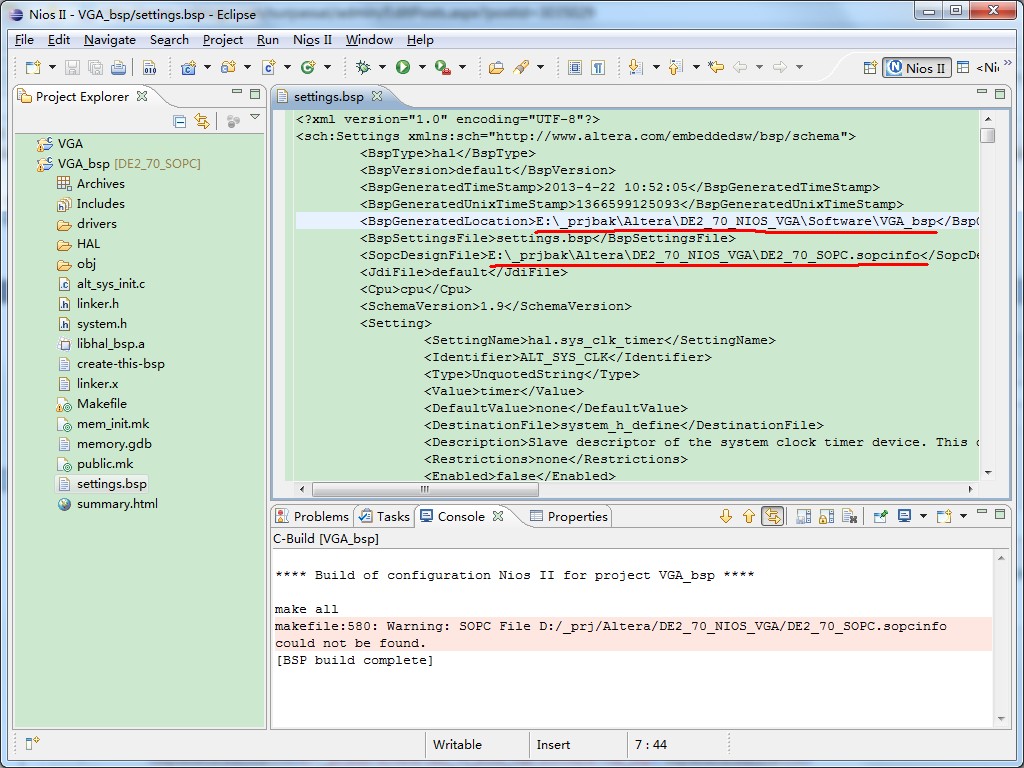

以此将其修改成新的软件工程和硬件工程路径即可。修改后的settings.bsp文件:

1 <?xml version="1.0" encoding="UTF-8"?> 2 <sch:Settings xmlns:sch="http://www.altera.com/embeddedsw/bsp/schema"> 3 <BspType>hal</BspType> 4 <BspVersion>default</BspVersion> 5 <BspGeneratedTimeStamp>2013-4-22 10:52:05</BspGeneratedTimeStamp> 6 <BspGeneratedUnixTimeStamp>1366599125093</BspGeneratedUnixTimeStamp> 7 <BspGeneratedLocation>E:\_prjbak\Altera\DE2_70_NIOS_VGA\Software\VGA_bsp</BspGeneratedLocation> 8 <BspSettingsFile>settings.bsp</BspSettingsFile> 9 <SopcDesignFile>E:\_prjbak\Altera\DE2_70_NIOS_VGA\DE2_70_SOPC.sopcinfo</SopcDesignFile> 10 <JdiFile>default</JdiFile> 11 <Cpu>cpu</Cpu> 12 <SchemaVersion>1.9</SchemaVersion> 13 <Setting>

...

图示:

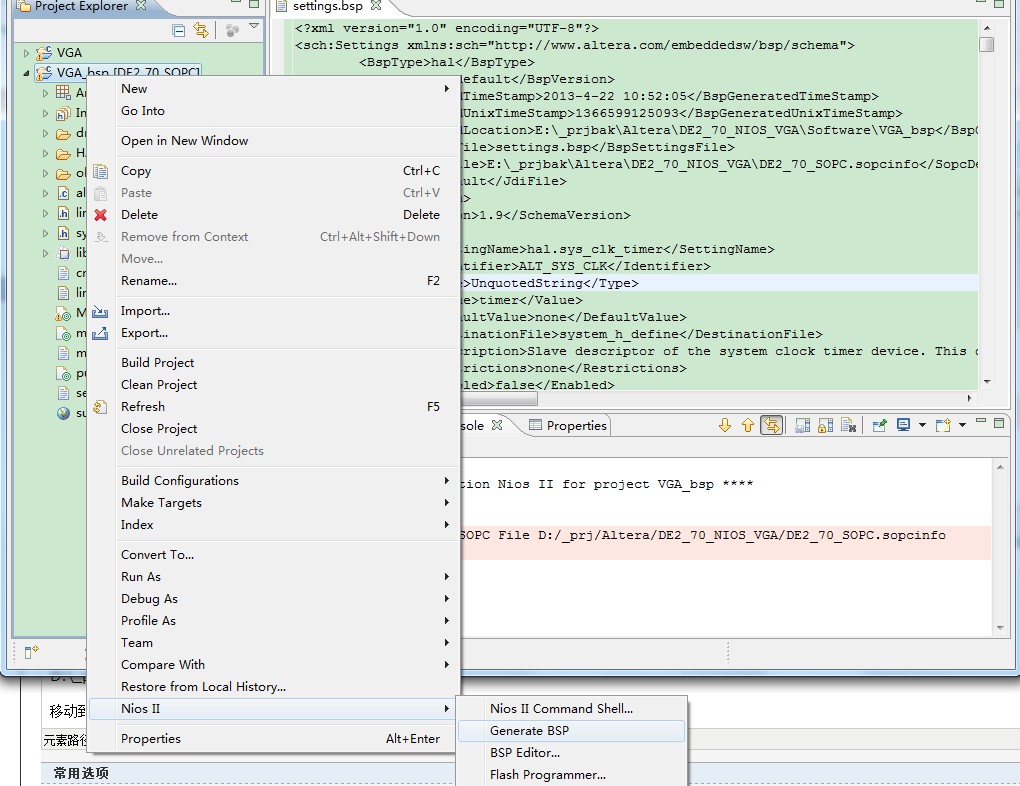

红色部分是修改后的。保存。再重新生成bsp

再查看bsp信息,已经识别到新的sopcinfo文件了

重新编译原工程(如果愿意可以先clean原工程和bsp工程),可以完成编译并生成可执行文件elf

========================

注:这种方法适应于Quartu II 10.0/ NIOS IDE 10.0以后的版本,对于Quartu II 10.0/ NIOS IDE 10.0以前版本,修改的是syslib里面的配置文件system.stf文件。这个文件和settings.bsp类似,也是一个xml文件:

1 <?xml version="1.0" encoding="UTF-8" standalone="no"?> 2 <stf> 3 <project ptf="E:\Sample_SOPC\nios_system.ptf" target="Nios II System Library"> 4 </project> 5 <cpu name="cpu_0"> 6 </cpu> 7 <os_spec clean_exit="yes" direct_drivers="no" exception_stack="no" instruction_emulation="no" name="none (single-threaded)" no_c_plus_plus="no" no_exit="no" profiling="no" small_footprint="no" sopc_component_dir="altera_hal" stack_checking="no" stderr="jtag_uart_0" stdin="jtag_uart_0" stdout="jtag_uart_0"> 8 <sys_defines> 9 <define name="alt_max_fd" quote="no" value="32"/> 10 <define name="alt_sys_clk" quote="no" value="none"/> 11 <define name="alt_timestamp_clk" quote="no" value="none"/> 12 </sys_defines> 13 <make_macros> 14 <macro name="alt_sim_optimize" quote="no" value="0"/> 15 </make_macros> 16 </os_spec> 17 <link_spec auto_gen_script="yes"> 18 <script name="none"> 19 <section memory="onchip_memory2_0" name=".text"/> 20 <section memory="onchip_memory2_0" name=".rodata"/> 21 <section memory="onchip_memory2_0" name=".rwdata"/> 22 </script> 23 </link_spec> 24 </stf>

只需要第三行project ptf节点内容改成新硬件工程的ptf文件路径就可。