IIC 协议总结

第1章 IIC协议

1. 协议基础

I²C即Inter-Integrated Circuit(集成电路总线),它是一种串行通信总线,使用多主从架构,由飞利浦公司在1980年代设计出来的一种简单、双向、二线制总线标准。多用于主机和从机在数据量不大且传输距离短的场合下的主从通信。主机启动总线,并产生时钟用于传送数据,此时任何接收数据的器件均被认为是从机。

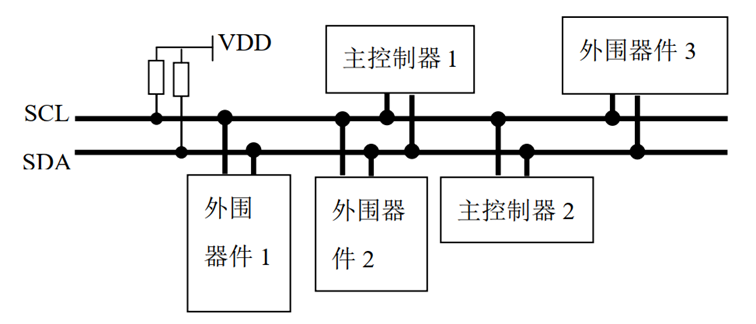

I²C总线由数据线SDA和时钟线SCL构成通信线路,既可用于发送数据,也可接收数据。在主控与被控IC之间可进行双向数据传送,数据的传输速率在标准模式下可达100kbit/s,在快速模式下可达400kbit/s,在高速模式下可达3.4Mbit/s,各种被控器件均并联在总线上,通过器件地址(SLAVE ADDR,具体可查器件手册)识别。I²C总线物理拓扑结构图如下所示:

2. 数据的有效性及起始结束条件

在I2C器件开始通信(传输数据)之前,串行时钟线SCL和串行数据线SDA线由于上拉的原因处于高电平状态,此时I2C总线处于空闲状态。

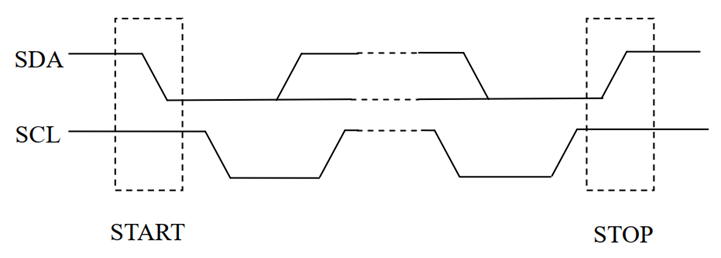

如果主机想开始传输数据,只需在SCL为高电平时将SDA线拉低,产生一个起始信号,从机检测到起始信号后,准备接收数据,当数据传输完成,主机只需产生一个停止信号,告诉从机数据传输结束,停止信号的产生是在SCL为高电平时,SDA从低电平跳变到高电平,从机检测到停止信号后,停止接收数据。

起始信号之前为空闲状态,起始信号之后到停止信号之前的这一段为数据传输状态,主机可以向从机写数据,也可以读取从机输出的数据,数据的传输由双向数据线(SDA)完成。停止信号产生后,总线再次处于空闲状态。

起始:SCL为高时,SDA由高拉低。

停止:SCL为高时,SDA由低拉高。

3. 数据传输模式

数据传输

SCL为低时,SDA运行变化。

SCL为高时,SDA数据锁存。

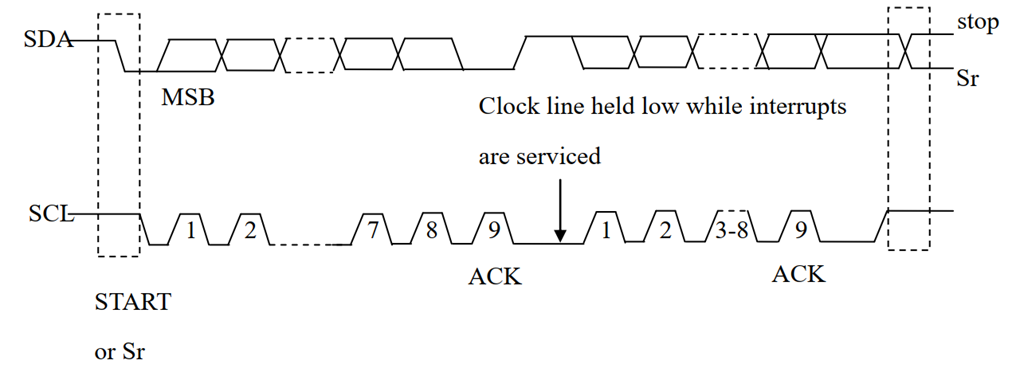

数据的前七位都是地址,最后一位为传输方向位(R/W),若最后一位为 0,表明主器件向从器件的一个写过程,最后一位是 1 时,则代表着从器件向主器件的一个写过程,发送器发送完一个字节数据后,接收器必须发送一位应答信号(ACK)来回应发送器。

数据传输过程中假设从机要处理其他的事物,无法接收和发送数据,从机可以将 SCL 线拉低,让主机等候,直到从机完全预备好接收下一条数据信息时,放开 SCL 线,并接着传输数据。 当所有的数据传输完毕后,主机会产生一个停止信号。

器件地址

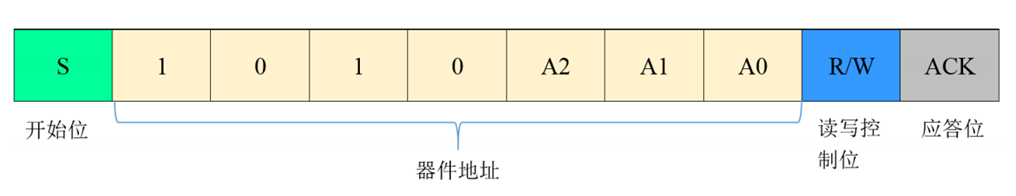

进行数据传输时,主机首先向总线上发出开始信号,对应开始位S,然后按照从高到低的位序发送器件地址,一般为7bit,第8bit位为读写控制位R/W,该位为0时表示主机对从机进行写操作,当该位为1时表示主机对从机进行读操作,然后接收从机响应。对于AT24C64来说,其传输器件地址格式如下图所示。

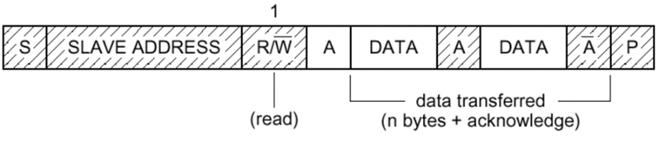

IIC写

IIC读

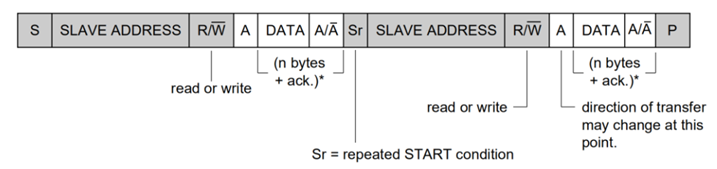

读写混合

4. 时钟同步

I2C协议规定允许一个或者多个主器件存在,每个器件都能生成自己不同的时钟。为了实现仲裁就需要统一的时钟系统,把各个器件所生成的频率和相位不一致的时钟,统一为同一时钟的过程就是时钟同步。

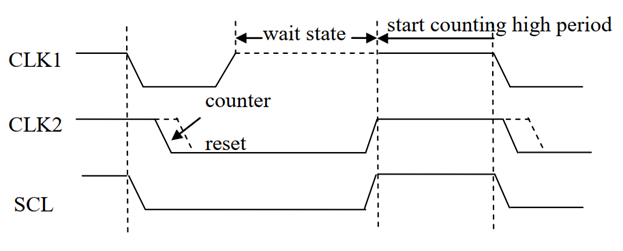

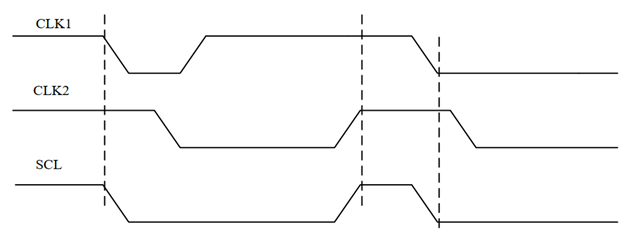

以I2C总线上挂两个主器件为例,如图所示,CLK 1和CLK2是同步前的时钟波形,CLK1和CLK2组成了一个与门,而同步的过程也就是逻辑与过程,即SCL等于CLK 1&CLK2。

当CLK1从1变到0,SCL也从1变成0,当CLK1从0变成1时,此时的CLK2处于低电平状态,与CLK1相与之后,SCL仍为0。当CLK2从0成1,2和CLK1同时处于高电平,在相与之后,SCL仍然保持高电平。如图所示,这样的同步过程形成了单一时钟SCL,SCL低电平时刻长度的大小,由低电平有效时刻最长的节点来决定,而SCL高电平时刻的长度,则取决于保持高电平时刻最小的那个节点,这就是时钟同步的过程。

5. 仲裁

当I2C总线上挂载了超过一个主机,并且这些主机都有控制总线的功能,若他们同时传输数据,将会出现多主机的总线竞争问题,I2C总线规定用SDA线和SCL线的线与逻辑来解决,即当一个主机在发送过程中监测到自己发送的状态和总线状态不一致,将退出仲裁,这个过程对其他主机传输不产生任何影响,最终仲裁出一个主机在12C总线上进行传输。

总线仲裁也是基于总线的与逻辑,主机每发送完一个数据都会和 I2C总线上的状态比较,检测一下总线上的状态和主机发送的信号是否一样,如果一样那么将继续发送,如果不是将退出竞争。

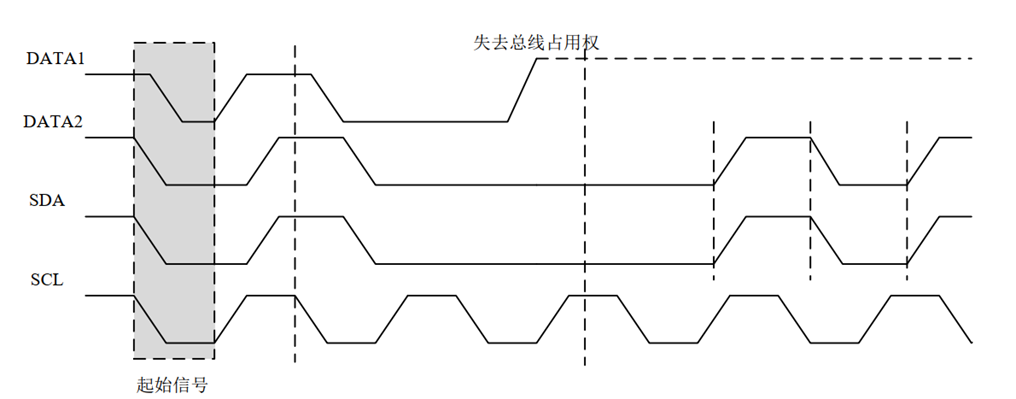

SDA线上所执行的总线仲裁与SCL上的时钟同步过程一样,DATA1的数据线和DATA2的数据线组成了一个与门,并且分别向主节点总线发送数据信号,SDA线就是线与之后总线上呈现的数据信号。

当起始信号后,DATA 1 和 DATA 2 两个主节点都发送了高电平,这时的 SDA 线的信号也为高电平,DATA 1 和 DATA 2 检测到 SDA 总线上的数据和自己发送的数据一样,将继续发送。在第二个时钟周期, DATA 1 和 DATA 2 都发送了低电平,SDA上也呈现低电平,继续发送。到了第三个时钟周期的时候, DATA 1 发送高电平, DATA2 发送低电平,线与之后 SDA 线呈现低电平,此时 DATA 1 检测到总线上的数据和自己的数据不一致,失去了占用权,断开传输级。这样 DATA 2 就控制了总线,整个流程中不会出现数据的遗失。 SDA 线上与 DATA 2 传输的数据一样,DATA 1 在断开传输级之后,变成了从机的接收状态。

6. 时钟延展

时钟延展:通过将 SCL 线保持在低电平来暂停传输。在 SCL 再次拉高之前,传输无法进行。

从机通过将 SCL 线拉低,强制主机进入等待状态。

时钟延展功能是可选的,非必须。

byte level

时钟延展导致需要更多时间来存储接收到的字节或准备另一个要传输的字节

bit level

通过延长每个时钟低电平周期来降低总线时钟。任何主机的速度都与该设备的内部运行速度相适应。

在 Hs mode,只能使用 byte level,也就是只能在传输完一个字节(8bits)后拉低 SCL 进行时钟延展。在 Standard-mode 和 Fast-mode,既可以 byte level 也可以 bit level,bit level 意思是哪怕你之传输了 2 bits ,从机也可以拉低 SCL 线进行时钟延展,临时暂停传输。

I2C 主设备始终控制着时钟线 SCL,不论是往设备写还是从设备读。一般情况下,如果操作对象是 EEPROM 或者其他简单设备而言,无所谓,但是,如果从设备是处理器,在接到主机命令后要去处理一些运算然后得出结果返回给主机。这个时候可能造成来不及处理。怎么办?这时,从设备会主动控制时钟线把它拉低!直到数据准备好之后再释放时钟线,把控制权交还给 MASTER。这也是 I2C 通信系统中,从机唯一能控制总线的时候!

本文作者:superego-zhang

本文链接:https://www.cnblogs.com/superego-zhang/p/17531898.html

版权声明:本作品采用知识共享署名-非商业性使用-禁止演绎 2.5 中国大陆许可协议进行许可。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步