快时钟域到慢时钟域

个人导航网站:yun916831.github.io

1 将快速信号同步到慢速时钟域

如果CDC 信号在时钟域之间传递时无法漏采,那么在时钟域之间传递信号时考虑信号宽度或同步技术就很重要。

与同步器相关的一个问题是,来自发送时钟域的信号在被采样之前可能会更改值两次,或者可能太靠近较慢时钟域的采样边沿。任何时间信号从一个时钟域发送到另一个时钟域时都必须考虑这种可能性,并且必须确定漏采的信号是否重要的问题。

当不允许漏采时,有两种一般方法可以解决该问题:

一种开环解决方案,可确保无需确认即可捕获信号。

需要确认收到跨越CDC 边界的信号的闭环解决方案。

1.1 时钟域之间可靠的信号传递的要求

一般来讲,快时钟域采慢时钟信号是没有问题的,基本都能采到;但是慢时钟域采快时钟信号则需要分情况讨论。

如果较快时钟域的频率是较慢时钟域的1.5 倍(或更多),则将较慢的控制信号同步到较快的时钟域通常不是问题,因为较快的时钟信号将对较慢的CDC 信号采样一次或多次。将较慢的信号采样到较快的时钟域比将较快的信号采样到较慢的时钟域引起的潜在问题更少,设计人员可能会利用这一事实,通过使用简单的两个触发器同步器在时钟域之间传递单个CDC 信号。

1.1.1 “三边”要求

“三边”要求的实质是要保证信号足够长—能被接受时钟域采到。

当通过双触发器同步器在时钟域之间传递一个CDC 信号时,CDC 信号必须比接收域时钟周期宽1.5倍。即“输入数据值必须在三个目标时钟边沿保持稳定”。

对于特别长的源和目标时钟频率,这个要求可能会安全地放宽到接收时钟域周期时间的1.25倍或更少,但“三边”指南是最安全的初始设计条件,并且通过使用SystemVerilog 断言比在仿真期间动态测量CDC 信号的分数宽度更容易证明。“三个边沿”要求实际上适用于开环和闭环解决方案,但闭环解决方案的实现会自动确保至少检测到所有CDC 信号的三个边沿。

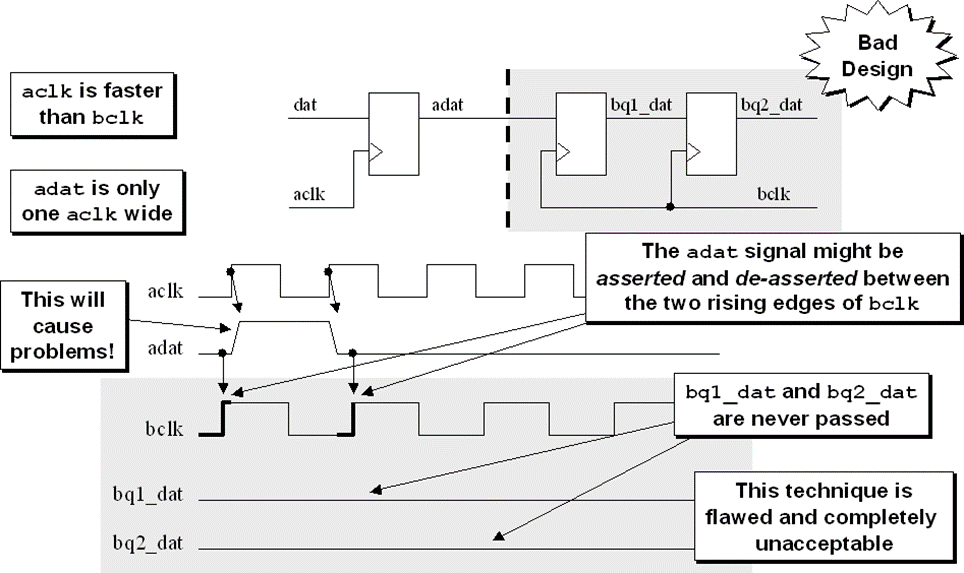

1.2 问题—传递快速CDC脉冲

考虑存在严重缺陷的情况,即发送时钟域的频率高于接收时钟域,并且CDC 脉冲在发送时钟域中只有一个周期宽。如果CDC 信号仅脉冲一个快时钟周期,则CDC 信号可能会在较慢时钟的上升沿之间变高和变低,而不会被捕获到较慢时钟域中,如图8 所示。

此类情况就是慢采快直接采不到的可能性。

Figure 8 - Short CDC signal pulse missed during synchronization

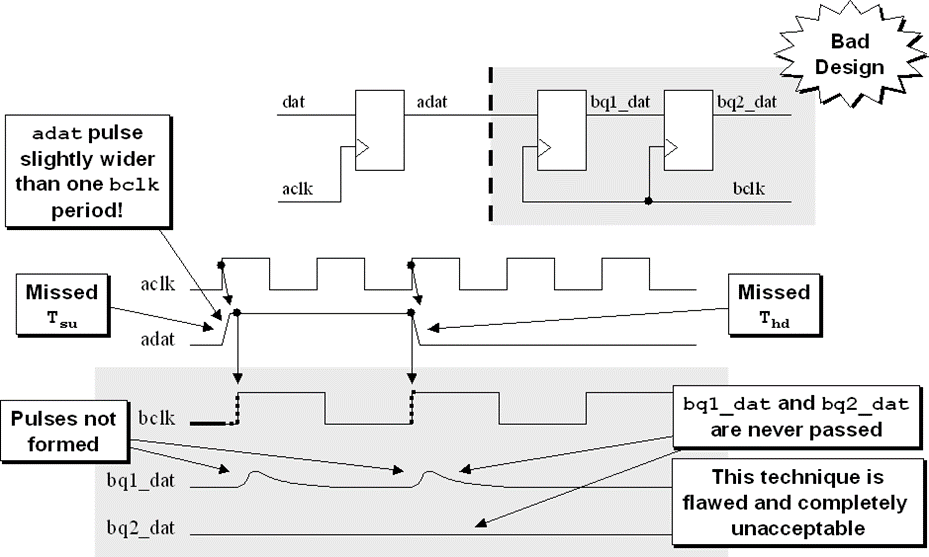

1.3 问题—采样一个长 CDC 脉冲—但不够长!

此类情况就是慢采快,虽然不是单周期脉冲信号了,但任然无法被慢时钟域采到。

考虑一些不直观和有缺陷的情况,其中发送时钟域向接收时钟域发送一个脉冲,该脉冲比接收时钟频率的周期略宽。在大多数情况下,信号将被采样并通过,但CDC 脉冲变化过于接近接收时钟域的两个时钟上升沿,从而违反第一个时钟沿上的建立时间的可能性很小但确实存在并且违反第二个时钟边沿的保持时间并且不形成预期的脉冲。这种可能的故障如图9 所示。

Figure 9 - Marginal CDC pulse that violates the destination setup and hold times

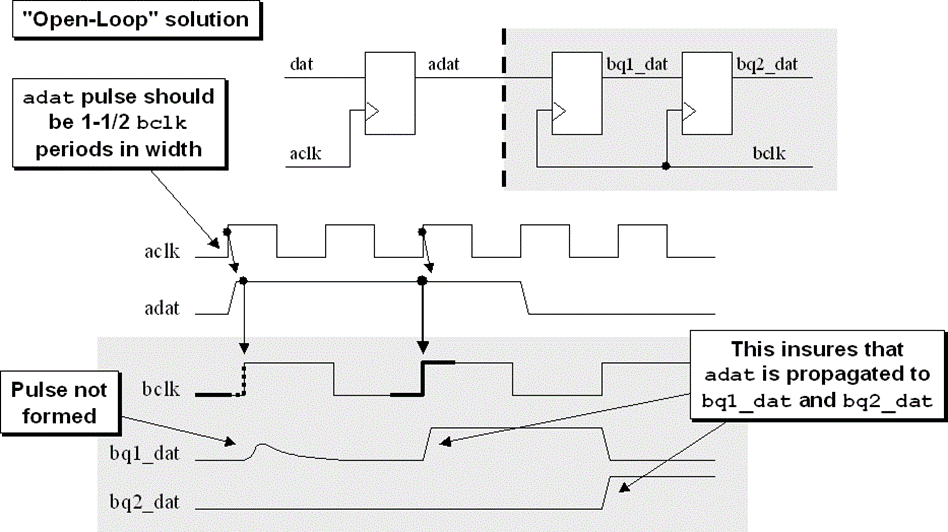

1.4 开环解决方案—使用同步器采样信号

不需要知道接收时钟域的边沿信息,只要在发送域保证发送信号的长度就可以。

该问题的一个可能的解决方案是在超过采样时钟周期时间的一段时间内置位CDC 信号,如图10 所示。最小脉冲宽度是采样时钟周期的1.5 倍。假设CDC 信号将被接收器时钟至少采样一次,也可能采样两次。

当相对时钟频率固定并正确分析时,可以使用开环采样。

优点:开环解决方案是通过CDC 边界传递信号的最快方式,不需要对接收信号进行确认。

缺点:与开环解决方案相关的最大潜在问题是另一位工程师可能会将解决方案误认为通用解决方案,或者设计要求可能会发生变化,并且工程师可能无法重新分析原始开环解决方案。通过向模型中添加SystemVerilog 断言以检测输入脉冲是否未能超过“三个边沿”设计要求,可以将这个问题最小化。

此方法的本质是将脉冲信号拓宽,实际上就是将快信号变为比满时钟域更慢的信号—降频。此类方法的缺陷是不够通用,若慢时钟变得更慢,则无法采样了。

Figure 10 - Lengthened pulse to guarantee that the control signal will be sampled

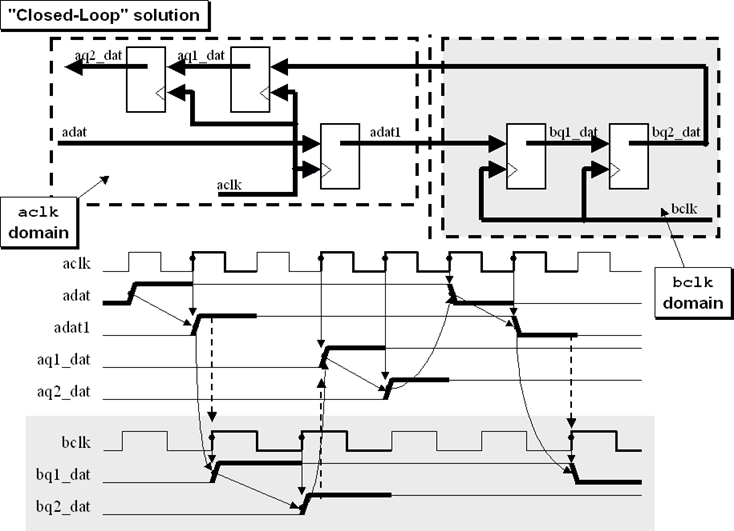

1.5 闭环解决方案—使用同步器采样信号

采用反馈信号自动延长快时钟域的信号,第二个可能的解决方案是发送一个使能控制信号,将其同步到新的时钟域,然后将同步信号通过另一个同步器传回发送时钟域作为确认信号。

优点:同步反馈信号是一种非常安全的技术,可以确认第一个控制信号已被识别并采样到新的时钟域中。

缺点:在允许控制信号改变之前,在两个方向上同步控制信号可能存在相当大的延迟。

此方法的本质是先降频,后握手。通过接受时钟域反馈的信号来决定降频到什么程度。

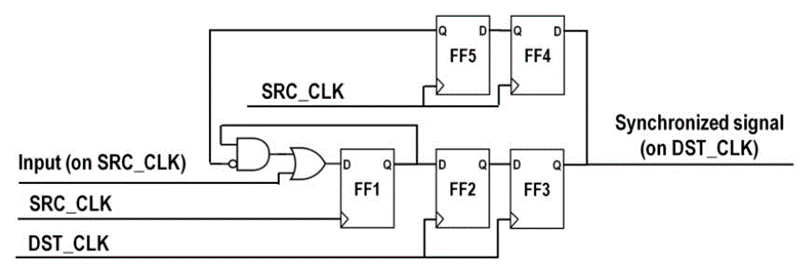

Figure 11 - Signal with feedback to acknowledge receipt

将A时钟域要传输的信号打一拍送到B域中进行双reg同步,同步之后的信号在反馈会A中,A中再进行双reg同步,当A域中反馈同步信号变为高时才将被采信号拉低,这样的方法时比较稳妥的,但是会有更多的延时,并且需要更多同步reg。 例如下图就是采用闭环延长信号的一个方法:

FF1由源时钟驱动,输入变高,FF1输出变高。FF1的Q输出反馈通过与门和或门保证了在FF5输出为0时,只要FF1输出变高,FF1输出就一直保持高。直到FF3同步输出变成1后,FF5输出变成1,与门输出0。这时只要输入为0,FF1输出即为0。

参考:Clock Domain Crossing (CDC) Design & Verification Techniques Using SystemVerilog

https://zhuanlan.zhihu.com/p/359327167

https://wuzhikai.blog.csdn.net/article/details/122874278

https://www.cnblogs.com/lyc-seu/p/12441366.html

本文作者:superego-zhang

本文链接:https://www.cnblogs.com/superego-zhang/p/17499419.html

版权声明:本作品采用知识共享署名-非商业性使用-禁止演绎 2.5 中国大陆许可协议进行许可。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步