HDLBits — Edge Capture Register & Dual-edge triggered flip-flop

Edge Capture Register

要求

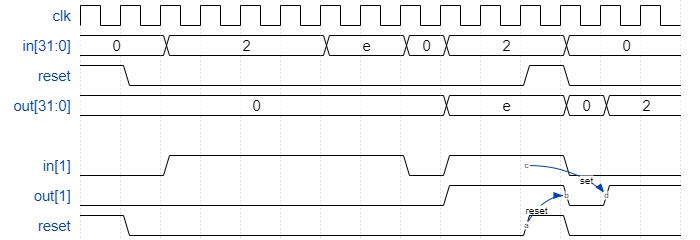

对于32bits向量中的每一位,当输入信号由1变为0时进行检测(即下降沿检测)

其中检测表示在复位信号(同步)到达前,输出将保持1。 每一个输出位就像一个RS触发器,即当对应位出现1 to 0的变化时,输出位将置1

而当reset信号为高电平,输出位将在下一个时钟的上升沿被复位。如果信号的下降沿和reset事件在同一时刻发生,将优先执行复位操作

在下图示例波形的最后4个时钟周期中,reset事件比set事件早一个周期出现,因此这里没有前述冲突。 为清楚起见,in[1]和out[1]在波形中分别单独显示

解析

首先电路需要检测下降沿,其次在检测到的下降沿所在位进行置位操作,同时还不能影响到其他已置位的输出位

| out 使之没有下降沿信号保持高电平,这是对 Capture的理解

Dual-edge triggered flip-flop

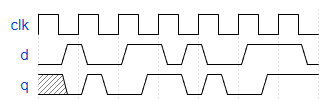

触发器分为单边沿触发器(SETFF)和双边沿触发器(DETFF)。相对于单边沿触发器,双边沿触发器在时钟的上升沿和下降沿均能采样数据。双边沿触发器的工作效率是单边沿触发器的2倍T7。

相对于单边沿触发器,输入信号相同时,双边沿触发器只需50%的时钟频率就可实现等效的电路功能。或者在相同的时钟频率下,双边沿触发器的数据吞吐量是单边沿触发器的2倍。

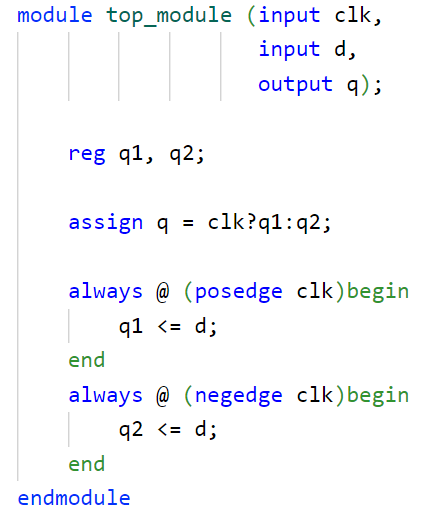

MUX型双边沿触发器

这种方法简单明了,但因为触发器Tc_to_q延时的存在,输出波形会产生glitch,即p、q的值还没更新,就已经执行了assign q = clk? q1:q2。

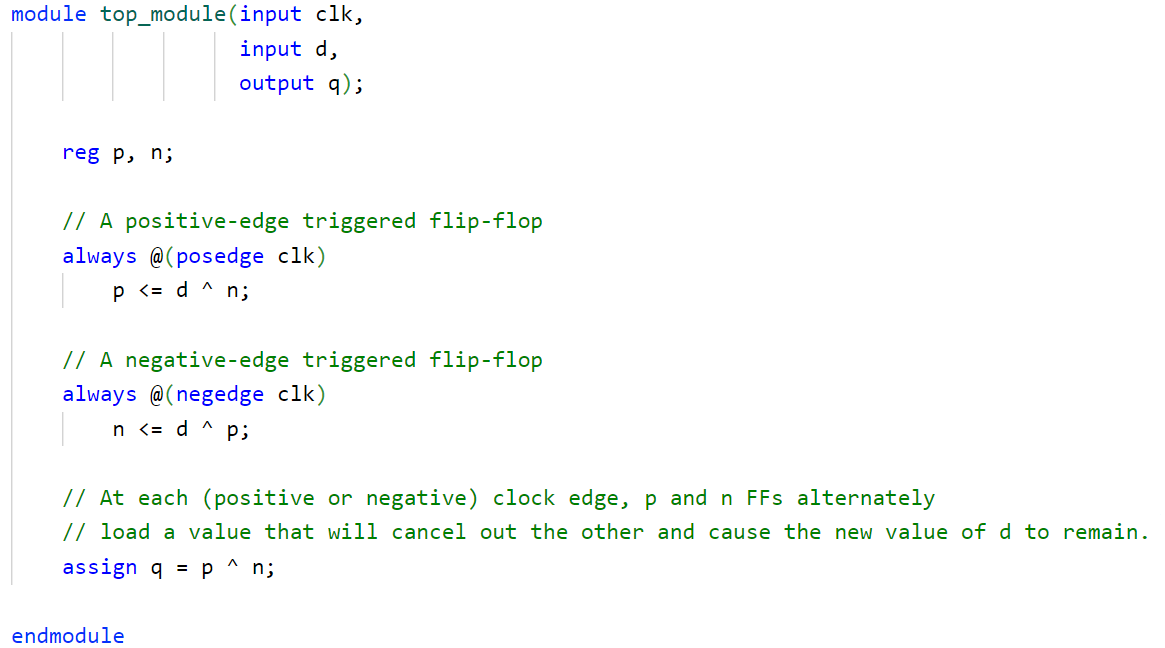

XOR

这种方法不会产生毛刺,但使用了三个异或门,电路较为复杂

参考:

https://hdlbits.01xz.net/wiki/Edgecapture

https://zhuanlan.zhihu.com/p/61695679

https://zhuanlan.zhihu.com/p/369143714