信号完整性与高速PCB设计(1):过冲、欠冲、振铃

Hello,大家好,《高速数字设计》(基础篇)目前已经初步完成框架规划,经再三考量还是决定使用有章无节的组织方式。全书预计约26章,每章约5000字,目录与《三极管应用分析精粹:从单管放大到模拟集成电路设计》相似,后续还要对框架进行优化,接着才会正式进入细化阶段,敬请期待哈~~

言归正传,从今天开始,咱们讨论一些关于信号完整性(Signal Integrity, SI)与高速PCB设计相关的内容,这些内容基本上也会出现在《高速数字设计》一书中,本系列文章就从过冲(overshoot)、欠冲(undershoot)、振铃(ringing)等概念切入。

值得一提的是,文章与图书的撰写思路完全不一样,文章更侧重形象易懂,图片会多一些,而且会尽量避免数字公式或计算(说得好听点,不需要动脑就可以基本看懂~~),图书更侧重体系的完整与阐述的详尽,毕竟阅读的载体不一样,读者的耐心也不尽相同。

先来看看下图所示的脉冲信号,其在“低电*往高电*切换时”出现了超过正常高电*的上冲波形,也称为高电*过冲。紧接着又会下冲到低于正常高电*的下冲波形,也称为高电*欠冲,而这种“从信号过冲开始逐渐减小直至最后消失的现象(即阻尼振荡)”则称为振铃。脉冲信号在“高电*往低电*切换时”也会出现相似波形,此处不再赘述。

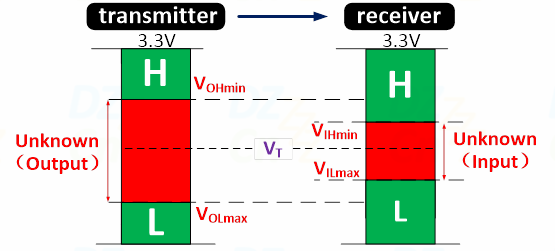

信号欠冲的主要危害是可能会导致接收逻辑错误判断输入电*值。我们知道,数字逻辑本质上可以理解为一个比较器,即当高于某值时为高电*,低于某值时为低电*。但是,与真正的比较器有所不同是,高低电*的两个比较值并不是相同的,这两者之间存在一个未知区域(Unknown Region),在这个区域的电*可能判断为高或低,如下图所示:

以最简单的CMOS反相器为例,其由下侧N沟道场效应管(NMOS)与上侧P沟道场效应管(PMOS)组合而成。当输入为低电*(L)时,上侧PMOS管导通将输出上拉为高电*(H),当输入为高电*(H)时,下侧NMOS管导通将输出下拉为低电*(L),如下图所示:

通常我们简单地认为,所谓的“输入高低电*”,是以MOS管的阈值电压VT值为参考。但实际上,VT值存在一定的分散性,而且会受到外界因素的影响(例如,温度),这也就意味着,对于VT值附*的电*值,有些反相器有时可能会判断为高电*,而另外一些则可能会判断为低电*。因此,为了保证接收端能够正确判断逻辑,发送端输出的低电*最大值(VOLmax)必须比VT值更低,而输出的高电*最小值(VOHmin)必须比VT值更高,而VOLmax与VOHmin之间则是未知区域,发送端输出的电*不允许进入该区域,如下图所示:

回过头来,如果信号欠冲过大,正常的高电*或低电*就有可能进入未知区域,也就存在逻辑误判的可能,这在数字系统中是不允许出现的,如下图所示:

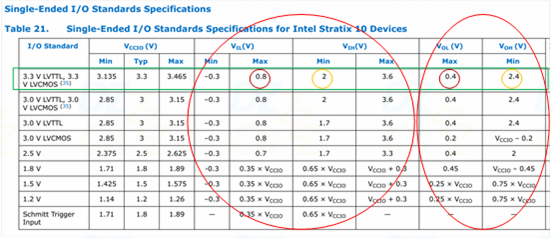

以Intel Stratix10 FPGA为例(Stratix原为Altera公司针对高端应用的FPGA系列,后来Altera被Intel收购),部分单端(Single-Ended)IO电*标准如下表所示。以3.3V LVTTL/LVCMOS为例,逻辑输出低电*的最大值(VOLmax=0.4V)必然会小于“接收方能够正确判断输入为低电*”的最大值(VILmax=0.8V),而输出高电*的最小值(VOHmin=2.4V)必然会大于“接收方能够正确判断输入为高电*”的最小值(VIHmin=2V)。

与信号欠冲不同,过冲并不会导致逻辑判断错误,但却可能给芯片带来潜在的累积性伤害,从而缩短其工作寿命,严重者可能会损坏芯片。一般来讲,过冲越高,持续时间(Duration Time, DT)越长,器件寿命会越短。同样以Intel Stratix10 FPGA为例,其允许最大过冲持续时间如下表所示。

需要注意的是,“过冲持续时间”的表达方式为“正常使用时的芯片寿命的百分比”。从方便理解的角度,基本思路是这样:以“IO应用在正常直流电压的芯片寿命”为基准(此处假设直流电压以简化描述),其在更高直流电压(假设为VX)应用下的寿命会缩短(假设为TX),而过冲通常是短暂性的,但“超过电*Vx的过冲持续时间”的总和仍然还是TX。

在前述思路下换另一个角度,如果想要在某个过冲值的条件下仍然保持基准寿命,那么相应的过冲持续时间必然需要受到限制。就好比一个人正常工作强度时可持续10小时(基准寿命),当工作强度更大时可持续5小时(一定过冲应用时的总寿命),如果想让它的工作时间跨度仍然为10小时(基准寿命),则需要保证更多的休息时间(降低过冲持续时间)。因此,当过冲越大时,表格中相应的持续时间就越小。当然,过冲过大(表格中为大于VCCIO+0.95)则可能会损坏芯片,这是不允许的。

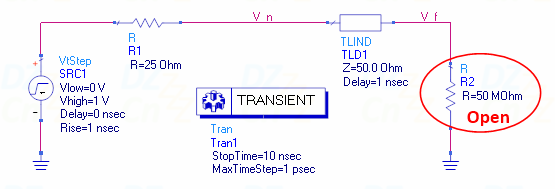

最后,我们可以使用ADS仿真一下振铃现象,相应的仿真电路如下图所示。其中TLD1是一个可以指定特性阻抗与传播延时大小的传输线(此处保持默认的50欧姆与1ns),TLD1右侧连接了一个50M欧姆的大电阻负载R2(表示开路),左侧串联一个25欧姆的电阻(R1),可以将其理解为信号源内阻。SRC1是一个阶跃信号源(幅值为1V,上升时间为1ns),用来模拟一个脉冲上升沿。因为我们要观察传输线两端(靠*信号源的*端节点V_n与靠*负载的远端节点V_f)的瞬时波形,所以添加了一个“TRANSIENT”控件,仿真时长为10ns,分析时间最大步长为1ps。

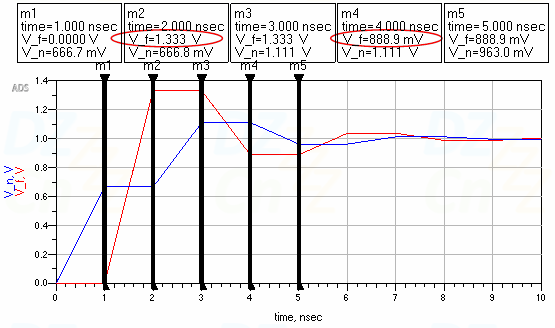

相应的仿真波形如下图所示,其中红色曲线为负载两端的波形,其中出现了超过信号源幅值(1V)的电*(1.333V, m2),对应本文所讨论的过冲,而(888.9mV, m4)则为欠冲。