硬件工程师经典面试题(6):高速数字信号串联匹配电阻的阻值应该多大?

Hello,大家好,首先表达一下歉意,有段时间没有更新《电感应用分析精粹》的撰写进度了,这主要是因为在第2章撰写过程中触发的灵感颇多(真可谓有如神助,不要打我~~),导致总字数超过4万,因此偶决定将其拆分为2章(现在总6章)。

图书架构随时会在撰写过程中不断优化,因为写作过程也是自我总结的过程,不少以往未曾加以重视的知识点一旦扩展开来,也会发现更多令人惊喜的关键枢纽,这些内容在同类图书中未曾涉及(或一笔带过,语焉不详),将其添加进来对加强图书的思想纵深有着非凡的意义,敬请期待哈~~

今天来继续讨论下一个经典面试题:

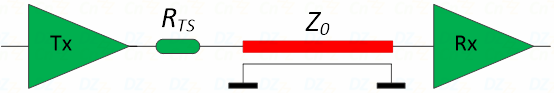

如下图所示,假设驱动端Tx的输出阻抗约为20~30欧姆(输出高电平与低电平时的阻抗不同),传输线特性阻抗Z0为50欧姆,请问串联匹配电阻RTS应该如何取值?

这个题目,知道的同鞋会觉得很简单,不知道的打死也想不出来。技术难点就是这样,其实就是一层薄纸而已,但是否有能力将其捅破就因人而异了。

此题是高速数字电路设计与高速PCB设计实践中最基础的题目,在源端(驱动端)串联匹配电阻也是最常见的解决方案,阅读过《三极管应用分析精粹:从单管放大到集成电路设计》(以下简称“三极管”)一书的同鞋应该很容易回答,其中对方波信号反射产生的振铃现象进行了非常详细的计算,还手工画出了相应的图形,最后还使用Multisim软件平台仿真与手工计算结果对比。

言归正传,高速信号线上的阻抗匹配是为了使信号反射最小化。换句话说,在传输过程中应该让高速信号看到的阻抗稳定。传输线阻抗为50欧姆,那么串联匹配电阻与源端的电阻之和也应该为50欧姆,所以相应的阻值在20~30欧姆之间,一般取25欧姆左右即可。

接下来作为扩展,我们来看看阻抗不匹配可能会对信号带来什么影响。假设源端现在处于阻抗匹配状态,当高速信号从源端输出时,其输出阻抗可以理解为50欧姆(输出阻抗与源端串联电阻之和),之后看到50欧姆传输线,所以会对其分压,即注入到传输线上的电压只有信号源的一半。当信号到达不匹配的终端(接收端)后就会产生一定的反射电压。反射电压经传输线再次返回到源端后,看到的仍然是50欧姆(输出阻抗与源端串联电阻之和),至此,反射电压才会消失。

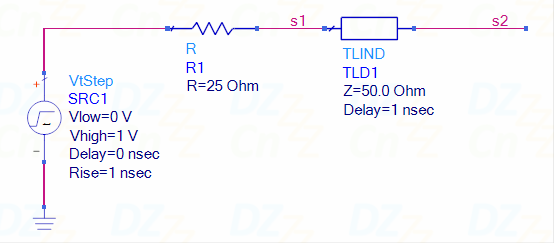

我们可以用ADS软件来仿真一下,相应的仿真电路如下图所示。其中,TLD1是一个可以指定特性阻抗与传播延时大小的传输线,此处保持默认的50欧姆与1ns,与《三极管》一书中一致。TLD1右侧未接负载(用高输入阻抗代替不匹配的终端),其左侧串联了一个25欧姆的电阻(R1),可以将其理解为信号源内阻,与传输线阻抗不相同(不匹配)。SRC1是一个阶跃信号源(幅值为1V,上升时间为1ns),用来模拟一个高速信号的上升沿。当然,也可以像《三极管》一书中使用时钟信号源。

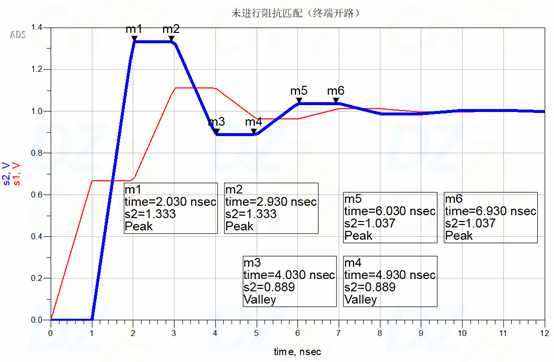

我们来看看瞬时仿真结果,如下图所示。其中,蓝色加粗线条为传输线右侧节点s2的电压波形,红色细线条为传输线左侧节点s1的电压波形。很明显,本来两个波形都应该是理想的上升沿(上升时间为1ns),现在都发生了变形,这就是由于信号反射带来的影响。

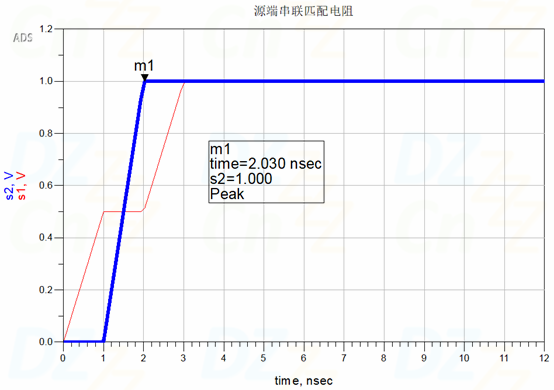

现在我们在源端再串联一个25欧姆的电阻(将R1阻值由原来的25欧姆改为50欧姆即可),相应的仿真结果如下图所示。可以看到,在高速信号刚到达终端时(1ns后),由于信号源内阻50欧姆与传输线阻抗(50欧姆)分压,s2的电压值本应该约为0.5V,但是由于负载为无穷大,其反射系数为1,所以0.5V全部被反射回来,两个电压值叠加所以得到了1V(即信号源的幅值)。

当然,你也可以采用终端并联下拉电阻匹配方案。保持原来的R1为25欧姆不变,在终端并联一个50欧姆的电阻,相应的仿真电路如下图所示:

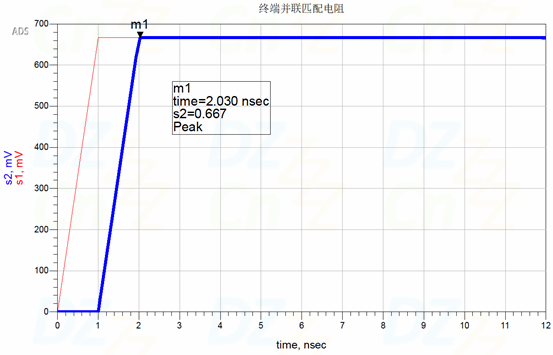

仿真的结果如下图所示,可以看到,现在传输线两侧都不再有信号反射现象,但电压幅值都只有约0.667V,它是25欧姆源端输出阻抗与50欧姆传输线阻抗对信号源(1V)串联分压得到的。

以上仿真参数与结果均与《三极管》一书相同,关于反射系数、驻波比、阻抗匹配、史密斯圆图、高频放大电路的匹配电路设计等细节也可参考此书,此处不再赘述。

浙公网安备 33010602011771号

浙公网安备 33010602011771号