【ZYNQ】学习笔记:VDMA彩条显示实验Part1

【学习视频】正点原子https://www.bilibili.com/video/BV11j411f7Co

===================================================================

【ZYNQ】学习笔记:VDMA彩条显示实验Part2 https://www.cnblogs.com/steven913/p/17298731.html

===================================================================

【学习笔记】

【1】

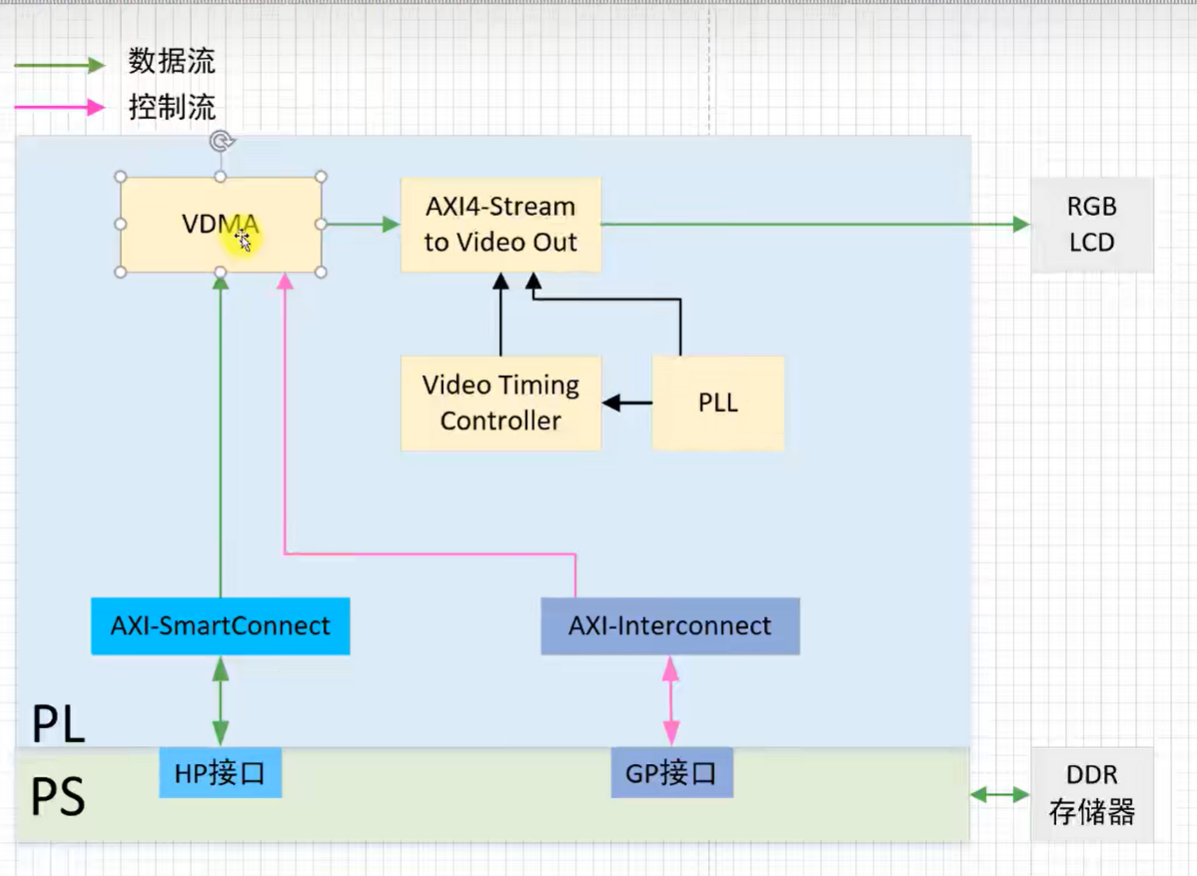

DDR的帧缓存操作:VDMA写数据至DDR;VDMA再从DDR中读取数据。

作用:解决视频源与显示设备间速率、分辨率不匹配的问题。

【2】

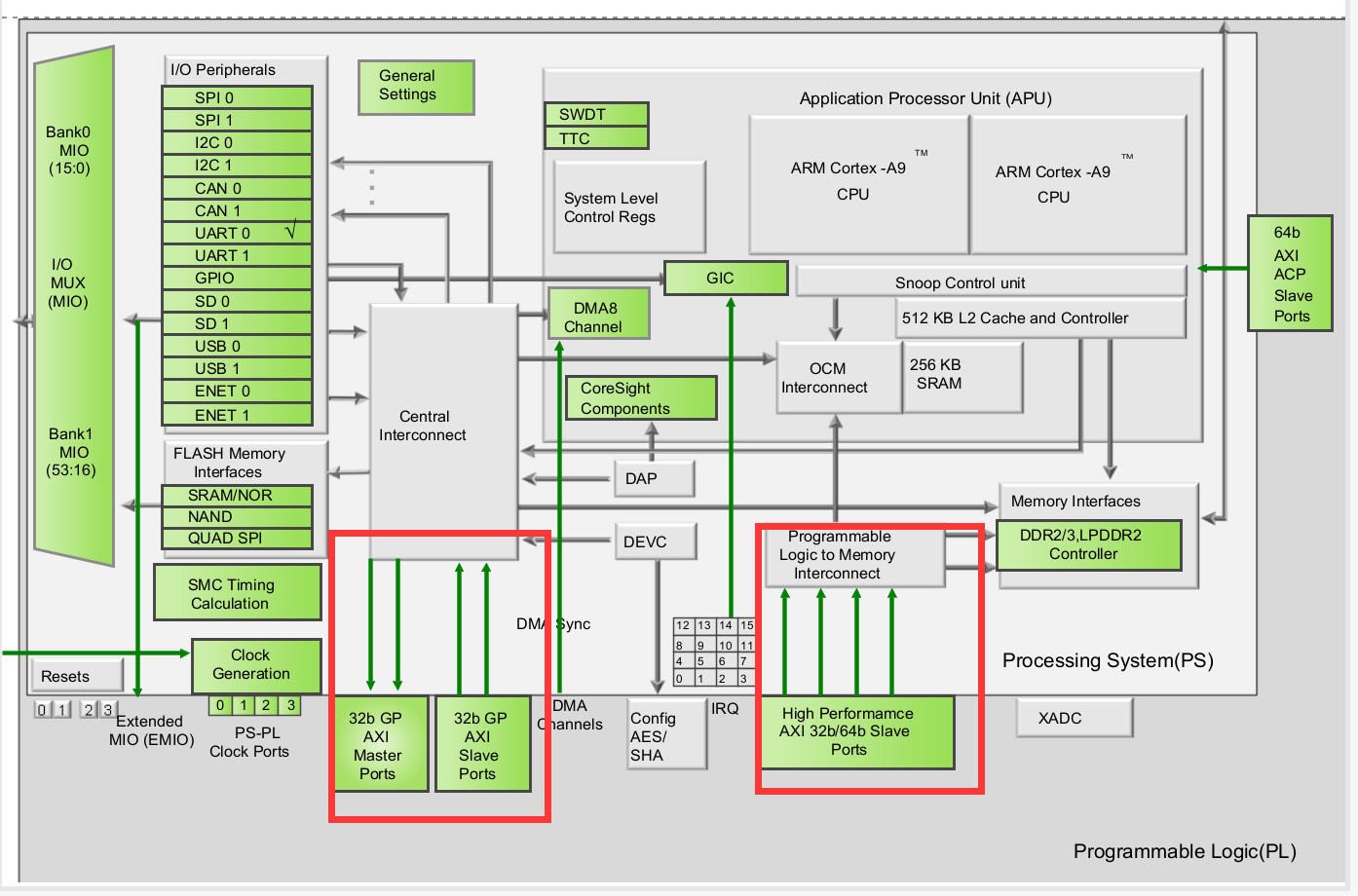

PS通过GP接口控制PL中的VDMA模块。

【3】

打开Vivado工程,新建Block Design,配置ZYNQ-PS:

(1)UART0:14、15

(2)DDR3:MT41J256M16RE-125

(3)FCLK_CLK0:100MHz

(4)HP Slave AXI:HP0(S_AXI_HP0)

对于HP而言,PS是从机,故为Slave,而PL为主机;但在本实验中,PS是GP接口(M_AXI_GP0)的主机,PL为从机。

【4】

HP:High Performance Ports 高性能端口,每个接口有两个FIFO缓存(AFI:AXI FIFO interface)

GP:General Purpose Ports 通用端口(同GPIO),无FIFO缓存

共有四个HP接口,均是PL为主机,PS为从机(箭头从PL指向PS)

共有四个GP接口,两个是PL为主机、PS为从机,两个是PL为从机、PS为主机。(本次实验用到后者之一)

【5】

Interconnect互联:数据交互的主要机制(机构,mechanism,也可称为“开关”,即开启/关闭数据的交互)

互联矩阵:网状结构

【6】

数据总线位宽(Data bus width)

HP:32或64bit(借助FIFO提升了性能)

GP:32bit(无FIFO)

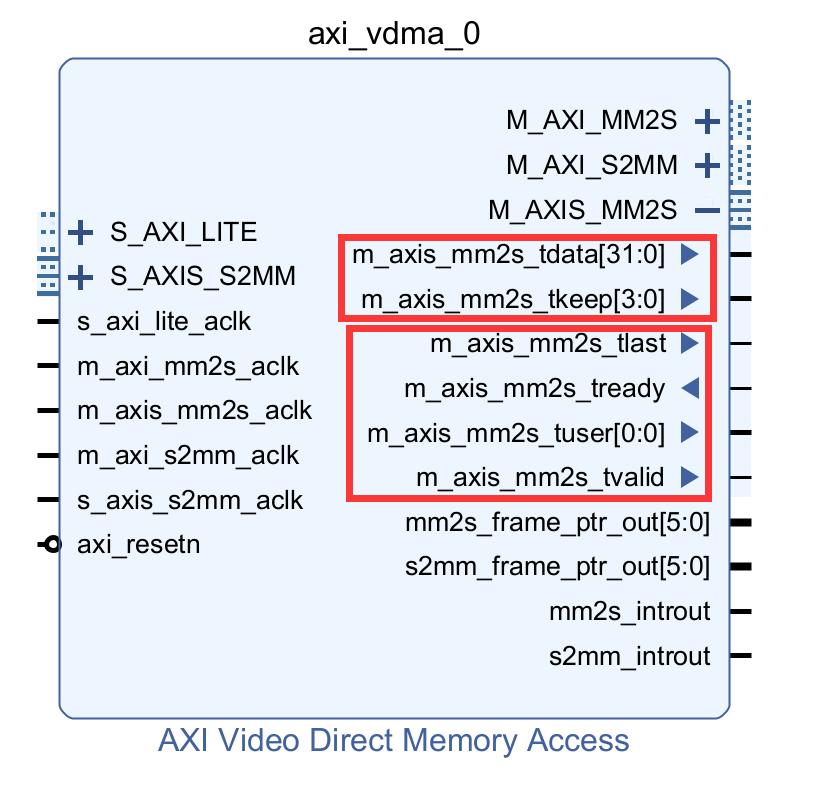

【7】添加IP核——VDMA:AXI Video Direct Memory Access

用于AXI4-Stream Video 类型的目标外设。

采用AXI4-Stream Video Protocol(协议):支持视频IP核间的数据传输(该协议与AXI4-Stream Protocol有很大的相似性,而后者用于AXI4-Stream 类型的目标外设)。

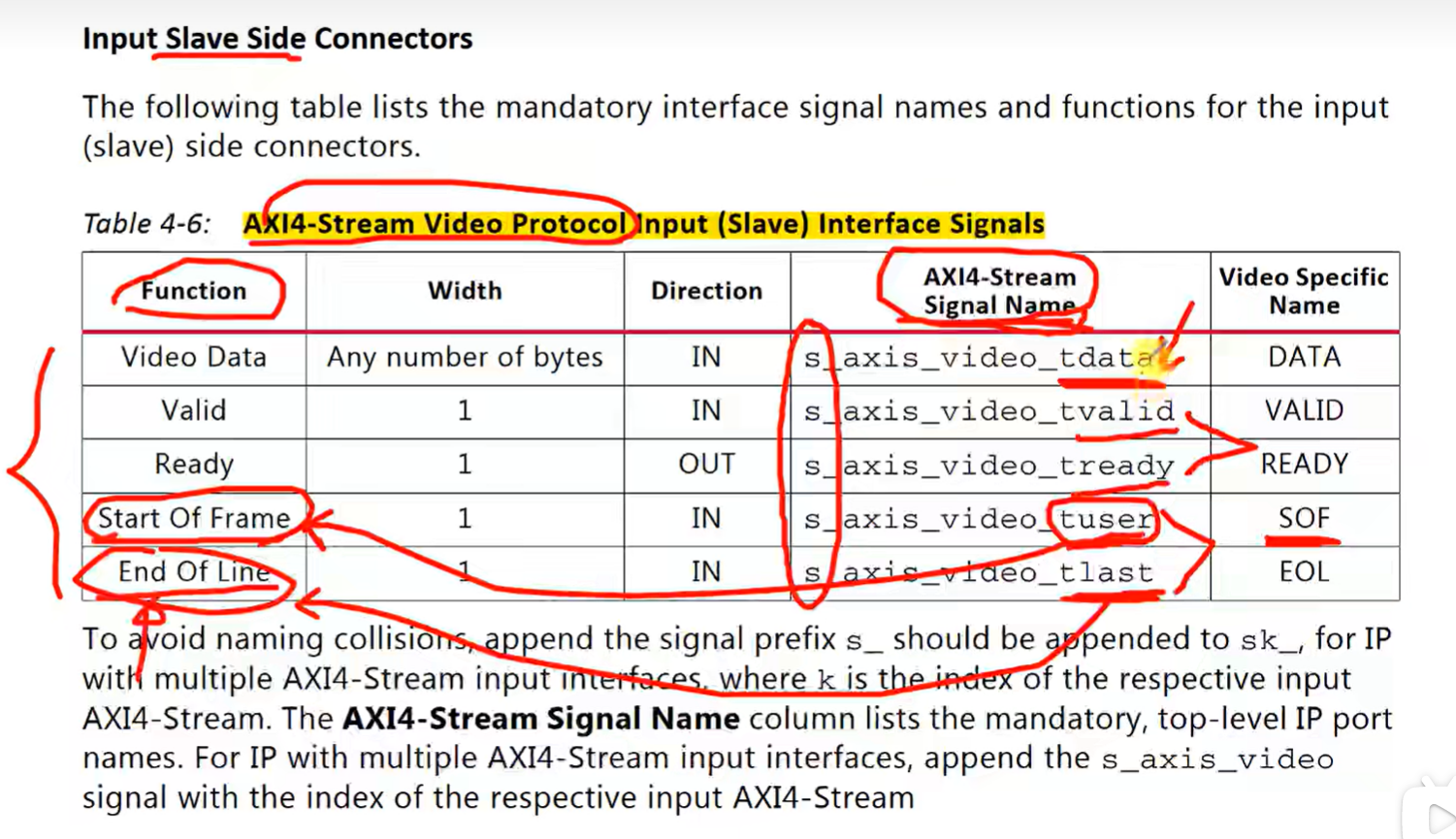

对于协议的Slave而言,Valid信号方向为IN,Ready信号方向为OUT;对于协议的Master而言,Valid信号方向为OUT,Ready信号方向为IN。

通常Valid和Ready信号是成双成对出现的,是常见的“握手”机制,且Valid与Ready通常是反向的。

【8】

AXI4-Stream Protocol中的TKEEP和TSTRB信号在AXI4-Stream Video Protocol中并没有被用到。

若连接到有这两个信号的IP核,将它们赋值为1(高电平)即可。

【9】

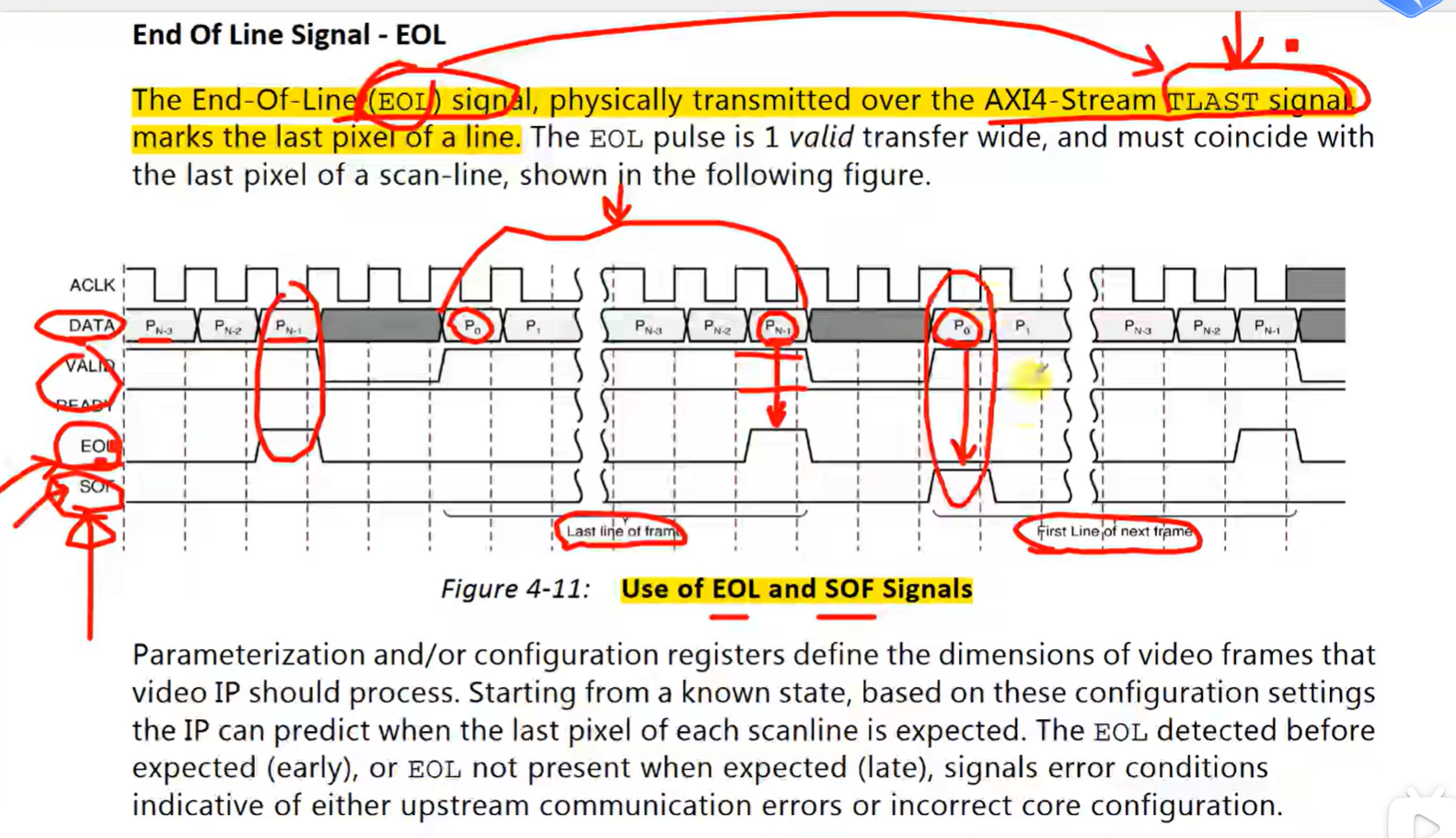

SOF:Start of Frame 一帧图像的开始;

EOL:End of Line 一行帧数据的结束;

一帧分为许多行。

在Video协议中,TUSER信号只有bit0是有意义的,即它代表了Start of Frame(SOF);即使该信号有再多的位数,也只有bit0有效。

EOL(End of Line)信号由AXI4-Stream Protocol的TLAST信号接口传输。

所以,SOF和EOL在IP核中是找不到的,在IP核信号中它们分别是TUSER信号的bit0和TLAST信号。

【10】

Ready/Valid Handshake 握手机制:当Ready和Valid同时为高电平时,数据传输有效(还需考虑SOF和EOF)。

【11】

VALID、READY、SOF、EOL信号都是为了统一时序(标志视频传输的时序,为后续IP同步图像处理过程)。

VALID、READY、SOF为高电平、EOL为低电平,此时DATA有效,且为第1帧的第1个像素

【12】

要将AXI4-Stream Signal NAME 与 AXI4-Stream Video Protocol的Function关联起来。

【13】

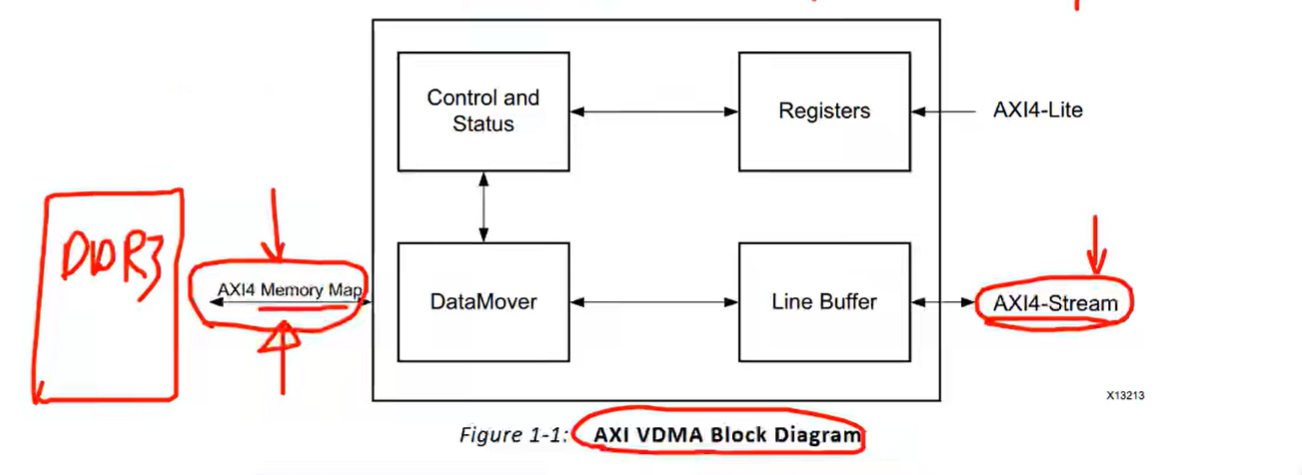

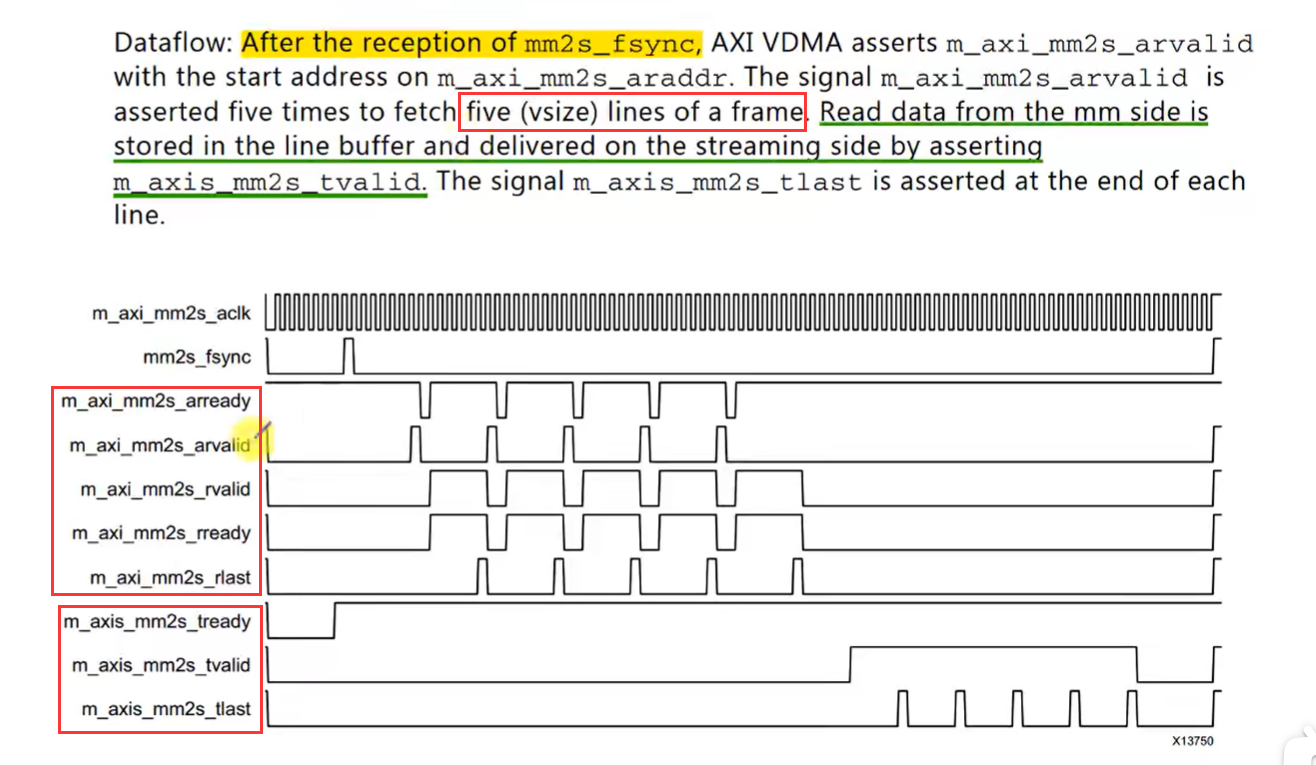

【14】VDMA读路径:MM2S(AXI4 Memory Map to AXI4-Stream):Data从DDR到AXI4 Memory Map到DataMover到Line Buffer到AXI4-Stream。

mm2s_fsync帧同步信号:下降沿标志着同步的开始。

axi表示AXI4接口,即MM(Memory Map);axis表示AXI4-Stream接口。从MM中读出的数据先存在Line Buffer中,再从中由AXI4-Stream读出。

arready和arvalid分别为ready和valid的地址信号,它们分别开启五次,意味着从MM读取一帧(Frame)中的5行(Line)。

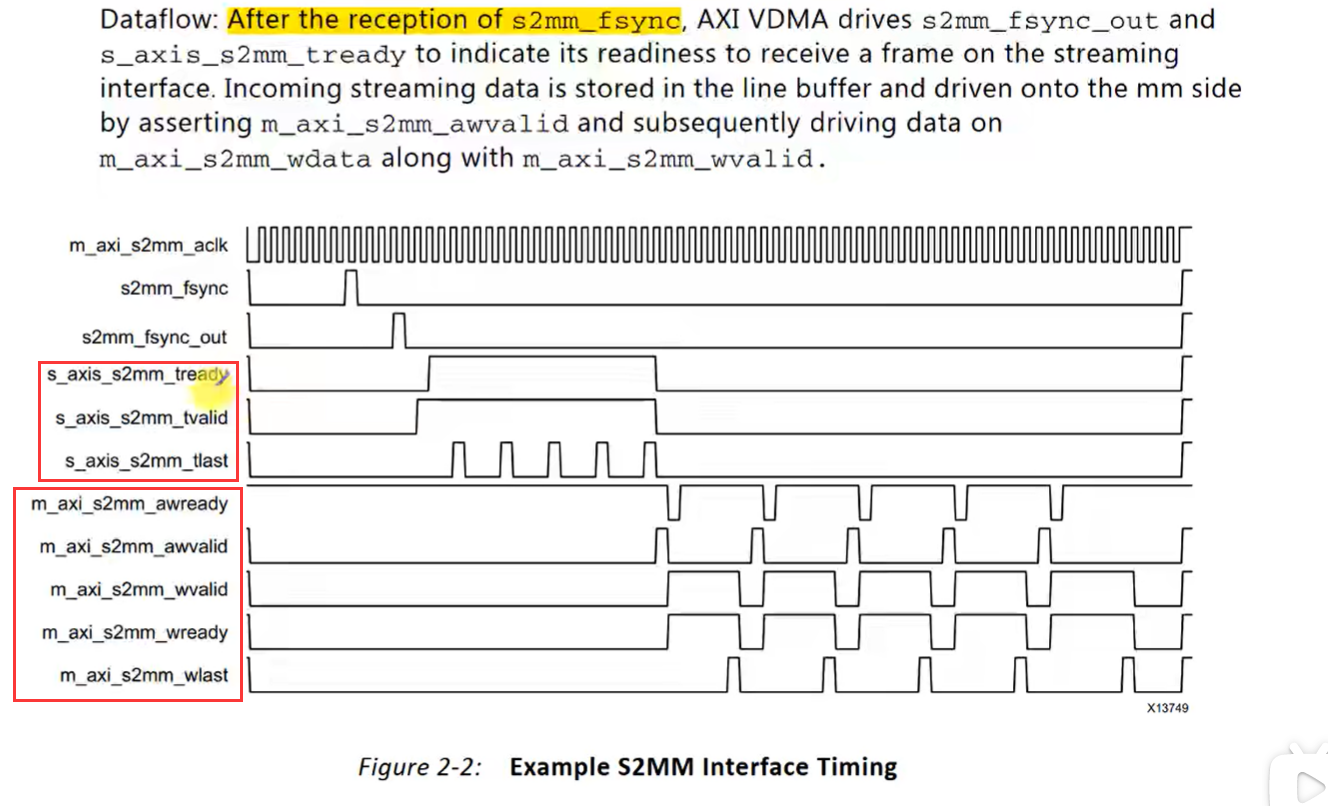

【15】VDMA写路径:S2MM(AXI4-Stream to AXI4 Memory Map):Data从AXI4-Stream到Line Buffer到DataMover到AXI4 Memory Map到DDR。

注意:axi接口的wlast信号与axis接口的tlast信号的性质是不同的。

axis的tlast信号(AXI4-Stream Video Protocol)表示每一行(Line)的最后一个像素点;

axi的wlast信号表示突发传输的最后一个数据,只是在这个时序图中,突发传输的长度正好等于帧图像一行的长度。

(例如,若帧图像一行为1920bit,而突发传输最多为256bit,那么wlast必须在传输256bit时拉高,而不能等到传输1920bit时才拉高;而tlast只能在一行的最后一个像素,即1920bit时拉高)

【16】

由于本次实验的图像数据由PS端生成并写入DDR,故VDMA模块仅执行MM2S路径(读数据操作)。

浙公网安备 33010602011771号

浙公网安备 33010602011771号