【读书笔记】《Verilog HDL数字设计与综合(第二版 本科教学版)》第一章:Verilog HDL数字设计综述

一、数字电路CAD技术的发展历史

真空管

晶体管,

集成电路(Integrated Circuit, IC)

小规模集成电路(Small Scale Integrated, SSI):逻辑门数量很少

中规模集成电路(Medium Scale Integrated, MSI):单个芯片布置上百个逻辑门

电子设计自动化(Electronic Design Automation, EDA)

大规模集成电路(Large Scale Integrated, LSI):单个芯片布置数千个逻辑门

手工完成电路版图设计,在面包板上完成逻辑仿真。

超大规模集成电路(Very Large Scale Integrated, VLSI):单片集成超过10万个晶体管

计算机辅助电路验证;用计算机进行电路版图的布局布线;计算机图形终端进行门级设计;模块化设计,从底层到高层,最终完成顶层设计。

二、硬件描述语言的出现

硬件描述语言(Hardware Description Language, HDL)

80年代后,逻辑综合工具发展,设计者可使用HDL在寄存器传输级(Register Transfer Level, RTL)对电路进行描述。

使用硬件描述语言来描述电路的功能和数据的流向,由逻辑及综合工具自动综合出由逻辑门及其互相连接构成的电路结构细节。

HDL在系统设计中的应用:仿真电路板、互联总线、现场可编程逻辑门阵列(Field Programmable Gate Arrays, FPGA)以及可编程阵列逻辑(Programmable Array Logic, PAL)等。通常,使用HDL单独设计每个芯片,然后通过仿真来验证整个系统的功能。

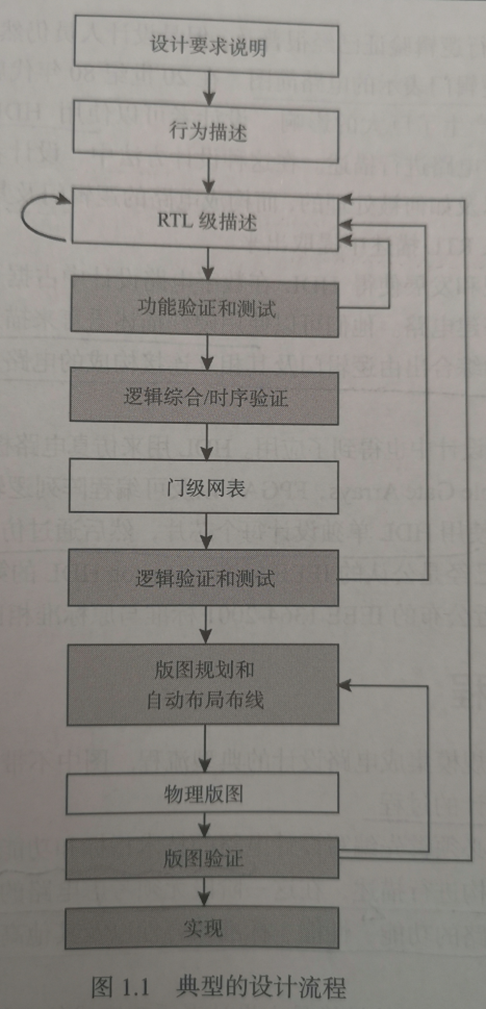

三、典型设计流程

设计重点:手工对RTL描述的优化。

设计者只需在非常抽象的层次使用HDL对电路的算法进行描述,然后再EDA工具的帮助下完成从行为级描述道最终芯片结构的转换。

四、硬件描述语言的意义

通过使用硬件描述语言(HDL):

(1)设计者可在非常抽象的层次上对电路进行描述

在RTL级进行电路描述而不必选择特定的制造工艺,逻辑综合工具可将设计转换为任意工艺的版图(门级网表),出现新工艺也只需要进行转换即可。

(2)可在设计周期的早期对电路的功能进行验证

易于对RTL描述进行优化和修改,在电路设计的早期发现和排除绝大多数设计错误。

(3)类似于计算编程,带有文字注释的源程序便于开发与修改

五、Verilog HDL的优点

Verilog HDL是一种通用的硬件描述语言,语法与C语言类似;

Verilog HDL允许在同一个电路模型内进行不同抽象层次的描述(开关级、门级、RTL级、行为级,等等);

编程语言接口(Programming Language Interface, PLI)是Verilog语言最重要的特性之一,它使得设计者可以通过自己编写C代码来访问Verilog内部的数据结构。可根据自己需要使用PLI配置Verilog仿真器。

六、硬件描述语言的发展趋势

随着数字电路速度和复杂性提升,最好能从更高的抽象层次对电路进行描述(只需从功能角度进行设计,由EDA工具完成具体实现细节)。

逻辑综合工具:从RTL描述生成门级网表(RTL级设计是基于HDL的主流设计方式)。

行为级综合工具:直接对电路的算法和行为进行描述,由EDA工具再各设计阶段进行转换和优化(尚未被业界广泛采用)。

形式验证和断言检查(formal verification and assertion checking):使用形式化的数学方法来验证Verilog HDL描述的正确性,并对RTL描述与综合后得到的门级网表电路行为的等价性进行检查。

断言检查允许将检查规则嵌入RTL描述中。

用Verilog HDL进行设计描述的需求将不会消失:对于像处理器这样的超高速、对时序有着严格要求的电路来说,逻辑综合工具生成的门级网表并不是优化的。此时需要直接在RTL描述中嵌入门级描述,以达到优化的效果。

-

-

浙公网安备 33010602011771号

浙公网安备 33010602011771号