vivado通过eco修改网表加快调试

在FPGA工程中,在调试过程中需要插入ila来验证设计的准确性,但一次验证不能达到设计的初衷,需要反复修改ila来定位问题,往往一个大工程编译、布线时间较长,反复定位问题非常耗费时间。xilinx系列的vivado16.4以上版本支持了类似ic设计的ECO功能。

1、dcp文件

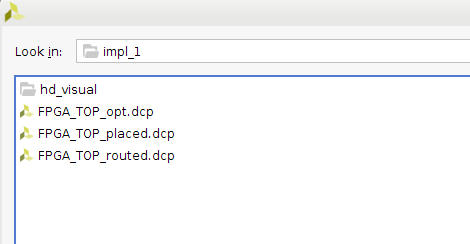

在implement成功后,/xxx.runs/impl_1文件夹下会有xxx_opt.dcp、xxx_placed.dcp、xxx_routed.dcp三个DCP文件。

- xxx_opt.dcp:在opt_design完成之后生成,opt_design主要是完成逻辑优化等;

- xxx_placed.dcp在placed_design完成之后生成,placed_design主要是完成布局工作;

- xxx_routed.dcp在routed_design完成之后生成,routed_desig主要是完成布线工作。

2、使用场景

以下几种场景可以使用eco功能

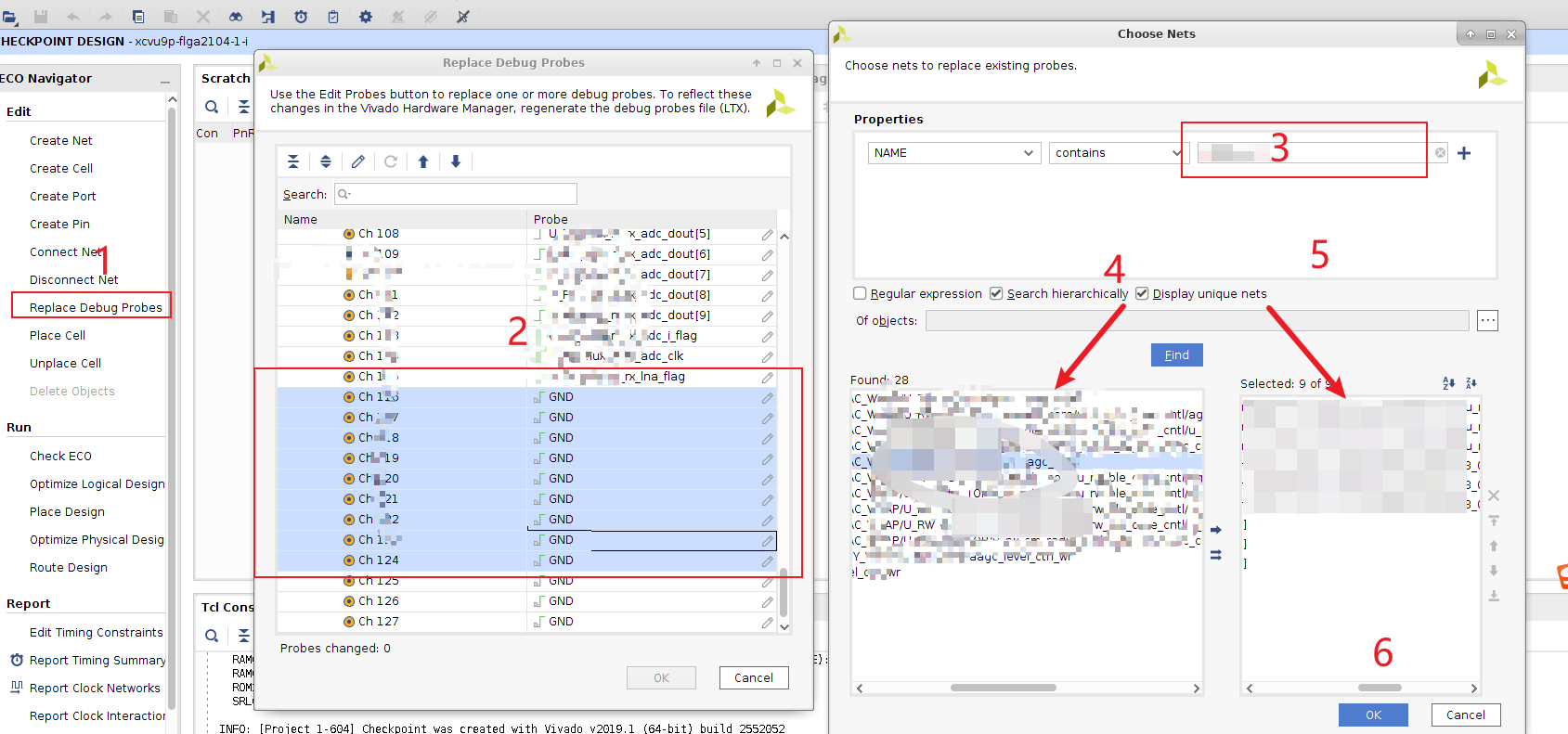

- 板级调试时,发现需要观测的信号没有添加到ila中。可使用ECO功能下的Replace Debug Probes(已经有ILA模块,只是没有加进去);

- 板级调试时,需要观测的信号没有添加到ILA中,且没有例化ILA核。可以在Debug功能生成Debug Core;

- 初始化RAM、ROM初始值。对RAM18E和RAM36E模块进行初始化;

- 逻辑功能有问题,需要简单的添加接地、拉高、FF、LUT等(理论上底层模块都能添加)。

3、替换ila引脚

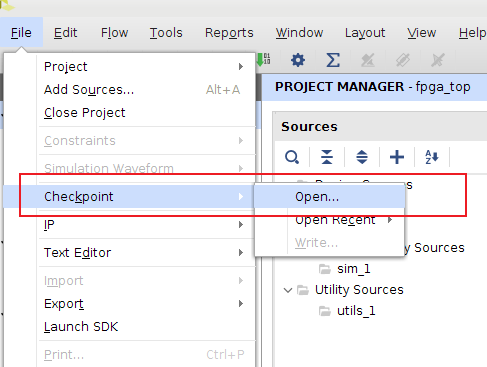

- 打开xxx_routed.dcp

在xxx.runs/impl_1/找到xxx_routed.dcp

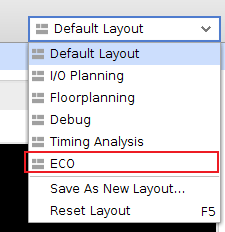

选择ECO选项

按照图示替换ila已有信号为选取的信号,点击OK

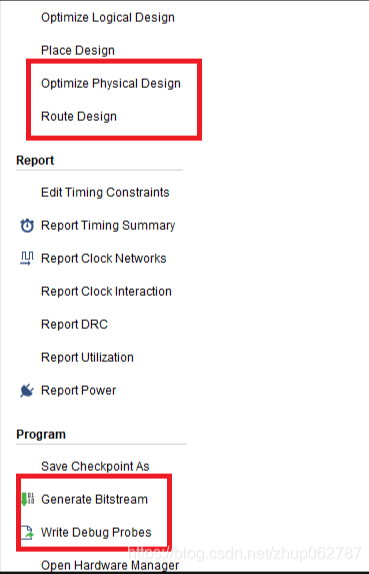

因为只是修改了布线,布局没有改动,所以需要Route Design。Optimize Physical Design是优化布局、时序等。大工程不优化有可能布不成功。布局完成,直接Generate Bitstream、write Debug probes。

还有可以添加ila模块、初始化RAM、添加逻辑块等功能可参考https://blog.csdn.net/zhup062787/article/details/104888398

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· 单线程的Redis速度为什么快?

· SQL Server 2025 AI相关能力初探

· AI编程工具终极对决:字节Trae VS Cursor,谁才是开发者新宠?

· 展开说说关于C#中ORM框架的用法!