2-255倍四路输出分频器~~互相学习

module frediver( input clkin, input en, output reg freq1out = 1'b0, output reg freq2out = 1'b0, output reg freq3out = 1'b0, output reg freq4out = 1'b0 ); parameter denominator1 = 3; parameter denominator2 = 4; parameter denominator3 = 6; parameter denominator4 = 8; reg [7:0] cal1 = 8'b0; reg [7:0] cal2 = 8'b0; reg [7:0] cal3 = 8'b0; reg [7:0] cal4 = 8'b0; always@(clkin or en) begin if( en ) begin cal1 <= (cal1 == denominator1 - 1 ? 8'b0 : (cal1 + 8'b1)); cal2 <= (cal2 == denominator2 - 1 ? 8'b0 : (cal2 + 8'b1)); cal3 <= (cal3 == denominator3 - 1 ? 8'b0 : (cal3 + 8'b1)); cal4 <= (cal4 == denominator4 - 1 ? 8'b0 : (cal4 + 8'b1)); freq1out <= (cal1 == (denominator1 - 2) ? ~freq1out : freq1out); freq2out <= (cal2 == (denominator2 - 2) ? ~freq2out : freq2out); freq3out <= (cal3 == (denominator3 - 2) ? ~freq3out : freq3out); freq4out <= (cal4 == (denominator4 - 2) ? ~freq4out : freq4out); end end endmodule

SoC作业

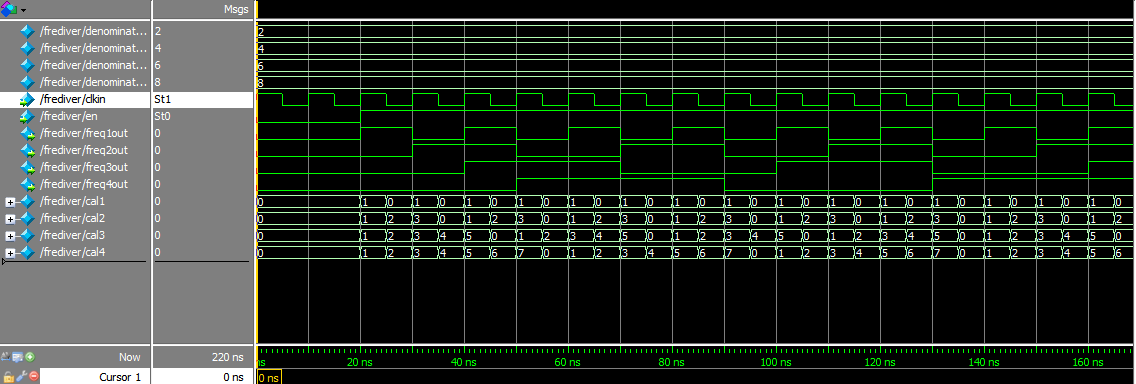

modelsim仿真图

浙公网安备 33010602011771号

浙公网安备 33010602011771号