芯片设计步骤和EDA的应用

前端设计

一、第一步,明确市场需求,确定产品的功能和性能。

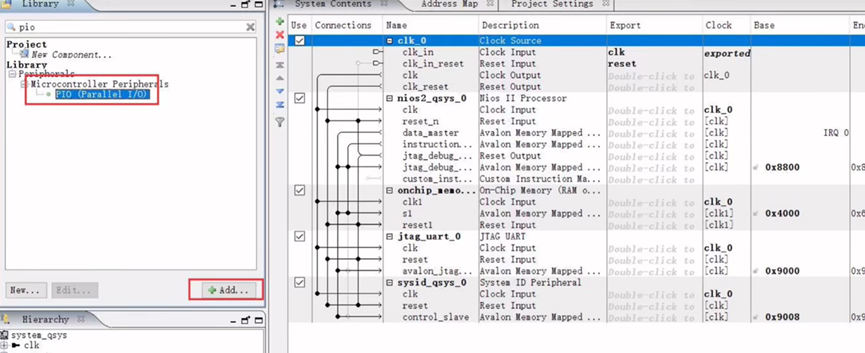

二、第二步,定义芯片的算法和模块(IP核)。

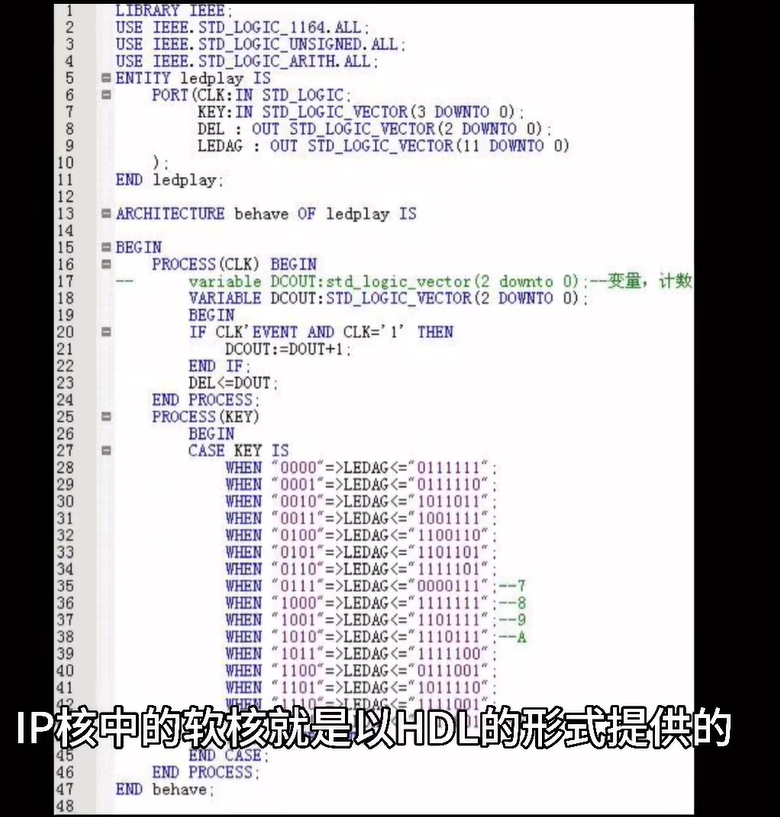

三、第三步,搭建功能模块。用硬件描述语言(HDL)将各个功能模块用代码组织起来。

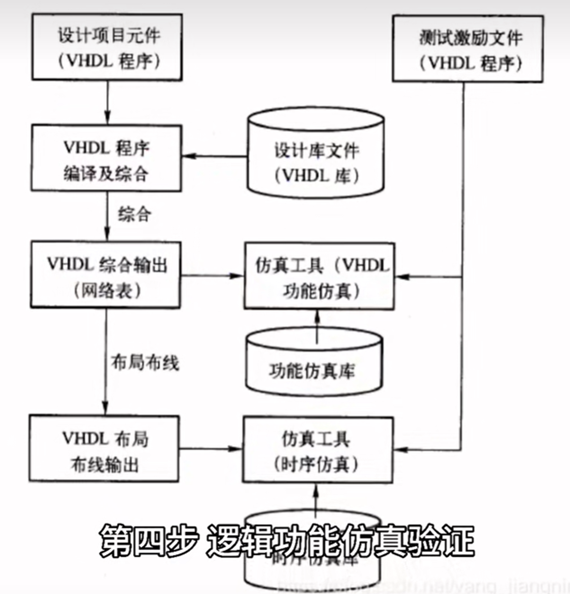

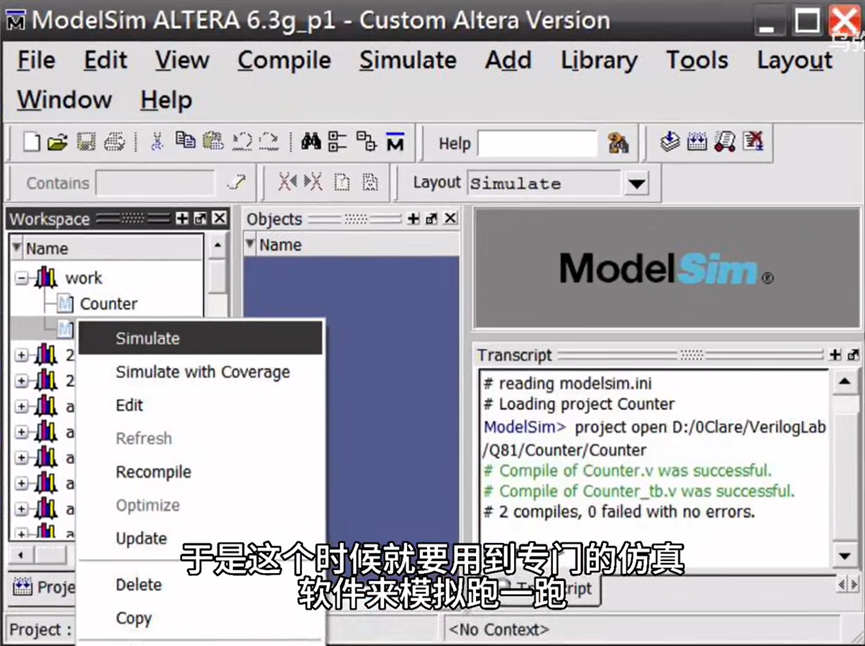

四、逻辑功能仿真验证:代码敲好了,模块搭建起来了,得试一下是否有bug,效果如何。这个时候需要进行仿真验证。

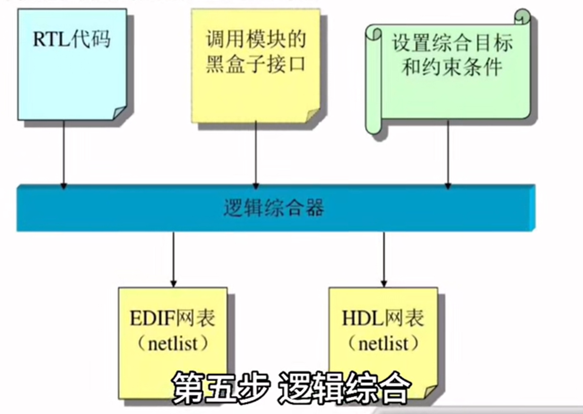

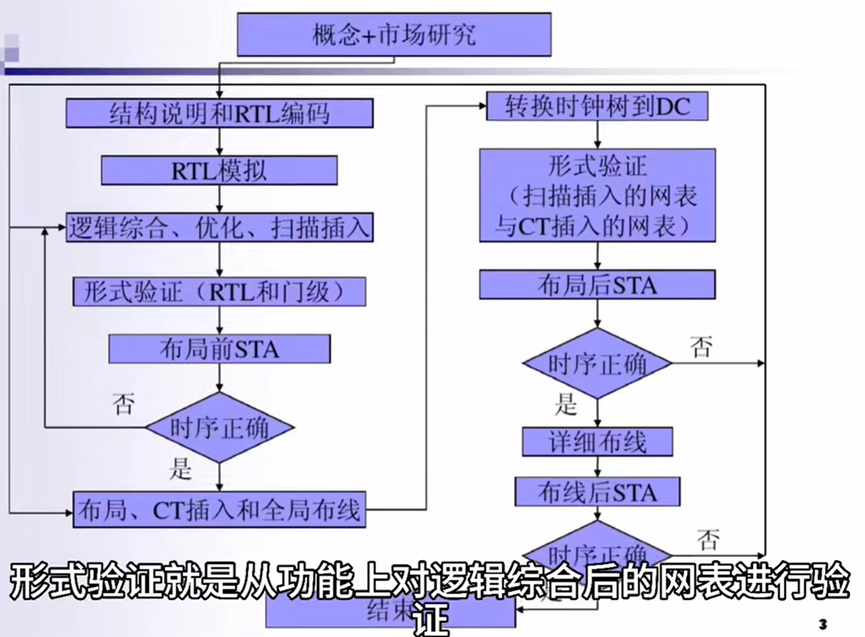

五、逻辑综合:就是把用HDL语言写的代码翻译成门级网表。网表就是用来描述电路元件之间连接关系的一种文本文件。每个晶圆代工厂都会提供自己的逻辑综合库和门电路基本标准单元,选择的综合库不一样,最后综合出来的电路在参数上也会有差异。

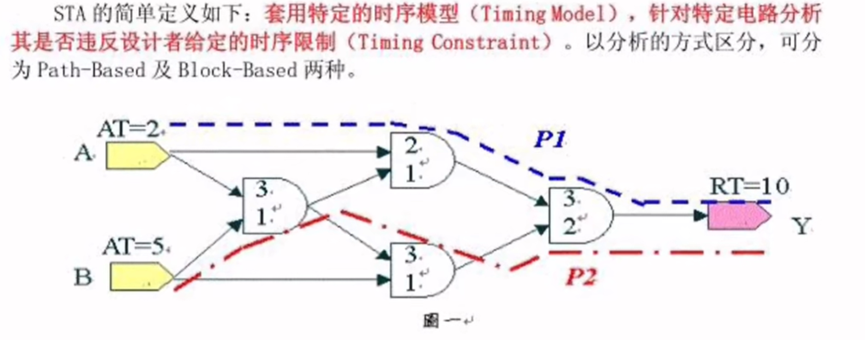

六、静态时序分析(STA)及形式验证。静态时序分析是验证是否违反设计者给定的时序限制。形式验证是从功能上对逻辑综合后的网表进行验证,常用的是等价性验证,以验证后的HDL设计为参考,对比综合后的网表,看它们在功能上是否存在等价性,这就是为了保证逻辑综合以后没有改变原来HDL描述的电路功能。

完成上述六个步骤,芯片设计的前端工作就算是完成了,在这个前端流程中我们获得了芯片的门级网表电路。芯片设计分为前端设计(也称逻辑设计)和后端设计(也称物理设计),两者没有严格的界限,不过后端设计会涉及到与芯片制造工艺相关的问题。

后端设计

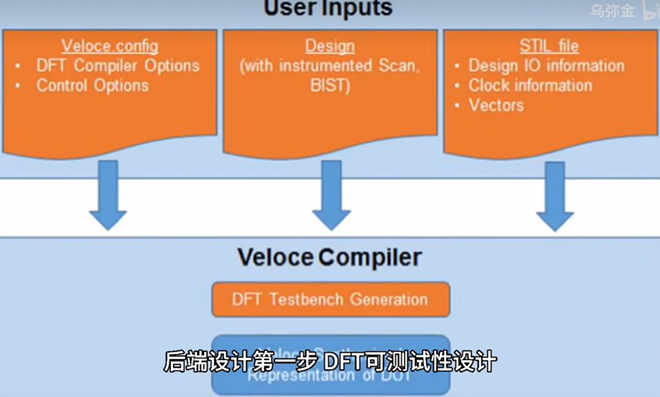

一、DFT可测试性设计:在不影响芯片正常工作的情况下,插入一些特殊结构的测试电路,以便芯片设计完成后在后续的硅片和封装测试中进行缺陷和故障测试,这样可以减少测试成本。

二、布局布线:安排芯片各个功能电路的摆放位置,让各个标准单元、门阵列和IP核等等实现布线交互。

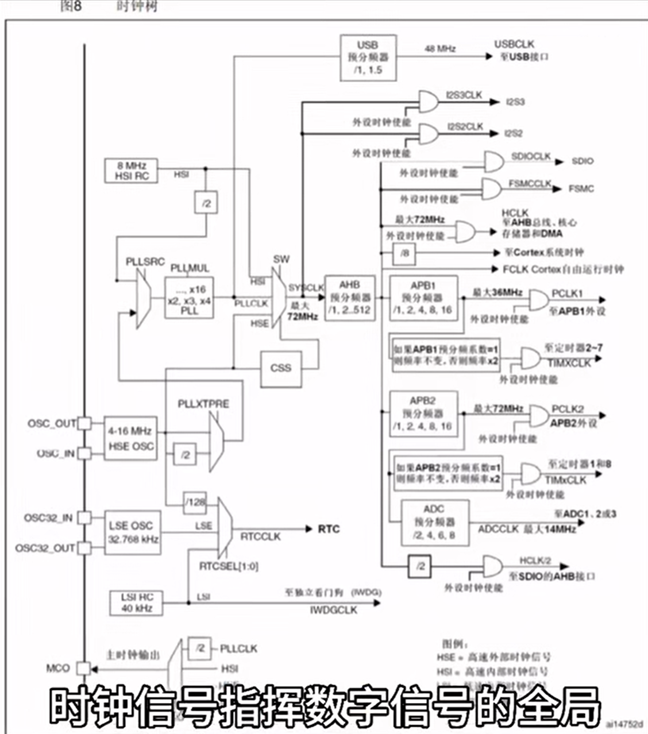

三、时钟树综合CTS。时钟信号指挥数字信号的全局,让时钟从同一个时钟源到达各个寄存器时,时钟延迟差异最小,所以时钟信号需要单独一下搞布线。

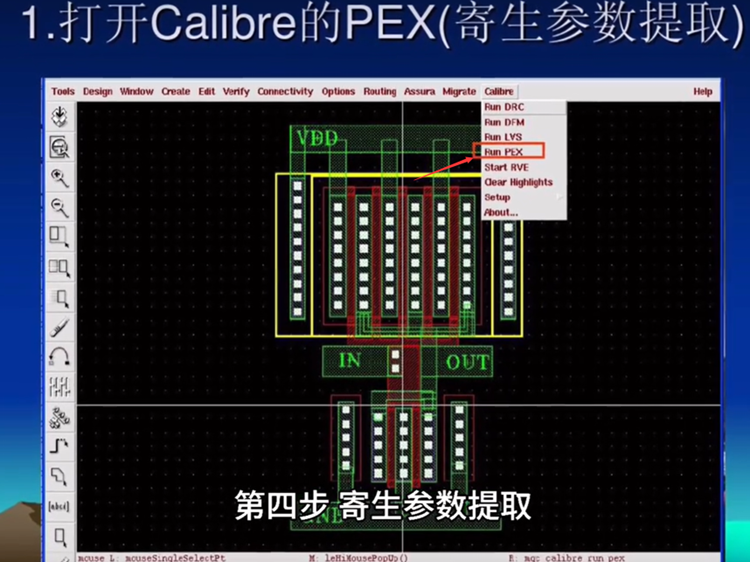

四、寄生参数提取。由于布线的导线自身也存在电阻,相邻的导线之间互感耦合电容在芯片内部会产生信号噪声串扰和反射,这些会影响信号的完整性,所以要对寄生参数进行提取,并再对生成布线后的电路进行仿真。

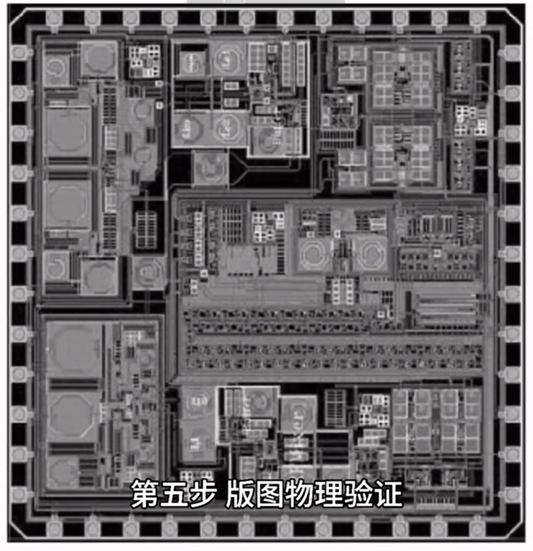

五、版图物理验证。这一步是对完成布线的物理版图进行功能和时序上的验证。这一步之后芯片设计的工作就完成了。

将物理版图交给晶圆厂,晶圆厂根据掩膜版在硅片上作出实际的电路,再经过封装和测试就成了我们平时看到的芯片。

上面的每一个步骤都有相关的EDA细分工具,可以看出,EDA贯穿芯片设计的始终。

参考:https://www.bilibili.com/video/BV1i44y1y7Gh/?spm_id_from=333.999.0.0&vd_source=2758ef806213f133641bb5da6406140b

浙公网安备 33010602011771号

浙公网安备 33010602011771号