mini2440的MPLL和UPLL

S3C2440有两个PLL(phase locked loop)一个是MPLL,一个是UPLL。MPLL用于CPU及其他外围器件,UPLL用于USB。用于产生FCLK, HCLK, PCLK三种频率,这三种频率分别有不同的用途:

1.FCLK是CPU提供的时钟信号。

HCLK是为AHB总线提供的时钟信号, Advanced High-performance Bus,主要用于高速外设,比如内存控制器,中断控制器,LCD控制器, DMA 等。

从S3C2440的DataSheet里可以看到,S3C2440最大支持400MHz的主频,但是这并不意味着一定工作在400MHz下面,可以通过设定MPLL, UPLL寄存器来设定CPU的工作频率。

尽管在CPU上电(power-on)或者复位(reset)后,MPLL就开始进入工作状态,但是此时MPLL的输出(Mpll)并不作为系统的时钟,而是直接使用外部信号EXTCLK或者外部时钟晶振作为系统时钟。直到软件初始化MPLL寄存器(rMPLLCON),写入了有效的值过后,系统才开始使用MPLL的输出(Mpll)作为系统时钟。虽然很多时候我们不必重新设置MPLL寄存器(rMPLLCON)新的值,但是为了使系统使用其输出作为时钟信号,在软件初始化系统部分,还是要向rMPLLCON写入一个有效的旧的值。这样子才使系统处于正确的工作状态。

2.HCLK是为AHB总线提供的时钟信号, Advanced High-performance Bus,主要用于高速外设,比如内存控制器,中断控制器,LCD控制器, DMA 等。

3.PCLK是为APB总线提供的时钟信号,Advanced Peripherals Bus,主要用于低速外设,比如看门狗,UART控制器, IIS, I2C, SDI/MMC, GPIO,RTC and SPI等。

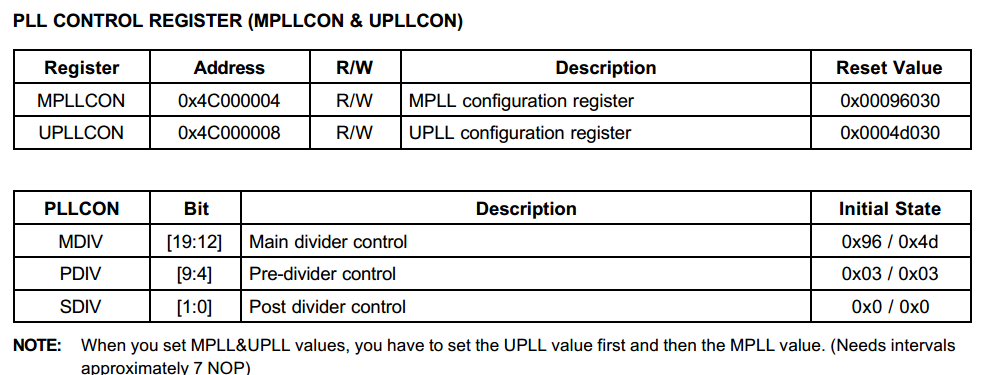

- MPLLCON&UPLLCON寄存器

上图注意最后的说明,UPLL一定要在MPLL设置之前设定。

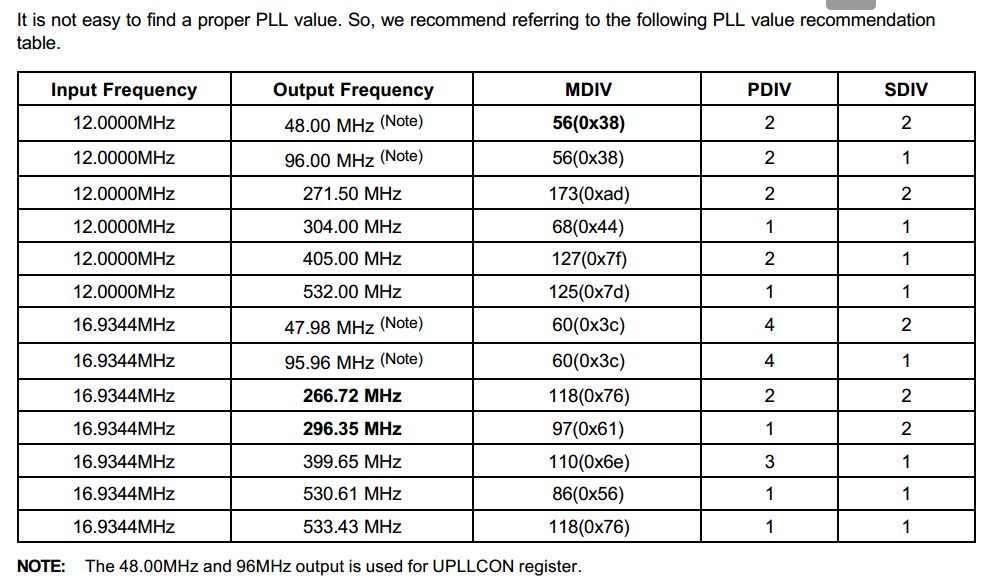

这里是一份推荐设置表:

在s3c2440.s初始化代码中,可以看到

MPLLCON_Val EQU 0x00043011 //300Mhz

这里是设置了FCLK为300Mhz

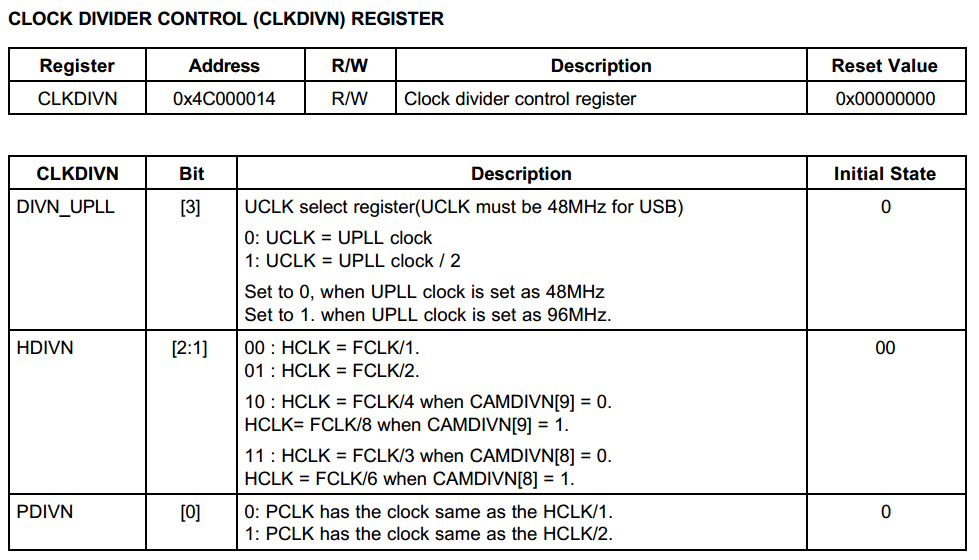

- 时钟分频控制寄存器CLKDIVN

CLKDIVN用来控制FCLK, HCLK, PCLK的比例

PLL 值选择向导(MPLLCON)=========Fin在mini2440板子上大小是12Mhz

1. Fout = 2 × m × Fin / ( p*2s ),Fvco = 2 × m × Fin / p 此处:m =MDIV+8, p=PDIV+2, s=SDIV

2. 600MHz ≤ FVCO ≤ 1.2GHz

3. 200MHz ≤ FCLKOUT ≤ 600MHz

4. 不要设置 P 或 M 的值为 0,这是因为设置 P=000000,M=00000000 将会引起 PLL 的故障。

5. P 和 M 的合理范围为:1 ≤ P ≤ 62,1 ≤ M ≤ 248

在s3c2440.s初始化代码中,可以看到

CLKDIVN_Val EQU 0x0000000F //HDIVN为全1,CAMDIVN[8]为0,所以HCLK为FCLK/3,为100Mhz,PDIVN为1,所以PCLK=HCLK/2=50Mhz

CAMDIVN_Val EQU 0x00000000

CLOCK_SETUP EQU 1 LOCKTIME_Val EQU 0x0FFF0FFF MPLLCON_Val EQU 0x00043011 //FCLK=300Mhz UPLLCON_Val EQU 0x00038021 CLKCON_Val EQU 0x001FFFF0 CLKSLOW_Val EQU 0x00000004 CLKDIVN_Val EQU 0x0000000F //HCLK=100Mnz, PCLK=50Mhz(UART会用到) CAMDIVN_Val EQU 0x00000000

浙公网安备 33010602011771号

浙公网安备 33010602011771号