14_嵌入式RAM使用之ROM

第14课 嵌入式RAM使用之ROM

课程目标:学会调用Quartus l软件中提供的ROM(read only memory)核并进行系统设计;

ROM(read only memory)为只读存储器;其特点为掉电不丢失(广义上的),上电瞬间可自动加载到开发板;

怎样理解广义广义?掉电后芯片内部不会存在数据,而是数据保存在外部的配置芯片中,比如EPCS芯片,当开发板上电的瞬间,就会将EPCS中的数据读取出来,配置到FPGA芯片中,在配置过程中,一部分希望掉电保持的数据存储在所设计的片上ROM的结构中。

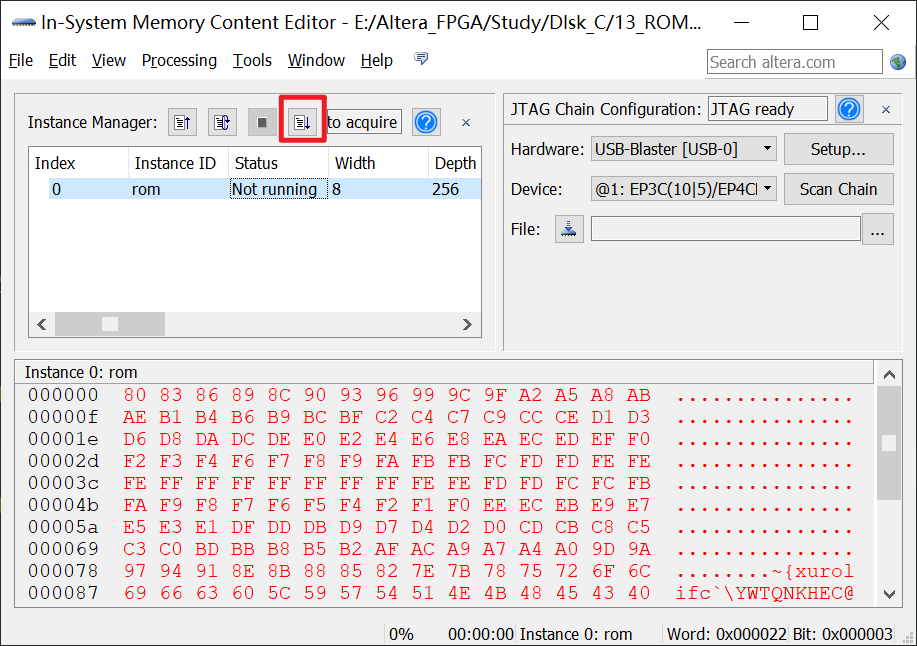

实验现象:将一组固定的数据(三角波形表)存储在FPGA中使用IP核构建的片上ROM中,开发板上电后,系统开始从ROM中读出数据,并将数据直接通过并口输出。通过使用signal Tapll软件实时抓取并口上的数据,显示得到三角波形。然后使用Quartusll软件中提供的In-System Memory Content Editor 工具在线更改ROM中的数据(将数据更改为正弦波形表),然后再次观察signal Tapll工具抓取到的波形数据。

知识点:

1、ROM存储器lP核的使用

2、In-System Memory Content Editor内存查看工具的使用。

3、SignalTap调试工具的简单使用

SignalTap调试工具流程示意图:

1.IP核ROM的建立

1.1 新建miff文件并写入内容

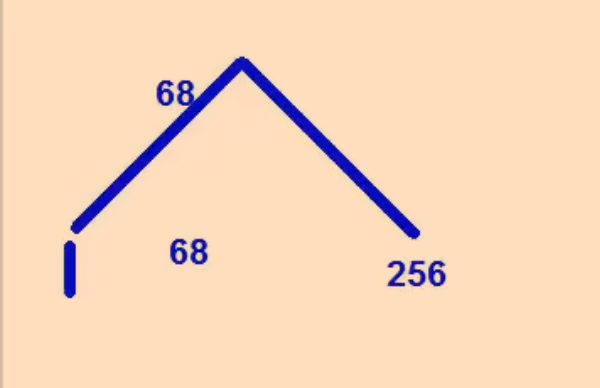

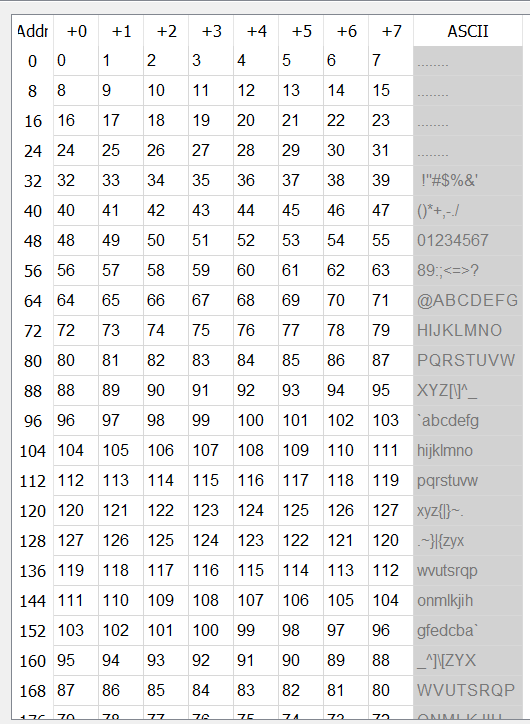

设置数据个数以及数据占用大小;如何创建miff文件;设置大小和位宽;将三角波的数据填入其中,三角波形如何得到?

生成三角波的miff文件方法:

(1)使用matlab生成三角波

(2)专用工具

(3)EXCEL导入(简单的三角波形可采用,但是复杂的比如正弦波就需要用特定工具)

这里可利用EXCEL文件写入数据[0...127-127...0]共256个数据,并复制粘贴在.mif文件中;注意:全选复制粘贴时,.miff文件的数据个数要与粘贴板的数据个数匹配,否则无法复制成功。

提示:所选范围与剪切或复制到剪贴板的范围不匹配!

1.2 新建IP核ROM

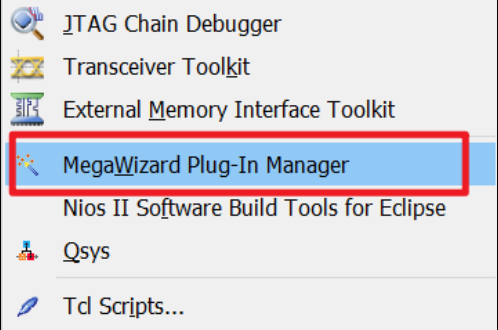

1.2.1 点击tool下的红框选项

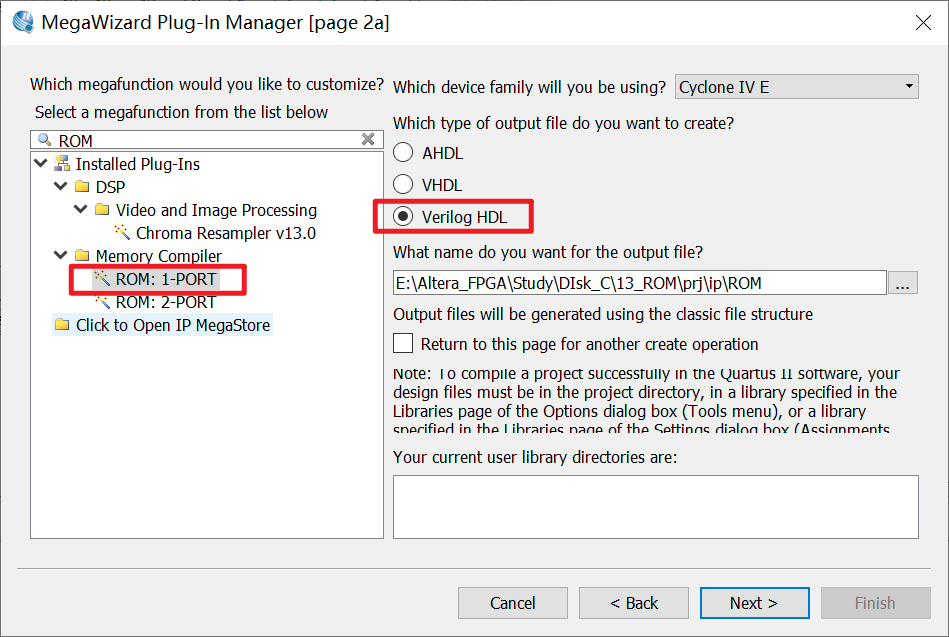

1.2.2

-选择ROM:1-PORT

-选择verilog HDL

1.2.3 选择数据个数;位宽;存储器类型;单时钟还是双时钟

如果想看ROM的操作说明,点击IP核数据手册右上角,documentation即可查看。

1.2.4 数据锁存设置

-对输出数据q锁存(加一级寄存器)

哪些端口上被寄存,也即需要在哪些端口加一级寄存器。数据输出Q加上一级寄存器,其输出会更稳定;

时钟使能引脚;异步清零信号(不清除ROM里面的数据,而是寄存器上的值);创建一个读使能信号;

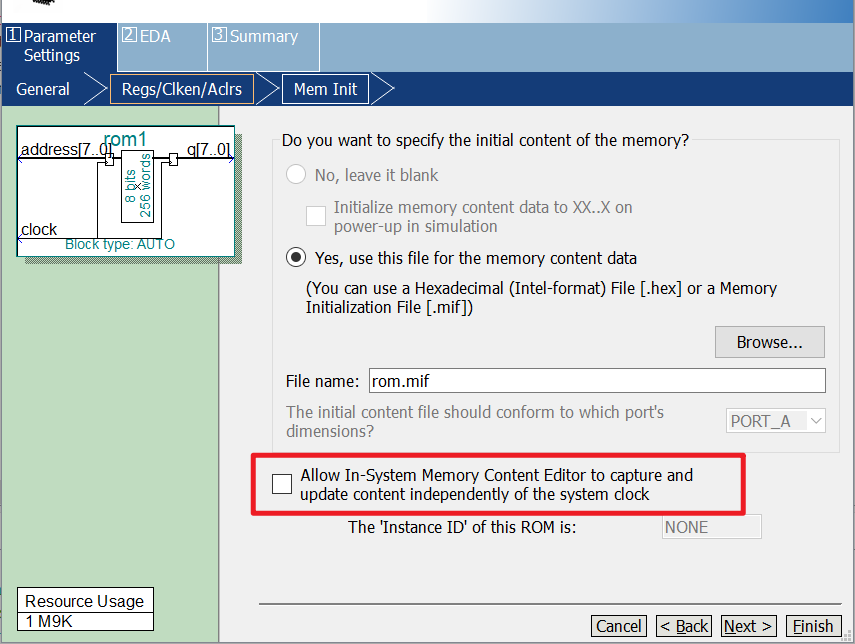

1.2.5 对ROM进行初始化

-给定初始化内容,默认必须,否则无法创建成功;使用HEX或者mif文件;

-勾选系统内存储器内容编辑器,方便后续更改ROM.mif文件内的内容; 并将ID命名为rom;

1.2.6 点击next,finish即可

2.仿真测试

2.1 编写rom_top.v文件

module rom_top( input Clk, input Rst_n, output [7:0]q ); reg [7:0]addr; //例化ROM rom1 rom1_0( .address(addr), .clock(Clk), .q(q) ); always @(posedge Clk or negedge Rst_n) if(!Rst_n) addr <= 8'd0; else addr <= addr + 1'b1; endmodule

2.2 编写rom_top_tb.v文件

`timescale 1ns/1ns `define clk_period 20

module ROM_top_tb(); reg Clk; reg Rst_n; wire [7:0]q; rom_top rom_top0( .Clk(Clk), .Rst_n(Rst_n), .q(q) ); initial Clk = 1; always #(`clk_period/2) Clk = ~Clk; initial begin Rst_n = 0; #(`clk_period * 20); #21; Rst_n = 1; #(`clk_period * 300); $stop; end endmodule

2.3 前仿真分析

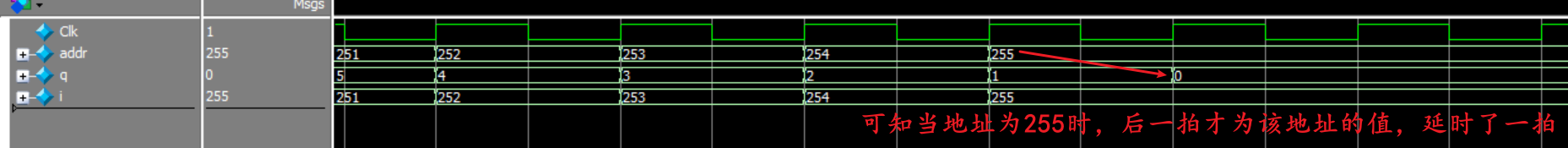

2.3.1 时序分析

由下图可知,ROM从给出地址到读取数据过程中, 延时了一拍;

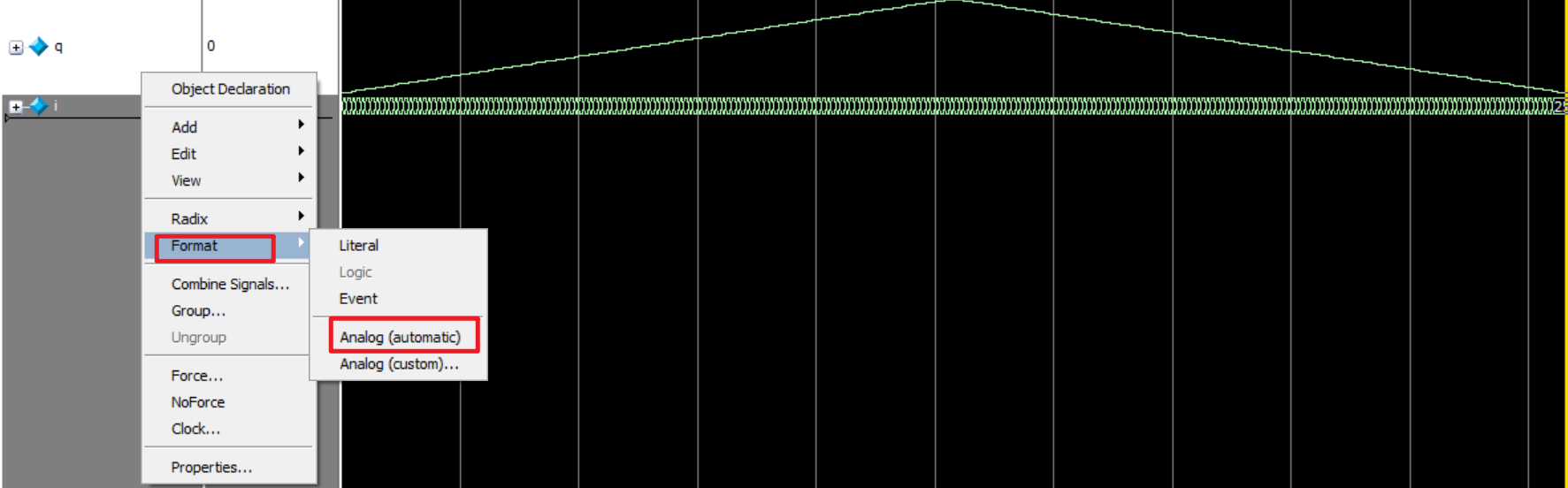

2.3.2 波形数据分析

鼠标右键点中数据,选择Format->Analog(automatic)

2.4 后仿真分析

当地址信号有效时候(已经延时了一拍),下下个时钟上升沿采集数据信号才比较稳定;

3. SignaTap II 逻辑分析仪的使用和上板测试

3.1 SignaTap II 逻辑分析仪的使用

(1)新建一个SignaTap II Logic Analyzer file,如下图:

(2)界面设置

-待观察信号,q输出端口和地址信号

-占用逻辑资源(逻辑分析仪在FPGA内部);相当于在内部开设一个存储器,先将数据存起来,然后再通过jtag发送到上位机实时显示;

-采样时钟

-存储器存储深度,4k(如果要显示10个正弦波,则需要256*10=2560bit)

(3) 启动发送

-单次发送(直到存满设置的储存深度(4k))

-循环发送

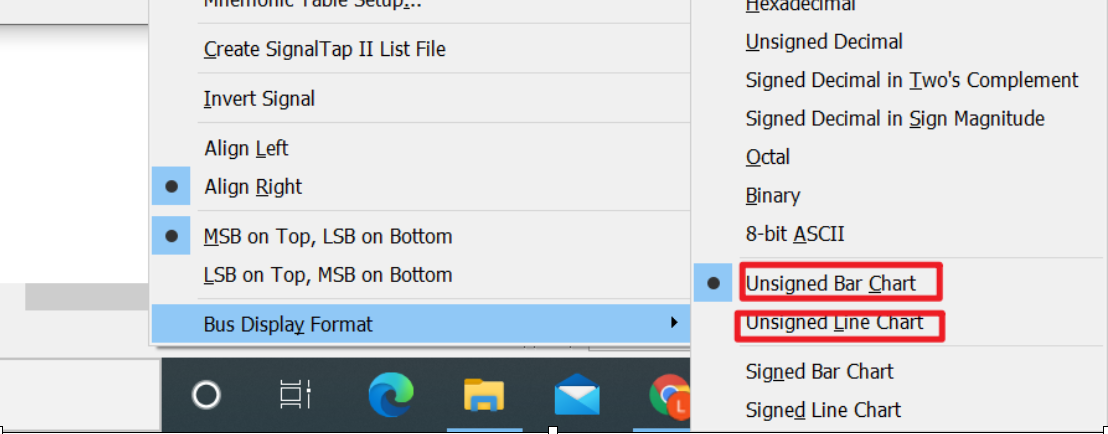

(4)波形显示

点击鼠标右键->Bus Display Format

-无符号条状显示

-无符号线状显示

4.利用In-System Memory Content Editor 工具修改ROM中的数据(将三角波改为正弦波)

(1)进入该工具界面没有出现rom表的数据,原来是自己在建立ROM IP核的时候没有勾选上使能该工具按钮。

(2)数据的读出和写入

-读出

-写入

()

()

(3)将正弦波数据写入

-1.在rom标号那里鼠标右键,导入正弦波的数据,即sine.mif文件;

-2.点击写入按钮

点击写入,此时就将sine.mif的数据写入到FPGA里的ROM了;

(4)验证

回到逻辑分析仪调试工具,点击单次发送,可以看到波形已经变为正弦波了,验证成功。

5.小结

之前第一遍建立工程,IP核的时候,仿真ROM波形图时q端口始终为高阻状态,没解决问题,不知道是ip核步骤不对,还是.mif文件没有数据,后面重新建了工程,重来一遍就正常了。

本节在学习IP核ROM的调用中,不仅学习了ROM的相关知识,也学会了嵌入式逻辑分析仪(Signal Tap II )和内存编辑工具(In-System Memory Content Editor )的使用。

特此记录,下一篇FIFO我来了。

参考:

1.小梅哥视频教程

2.小梅哥FPGA 系统设计与验证实战指南

浙公网安备 33010602011771号

浙公网安备 33010602011771号