高速USB2.0外设控制器接口设计

1、芯片选型:CY7C68013A;

2、介绍:赛普拉斯半导体公司 (赛普拉斯)的 EZ-USB FX2LP(CY7C68013A/14A) 是高集成、低功耗 USB 2.0 微控制器EZ-USB FX2™ (CY7C68013) 的一个低功耗版本;

3、软件:8051 代码运行介质:

内部 RAM,通过 USB 下载;

内部 RAM,从 EEPROM 加载;

4、应用

(1)低速设备(10-100kbps):键盘,鼠标

(2)全速设备(500kbps-10mbps):音频、麦克风

(3)高速设备(25-400mbps):视频、图像

5、校验方式(CRC)

(1)CRC5:x^5 +x^2 +1 (除数100101)

(2)CRC16:x^16 +x^15 +x^2+1(除数1100000000101)

6、传输方式

Usb2.0能够了传输方式(根据设备的应用划分)有4种,具体如下:

(1)配置传输

主机控制从机采用传输方式,步骤如下:

①主机发出一个配置传输令牌包

②主机发出配置数据包

③从机给主机一个应答包

(2)块传输

主要从来传输大批量数据,比如U盘,步骤如下:

①主机发出一个读数据/写数据传输令牌包

②主机发出写数据包/从发出读数据包

③从机给主机一个写应答包/主机给从机一个读应答包

(3)同步传输

针对像音频,视频类的设备,数据传输实时性高,因此专门定义了这种传输类型

步骤如下:

①主机发出一个读同步传输读数据令牌包(每隔一定的时间轮训)

②从机给主机数据包

(4)中断传输

针对终端类设备,像键盘,鼠标,针对这种设备定义了专门的传输类型,步骤如下:

①主机发出一个读终端传输读数据令牌包(每隔一定的时间轮训)

②从机给主机数据包

7、USB解决方案

针对USB这种通用串行总线,全球有专门的厂家产生usb解决方案的芯片,目前所熟知的全球最大的解决方案的公司cpress,在FPGA开发中也会用这些的解决方案;我们只需要通过芯片预留的GPIF接口和FIFO_SLAVE接口,将FPAG与USB进行连接。

8、信号介绍

Slwr_n : 写有效信号 芯片输入信号

Slrd_n : 读有效信号 芯片输入信号

Sloe_n : 读数据使能信号 芯片输入信号

port_sel[1:0] : 端口选择 芯片输入信号(00:EP2、01:EP4、10:EP6、11:EP8)

Ifclk : 芯片时钟 芯片输出信号

fd[15:0] : 数据(1次两字节) 双向

(Flaga、Flagb、Flagc、Flagd):对应EP2、4、6、8的端口缓存标志,如果该端口为读端口标志位高电平表示非空,如果是写端口,写之前单个缓存空的时候标志位低电平,当写入数据后没有满则为高电平,当单个缓存写满后变为低电平

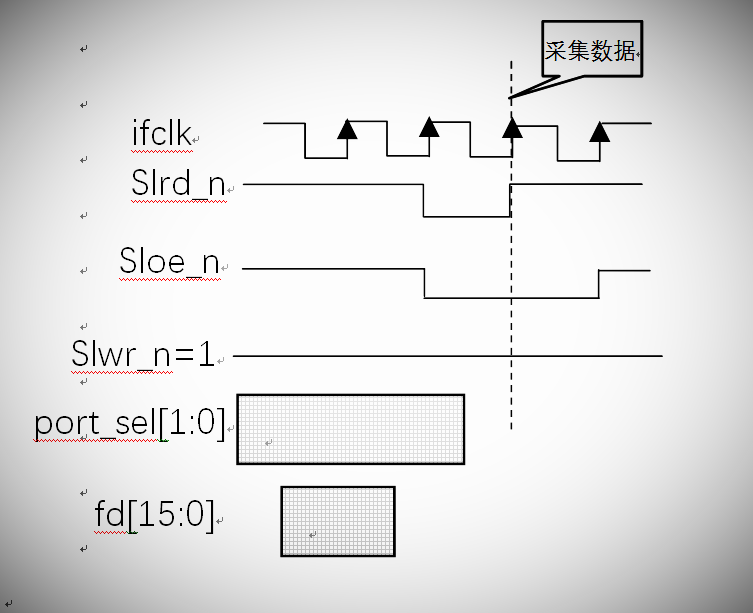

9、接受usb数据时序

10、接收USB数据接口代码

1 module exfx2_receive(if_clk, rst_n, slrd_n, sloe_n, slwr_n, port_sel, fd, flags, wr_en, wr_clk, wrdata, full); 2 3 input if_clk; 4 input rst_n; 5 6 //usb接口 7 output reg slrd_n; //读有效信号 8 output reg sloe_n; //读数据使能 9 output reg slwr_n; //写有效信号 10 output [1:0] port_sel; //端口选择 11 input [15:0] fd; //数据线 12 input flags; //缓存标志 13 14 //fifo写接口 15 output reg wr_en; 16 output wr_clk; 17 output reg [15:0] wrdata; 18 input full; 19 20 reg [1:0] state; 21 parameter S0 = 2'd0; 22 parameter S1 = 2'd1; 23 parameter S2 = 2'd2; 24 25 assign port_sel = 2'b00; 26 27 always @ (posedge if_clk, negedge rst_n) 28 begin 29 if(!rst_n) 30 state <= S0; 31 else 32 case(state) 33 S0 : if(flags) 34 state <= S1; 35 S1 : state <= S2; 36 S2 : state <= S0; 37 default : ; 38 endcase 39 end 40 41 always @ (posedge if_clk, negedge rst_n) 42 begin 43 if(!rst_n) 44 begin 45 slrd_n <= 1'b1; 46 sloe_n <= 1'b1; 47 slwr_n <= 1'b1; 48 end 49 else 50 case(state) 51 S0 : begin 52 slrd_n <= 1'b1; 53 sloe_n <= 1'b1; 54 slwr_n <= 1'b1; 55 end 56 S1 : begin 57 slrd_n <= 1'b0; 58 sloe_n <= 1'b0; 59 slwr_n <= 1'b1; 60 end 61 S2 : begin 62 slrd_n <= 1'b1; 63 sloe_n <= 1'b0; 64 slwr_n <= 1'b1; 65 end 66 default : ; 67 endcase 68 end 69 70 assign wr_clk = if_clk; 71 72 always @ (posedge if_clk, negedge rst_n) 73 begin 74 if(!rst_n) 75 begin 76 wr_en <= 1'b0; 77 wrdata <= 16'd0; 78 end 79 else 80 if(state == S2 && (~full)) 81 begin 82 wrdata <= fd; 83 wr_en <= 1'b1; 84 end 85 else 86 wr_en <= 1'b0; 87 end 88 89 endmodule

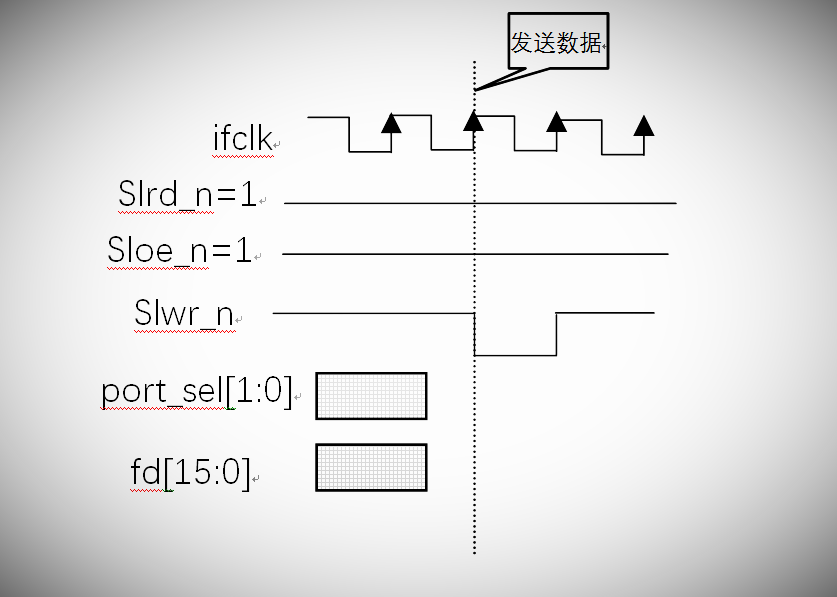

11、发送给usb数据时序

12、发送给USB数据接口代码

module ezfx2_trans(tr_en, if_clk, rst_n, fd, slwr_n, flagw, rd_en, rd_clk, rddata, empty); input tr_en; input if_clk; input rst_n; inout [15:0] fd; output reg slwr_n; input flagw; //fifo读接口 output reg rd_en; output rd_clk; input [15:0] rddata; input empty; reg [1:0] state; parameter S0 = 2'd0; parameter S1 = 2'd1; parameter S2 = 2'd2; assign fd = (slwr_n == 1'b0) ? rddata : 16'hzzzz; always @ (posedge if_clk, negedge rst_n) begin if(!rst_n) state <= S0; else case(state) S0 : if(tr_en && (~empty)) state <= S1; S1 : state <= S2; S2 : state <= S0; default : ; endcase end always @ (posedge if_clk, negedge rst_n) begin if(!rst_n) slwr_n <= 1'b1; else case(state) S0 : slwr_n <= 1'b1; S1 : slwr_n <= 1'b0; S2 : slwr_n <= 1'b1; default : ; endcase end always @ (posedge if_clk or negedge rst_n) begin if(~rst_n) rd_en <= 1'b0; else if(tr_en && (~empty)) rd_en <= 1'b1; else rd_en <= 1'b0; end assign rd_clk = if_clk; endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号