PCB制作时的EMC避坑学习《PCB电磁兼容技术设计实践》

第二章 旁路、去耦和储能

1.电容器等效电感称为等效串联电感(ESL),不过现在用的很少了。

2.在选择电容时,应该选择其ESR,ESL都很小的电容。

3.一定要尽量减少电容端的引线。

4.三端电容器:信号线抑制EMC好搭档。除了电感型滤波器,任何低通滤波器都要使用旁路电容。如果将电容的输入和输出端分开,构成三端电容器,则这种引线电感可以利用。这时,引线电感与电容一起构成T型滤波器,极大地改善了高频衰减特性。为了获得最好的效果,在使用时应将中间的导线(地线)直接接到低电感地上,否则这根引线上的电感将破坏电容器的滤波效果。

5.由于电容值小的瓷介电容自谐振频率高,在高频时工作较好,所以0.1μF以下的瓷介电容可以作为高频电路的去耦电容,可根据要滤除的不同频率范围来选择电容值。电解电容器自谐振频率较低,适用于低频或直流电路的滤波、耦合和旁路。

6.如果用到接口信号线上,则在三端电容前一定要加过压保护器件,因为三端电容的耐压值一般都不是很高。

7.旁路电容:靠近电源的滤波电容,用来控制电源向外输出的干扰。旁路电容一般作为高频旁路器件来减小对电源模块的瞬态电流需求,一般在10μF~470μF 范围内。若PCB板上有许多集成电路、高速开关和具有长引线的电源,则应该选择大容量的电容或采用多个电容。旁路电容的必须通过的最高频率为0.35 Fbypass ≈ trise/fall。式中∶Fbypm:旁路电容的最高频率;tis/full:数字信号上升/下降沿的时间。可以通过该频率来设置旁路电容容值。

8.去耦电容:靠近IC,用来处理IC开关时对电源造成的尖峰波动。在减小电源和地平面上纹波、噪声和毛刺很有效果。去偶电容容值:C = ΔI*(Δt/ΔV)。式中∶ΔI——器件导通和截止二种状态下流过电源引脚电流的差值;Δt————开关时间,是器件输出脉冲信号的上升沿或下降沿;ΔV————逻辑器件工作允许的电源电压值的变化。同时,电容的引线要尽可能的距离芯片近。原则上,集成电路的每个电源引脚都应布置一个0.01μF的瓷片电容。对于抗噪能力弱、关断时电源变化大的器件,应在芯片的电源脚和地脚之间直接接入去耦电容。

9.储能电容:提供直流功率。可以在电源旁边放一个。

第三章 单板传输线设计(阻抗匹配在这里呈现)

1.传输线是一个分部参数系统,描述其基本参量有两个:特征阻抗和传播常数。当传输线端接负载的阻抗等于其特性阻抗时,所传输的信号能量将完全被负载所接收,不会有信号被反射回去,这种情况称负载与传输线是匹配的。如果传输线在终端不匹配,则电路的性能问题和EMI就会出现,包括电压过冲、电压欠冲、信号上升沿延缓、脉冲波形畸变等。

什么是阻抗?这可能是较多人都不清楚的一个概念。阻抗控制对于确保信号完整和降低杂波噪声是有好处的。但用抽象和复杂高速逻辑原理来讲述,动辄就搬来一堆数学公式与物理学语言,这对新手或隔行者难以有启迪作用,就是对老手这样讲述也难有事半功倍的效果。对于PCB上传输线阻抗的讲述,读者可以先想象一下∶朝阳初升的早晨,一位老者在很大的后花园浇花,他浇花用的不是喷壶(由于花很多),而是用一根长长的软管,将自来水从屋檐下的水龙头上引过来,软管中一端,老者捏在手里,依靠手的握力来浇着高低远近的花。当老者手里的握力恰到好处时,水管里的水洒落在目标区里;当老者用力过度时,水柱射程就可能会太远,就会腾空越过目标区而浪费资源,甚至还有可能导致水压无处宣泄,以致向来源处反弹造成软管从水龙头上挣脱,浇花任务就会失败;假如老者用力不够,则会造成挤压不够导致射程太近,照样得不到想要的结果。惟有手用力恰到好处,才能有满意的结果。

在PCB上,信号沿导线在PCB上传输,此时,可以将传输线看成软管。而握管处就好像传输线的“接受器”一样,水龙头处就好像传输线上的“驱动器”(Driver)一样。而握管处所施加的压力,就好比板面上“接受器”(Receiver)元件所并联到工作地的电阻器一般,可用以调节其终点的特性阻抗,匹配接受端元件内部的阻抗需求。由上可知,当“信号”在传输线中飞驰旅行而到达终点,欲进入接受元件(如CPU或Memory 等大小不同的芯片)中工作时,则该信号线本身所具备的“特性阻抗”,必须要与终端元件内部的电子阻抗相互匹配才行,如此才不致使任务失败、白忙一场。一旦彼此未能匹配,则必将会有少许能量回头朝向“驱动器”反弹,进而形成信号反射的烦恼。

2.原则:当传输线本身的特性阻抗Z0被设计者设定为某个值时,则终端控管的接地的电阻器Zt也必须是某个值,如此才能协助传输线对Z0的保持。在Z0=Zt的情况下信号才是完整的。

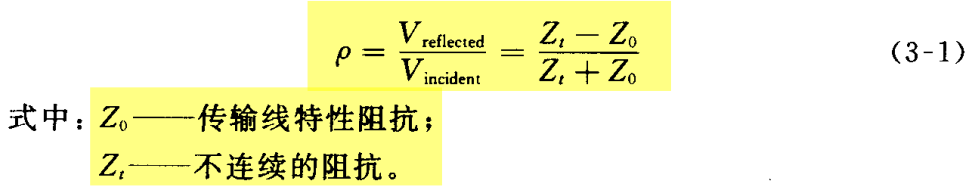

3.反射系数计算:

负载在短路时反射率为-1,而在开路时反射系数为1

4.消除反射的负面影响方法:

(1)降低系统频率以便在另一个信号加到传输线上之前传输线的反射达到稳态;

(2)缩短PCB走线以便反射在短时间达到稳态;

(3)阻抗匹配消除反射。

5.阻抗匹配方法:

5.1 源端匹配:驱动器的输出阻抗和电阻走线的阻抗匹配,通常称为源串联端接阻抗匹配。这种端接要求缓冲器阻抗与串联阻抗的和等于线的特征阻抗。

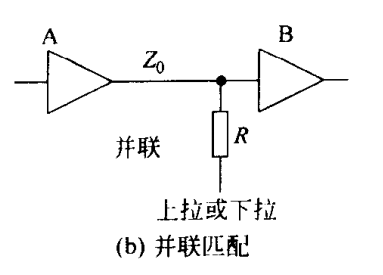

5.2 终端匹配:在终端进行阻抗匹配,使输入缓冲器的阻抗与匹配阻抗的和等于传输线阻抗。其中,作者需要的阻抗匹配方法主要为并联端接匹配

接收端并联匹配适用于单点对多点的连接,与发送端匹配不同,接收端匹配无需借助反射以建立电平,通过使匹配电阻Rp的阻值等于传输线阻抗,可实现接收端的阻抗匹配。如果传输线的阻抗为55Ω,那么Rp的值也为55Ω。

https://blog.csdn.net/sinat_15677011/article/details/104547189

6.串扰:当不同导线(传输线)产生的电磁场发生相互作用时就会产生串扰。串扰的幅度跟传输线间的平行长度成正比,即平行长度越长,串扰就越大。但这有一个极限,即平行长度达到一定程度后,串扰的幅度也到了极限,并不会随之增加了。一般可以通过加宽走线、降低信号层与平面层的介质厚度或采用低介电常数的介质可以降低传输线的特征阻抗。所谓串扰,一般是指某一回路中的电流或电压在邻近回路产生了电流或电压,从而影响了该邻近回路的正常工作。

● 布线条件允许的情况下,尽量拉大传输线间的距离;或者应该尽可能地减少相邻传输线间的平行距离(累积的平行距离),最好在不同层间走线。

● 在获得相同目标特征阻抗的情况下,应该使布线层与参考平面(电源平面或地平面)间的介质层尽可能薄,这样就加大了传输线与参考平面间的耦合度,减少相邻传输线间的耦合。

● 对系统中关键传输线,可以改用差分线传输,以减少其他传输线对它的串扰;也可以将关键信号线夹在两个地平面层内。

● 相邻两层的信号层(中间没有平面层隔离)走线方向应该垂直,尽量不要平行走线以减少层间的串扰。

● 在保证信号时序的情况下,尽可能选择转换速度低的元器件,这样电场与磁场的变化速率慢一点,从而可降低串扰;

● 尽量少在表层走线,因为表层线的电场耦合比中间层的要强(表层线只有一个参考平面)。

7.3W原则:3W原则可描述为∶二平行走线间距离间隔必须不小于单一走线宽度的3倍;另一种描述是,二平行走线之间的边缘距离间隔必须不小于单一走线宽度的2倍。比如,时钟线宽为6mil,则其他走线只能在距离这条线2×6mil 以外的地方布线,或者保证边到边距离大于12mil。

第四章 单板时钟部分的设计

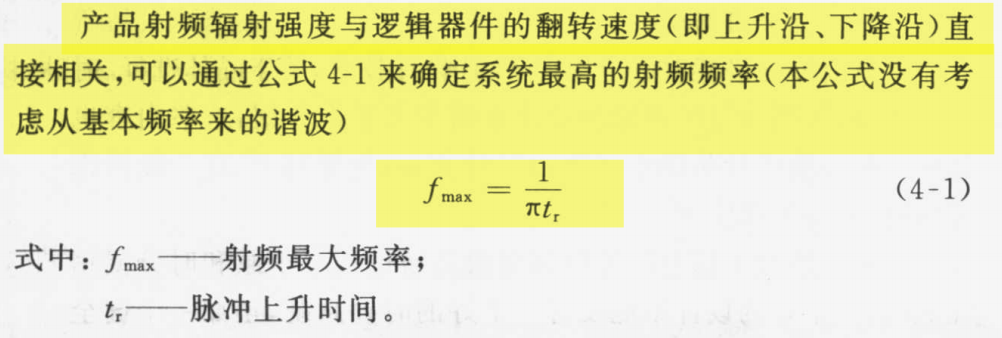

1.

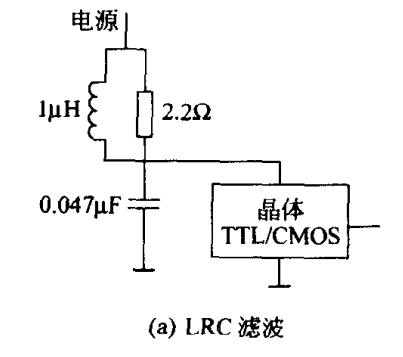

2.时钟电源滤波电路

为减小地电位跳跃和电源噪声的影响,时钟源电路部分需要采用滤波电路,这些电路在20MHz以上的频率范围内衰减量最大可达20dB,使用两级滤波器可以使衰减加倍,必须将滤波器尽可能地靠近振荡器的电源输入引线,以最大程度减小射频环路电流。

3.时钟系统EMC设计

在PCB上时钟电路区域只布与时钟电路有关的器件,避免布设其他电路或与其他电路靠近,在时钟电路附近或者通过时钟区域处、时钟晶体附近或下面不要布其他信号线!时钟电路和晶体下铺设地平面将提供一个映像平面,可以降低对相关晶体和时钟电路产生共模电流,从而降低射频辐射,地平面对差模射频电流同样也有吸收作用,这个平面必须通过多点连接到完整的地平面上,并且要求通过多个过孔,这样可以提供低的阻抗,为增强这个地平面的效果,时钟发生电路应该与这个地平面靠近。在时钟发生电路、晶体下使用地平面时,不能让任何信号线穿过该平面,因为这违反了映像平面的功能,如果让信号穿越这个地平面的话,就会存在很小的地环路并影响地平面的连续性,这些地环路在高频时将会产生问题。

4.映像空间

射频电流必须经由一个先前定义好的路径或其它路径,回到电流源;简言之,这个回传路径(return path)就是一种映像平面。映像平面可能是原先的走线的镜像(mirror image),或位于附近的另一个路径----亦即,串音(crosstalk);映像平面也许就是电源平面、接地平面,或者自由空间(free space)。射频电流会以电容或电感的形式与任何传输线耦合,只要此传输线的阻抗比先前定义好的路径的阻抗小。不过,为了符合EMC标准,必须避免让自由空间成为回传路径。

第五章 单板电源部分设计

1.尽可能选用主流器件,而不要一味根据以往成功经验。

2.所有流出的电流最终必须回到源端,回流路径为阻抗最小的路径,在多数情况下是电感最小的路径。当在回流路径上有不连续阻抗点存在时,因为电流需要绕过不连续点,所以回流路径面积会增加,增加的回流路径面积导致了电感的增加,这会破坏信号完整性,增加系统的 EMI 分量。

3.过压保护:过电压保护的基本原理是在瞬态过压冲击过程中,通过保护器件在配电线路与地电位或电位补偿系统之间建立起一个等电位。能够作为电压过压保护的器件很多,一般有放电管、压敏电阻、TVS管等器件。

第六章 接地设计

1.设备的地线要能够承受漏电流泄放和保护器件动作产生的泄放电流。地线有电流通量容限的要求。电流通量容限的上下限,可以参考设备的所要考虑耐受的意外泄放电流的数值,但由于这个泄放电流往往很大,根据这个电流选取导线肯定不合适,根据经验,可以按I/√45选取(I为泄放电流)。

2.PCB分层总的原则是信号线一定有存在相邻完整的映像回流平面,不可存在地环路,重要信号线、关键信号线要受到保护。

3.数字电路和低频模拟电路接地方法∶地线在印制板上以指叉形状或树权形状连接各元器件的地线,推荐支线地宽度不小于50mil,母线地宽度不小于100mil;对于较高频率部分,推荐另一层的相对应部分做成接地参考平面。推荐的汇接点在内部电源或外部输入电源的大滤波电容的接地点处;低频模拟电路的汇接点也可选在输入小信号的接地处。

4.为了减小耦合效应,要求所有的电源平面物理上都比其相邻的地平面小 20H,这就是所谓的 20H 原则。遵循20H原则,可以将电源对附近电路的耦合降低70%左右,当这个距离为100H时,几乎可以降低耦合98%。H为板厚,双面板感觉最好在电源线下面有地线并地线比电源线宽。

5.如果必须对地线层进行分割,而且必须通过分割之间的间隙布线,可以先在被分割的地之间进行单点连接,形成两个地之间的连接桥,然后通过该连接桥布线。这样,在每一个信号线的下方都能够提供一个直接的电流回流路径,从而使形成的环路面积很小。

6.采用光隔离器件或变压器也能实现信号跨越分割间隙。对于前者,跨越分割间隙的是光信号;在采用变压器的情况下,跨越分割间隙的是磁场。还有一种可行的办法是采用差分信号,信号从一条线流入再从另外一条信号线返回,这种情况下,不需要地作为回流路径。在实际工作中一般倾向于使用统一地,而将PCB分区为模拟部分和数字部分。模拟信号在电路板所有层的模拟区内布线,而数字信号在数字电路区内布线。只有将数字信号布线在电路板的模拟部分之上或者将模拟信号布线在电路板的数字部分之上时,才会出现数字信号对模拟信号的干扰。出现这种问题并不是因为没有分割地,真正的原因是数字信号的布线不适当。将地分割开,在A/D转换器下面把模拟地和数字地部分连接在一起。采取该方法时,必须保证两个地之间的连接桥宽度与IC 等宽,并且任何信号线都不能跨越分割间隙。

7.如果对混合信号PCB设计采用统一地的做法心存疑虑,可以采用地线层分割的方法对整个电路板布局布线,在设计时注意尽量使电路板在后边实验时易于用间距小于0.5in的跳线或0Ω电阻将分割地连接在一起。注意分区和布线,确保在所有的层上没有数字信号线位于模拟部分之上,也没有任何模拟信号线位于数字部分之上。而且,任何信号线都不能跨越地间隙或是分割电源之间的间隙。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步