名词、概念解释

@

- 概念集

- Bootloader

- ZYNQ资源和使用接线:

- ZYNQ OCM和DDR配置(都是RAM)

- ZYNQ MIO和EMIO

- 处理器与处理器核:

- 处理器外设:

- 总线:

- PL、PS以太网:

- ZYNQ外设驱动过程:

- 串口驱动过程:

- MII、GMII、RGMII 接口

- 常见存储器

- 堆栈:

- STM32 :

- EEPROM 存储器

- I2C总线

- UART 传输器/RS232接口 /RS485接口

- NOR、 NAND、 SPI、 CFI、 JEDEC、NVRAM

- SPI总线和QSPI

- SPI、I2C、UART三者关系

- CAN通信

- GPIO

- DMA控制器

- 寄存器

- FAT32、exFAT、NTFS之间的区别

- SD、TF卡速度等级

- TCP/IP协议栈

- UART -- FIFO缓冲区:

- 领航者ZYNQ开发板:

- POSIX

- CDT

概念集

嵌入式工程师需要非常扎实的C语言功底,

能基本看懂PCB硬件原理图,怎么也得知道哪些引脚是相接的吧

基本的驱动需要知道,比如PWM、串口、iic、SPI、DMA等,这些其实都不难需要了解

基本的网络协议,比如TCP三次握手,ARP协议、DHCP协议、ICMP协议、静态IP和动态IP的区别等

代码管理工具比如git或者svn

对于通讯协议,最基本的是把它分为物理层和协议层。

物理层规定通讯系统中具有机械、电子功能部分的特性,确保原始数据在物理媒体的传输。

协议层主要规定通讯逻辑,统一收发双方的数据打包、解包标准。

简单来说物理层规定我们用嘴巴还是用肢体来交流,

协议层则规定我们用中文还是英文来交流。

“总线”指多个外设共用的信号线。外设 与 处理器核 的通信道路。

全双工、半双工、单工:

举个半双工例子,一条马路只够一辆车通过,当有两辆车对开,这种情况下就只能一辆先过,另一辆再开,这说明了半双工的原理。

1、一般而言,嵌入式系统的构架可以分为4个部分:分别是(处理器)、存储器、输入/输出和软件,一般软件亦分为操作系统相关和(应用软件)两个主要部分。

2、根据嵌入式系统使用的微处理器,可以将嵌入式系统分为嵌入式微控制器,(嵌入式DSP处理器),(嵌入式微处理器)以及片上系统。

3、操作系统是联接硬件与应用程序的系统程序,其基本功能有(进程管理)、进程间通信、(内存管理)、I/O资源管理。

4、从嵌入式操作系统特点可以将嵌入式操作系统分为(实时操作系统)和分时操作系统,其中实时系统亦可分为(硬实时系统)和软实时系统。

5、内核负责管理各个任务,或者为每个任务分配CPU时间,并且负责任务之间的(通信),内核的基本服务是(任务切换)。

6、嵌入式开发一般采用(宿主机/目标机方式)方式,其中宿主机一般是指(PC机或者台式机)。

7、哈佛体系结构数据空间和地址空间(分开),ARM7TDMI采用(冯诺依曼体系)的内核架构。

8. ARM7TDMI采用(3)级流水线结构,ARM920TDMI采用(5 )级流水线。

9 .按操作系统的分类可知,Dos操作系统属于顺序执行操作系统,Unix操作系统属于(分时)操作系统,VxWorks属于(实时嵌入式)操作系统。

10、ARM7TDMI中,T表示支持16位Thumb指令集,D表示(在片可调试),M表示内嵌乘法器Multiplier,I表示(嵌入式ICE),支持在线断点和调试。

抢占式和非抢占式的区别:

执行的过程中对中断处理方式不一样,抢先式:某一中断执行完成后,如果有更高优先级的任务处于就绪状态,将执行更高优先级任务,而非抢占式不一样,一个任务只有主动放弃CPU的控制权,其它任务才能够获得CPU的控制权。

需求分析--方案设计--方案评审--方案实施--集成测试、性能测试、可靠性测试--评审总结

ARM是32位的单片机,具有比较强的事务管理功能,可以用来跑界面、操作系统以及应用程序等;

DSP主要是用来计算的,比如进行加密解密、调制解调等,优势是强大的数据处理能力和较高的运行速度;

FPGA可以用VHDL或verilog HDL来编程,灵活性强,由于能够进行编程、除错、再编程和重复操作,因此可以充分地进行设计开发和验证。当电路有少量改动时,更能显示出FPGA的优势,其现场编程能力可以延长产品在市场上的寿命,而这种能力可以用来进行系统升级或除错。

DSP是通用的信号处理器,用软件实现数据处理;FPGA用硬件实现数据处理

51单片机是MCU;

ARM型号:M0到A8、A9越来越高端;

ARM架构:V1到V7、V8越来越高端。

ARM系列CPU说明

1、ARM7系列

该系列主要针对某些简单的32位设备,作为目前较旧的一个系列,ARM7处理器已经不建议继续在新品中使用。主要包括ARM7TDMI-S(ARMv4T架构)和ARM7EJ-S(ARMv5TEJ架构)。

2、ARM9系列

主要针对嵌入式实时应用,主要包括ARM926EJ-S、ARM946E-S和 ARM968E-S。

3、ARM11系列

主要应用在高可靠性和实时嵌入式应用领域,主要包括ARM11MPCore、ARM1176、ARM1156、ARM1136。

4、Cortex-R系列

Cortex-R,代表实时的意义(Real-Time),目标是实时任务处理,主要应用领域包括汽车、相机、工业、医学等。该系列处理器主要包括Cortex-R4、Cortex-R5、Cortex-R7、Cortex-R8、Cortex-R52、Cortex-A17。

5、Cortex-M系列

Cortex-M,代表微处理器的意义(Microcontrollers),目标是最节能的嵌入式设备,主要应用领域包括汽车、能源网、医学、嵌入式、智能卡、智能设备。传感器融合、穿戴设备等。该系列处理器主要包括Cortex-M0、Cortex-M0+、Cortex-M3、Cortex-M4、Cortex-M7、Cortex-M23、Cortex-M33、Cortex-M35P。

6、Cortex-A系列

Cortex-A,代表的是先进意义(Advanced),目标是以最佳功耗实现最高性能,主要应用领域包括汽车、工业、医学、调制解调器、存储等。Cortex-A也是目前应用最广的处理器版本。

CPU 力气大啥P事都能干,还要协调。

GPU 上面那家伙的小弟,老大让他处理图形,这方面处理简单,但是量大,老大虽然能处理,可是老大只有那么几个兄弟,所以不如交给小弟处理了,小弟兄弟多,有数百至数千个,而且是专门只干这行和只能干这行。

有源与无源元件:

简单地讲就是需能(电)源的器件叫有源器件,无需能(电)源的器件就是无源器件。有源器件一般用来信号放大、变换等,无源器件用来进行信号传输,或者通过方向性进行“信号放大”。容、阻、感都是无源器件,IC、模块等都是有源器件。(通俗的说就是需要电源才能显示其特性的就是有源元件,如三极管。而不用电源就能显示其特性的就叫无源元件)

嵌入式系统的硬件核心部件是嵌入式处理器,嵌入式处理器有四种类型

第一种 微处理器(MPU)Motorola的68K系列和Intel的X86系列

第二种 微控制器(MCU、单片机)

第三种 数字信号处理器(DSP)

第四种 片上系统(SOC)

这里以偏重嵌入式Linux(ARM)驱动开发为例,给出一条入门的路线。

1、买一款使用广泛、资料多的ARM开发板。因为使用的人多,你遇到的问题别人可能早就遇到并解决了,这样能省很多时间,并且提高自信心。可以到某宝上看看板子。因为是学习使用,最好便宜又适用的。

2、使用vmware安装一个ubuntu系统。在vmware软件中设置物理桥接方式上网。在ubuntu设置好samba服务、nfs服务、tftp服务。

3、首先自己动手亲自编译u-boot、kernel,烧写到板子上(注:有可能rootfs不提供源码,而是提供img镜像文件)。

4、自己修改kernel,并编译busybox,烧写到板子,在板子挂载NFS,在虚拟机交叉编译一个Helloworld程序,并在板子上运行。

5、根据兴趣,开始捣鼓:u-boot、kernel、应用层开发、QT开发。

6、选择自己重点关注方面,继续研究。

这个路线不一定要严格遵守时间轴。

Bootloader

BootLoader是在嵌入式系统复位启动时,操作系统内核运行前,执行的一段程序。

通过BootLoader,初始化硬件设备,建立内存和I/O空间映射图,为最终加载操作系统内核调整好适当的系统软硬件环境。

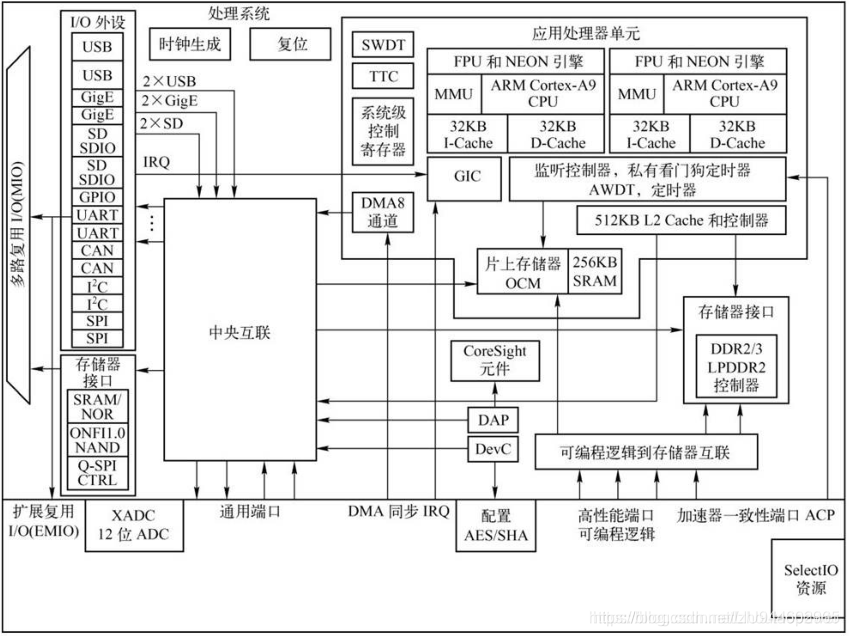

ZYNQ资源和使用接线:

1、JTAG插座指针,接7020的TCK_0 、TMS_0、 TDO_0、 TDI_0、 INIT_B

2、PS_MIO48 、PS_MIO_49接电平转换(1.3--1.8)再引出UART1_TX、UART1_RX

(需在vivado进行TX、RX 的MIO口配置)

3、QSPI接6个MIO 接FLASH芯片128Mbit = 16 MB

4、SDIO接6个IO口(4data),其中SDIO1_D3还要一分为二;如果有CD、WP还需接两个口

5、DDR : MT41K256M16HA-125。两个DDR除了data口和部分控制口,很多口都接的一样的7020上的接口。

6、PL端接以太网

7、网络口12个MIO,接6个TX(1时钟 1控制 4data)、6个RX (1时钟 1控制 4data)。 88E1518芯片,RGMII0

8、USB 12个MIO(8data)

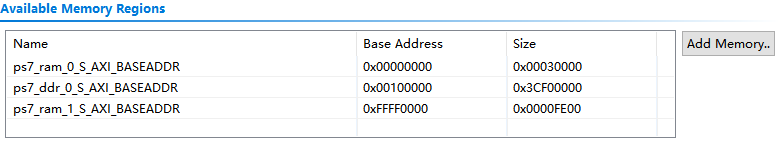

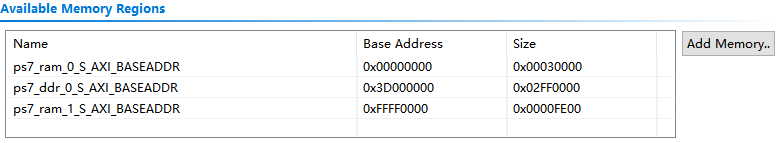

ZYNQ OCM和DDR配置(都是RAM)

CPU0:

ram0:包含3块64KB的OCM

ddr:CPU0的启动地址,以及DDR占用大小

ram1:包含64KB的OCM

CPU1:

ram0:包含3块64KB的OCM

ddr:CPU1的启动地址,以及DDR占用大小

ram1:包含64KB的OCM

由资源图可知,OCM是共享的,CPU0和1可以操作同一个地址的OCM;

DDR是独占的,采用把总DDR分成合适的两块,分配给CPU0和1 。

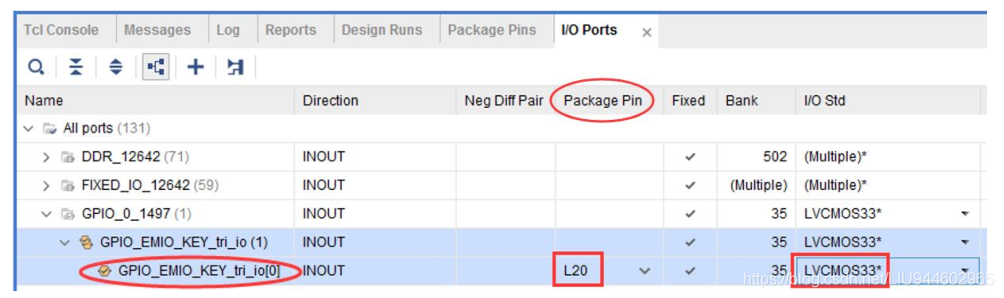

ZYNQ MIO和EMIO

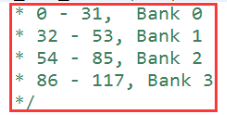

ZYNQ GPIO 接口信号被分成四组,分别是从 BANK0 到 BANK3。

BANK0 和 BANK1 中共计 54个信号通过 MIO 连接到 ZYNQ 器件的引脚上,这些引脚属于 PS 端;

BANK2 和 BANK3 中共计 64 个信号则通过 EMIO 连接到了 ZYNQ 器件的 PL 端。

GPIO_MIO 可连接到外设 LED 和 KEY 上,这些 GPIO_MIO 当作 GPIO 使用来驱动

外设 LED 和 KEY。由于这些引脚都是 PS 的引脚,不需要在 PL 中进行引脚位置约束。

而GPIO_EMIO需要管脚约束,例如PL的L20脚接一个按键,L20位于bank3,电压为3.3V,需配置如下,再保存。即完成了管脚约束。

处理器与处理器核:

STM32 系列处理器中使用 ARM Cortex M0/3/4/7 核作为处理器核。

在 ARM 提供的处理器核 IP(Processor IP) 基础上,ST 为其添加了一系列外设,包括串口,定时器,DMA等,以及 SRAM 和片上 FLASH 这样的 Memory ,一起流片做成了一颗 STM32。

STM32这样一个微处理器,其实也是一个 SoC (System on Chip)片上系统。

接着断言:Zynq 与其说是 FPGA ,不如说 Zynq 就是 SoC。而其处理器核为 ARM A9。

那么 Zynq 的 FPGA 逻辑部分怎么说,实际上 PL (Programable Logic 指 FPGA 中的可编程逻辑资源)需要听 ARM 核的指挥,某种程度上 PL 是 ARM 核的一项外设,或者说协处理器。

处理器外设:

外设在处理器系统中指的是 GPIO,UART,DMA 这些处理器的组件,他们听从处理器核的指挥,干他们自己的活儿,比如打印串口信息。对于 STM32 这样的单片机来说,外设只有一种,那就是固化的硬件电路,这和处理器核是一样的,都是不能修改的 ASIC (专用硬件电路)。

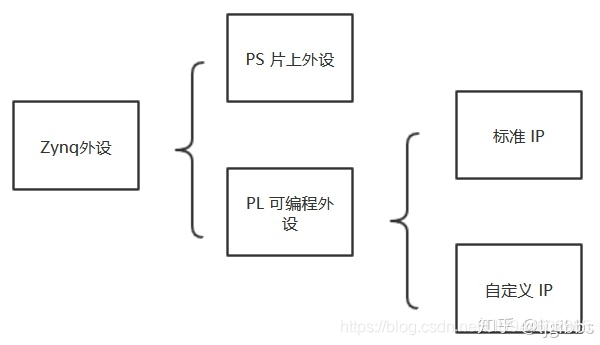

但 Zynq 的情况就有所不同,拥有两类不同的外设。

一类是和 STM32 单片机相同的PS上硬件电路外设,这部分硬件电路和处理器核一起组成了 Zynq 的处理器系统(Processor System)。

另一类外设由 FPGA 部分的可编程逻辑(PL)构成,它们最大的特点在于可编程,无论是外设的数量还是类型。某个部分的逻辑资源可以在先前作为串口使用,过会儿就可以作为 SPI 接口,这种变化甚至能够动态进行。在 Zynq 上,我们可以使用PL硬件资源部署 N个硬件串口等等。。。

PL 外设相比 PS 外设的缺点在于速度要慢一些,稳定性也可能稍差。

所以,Zynq 拥有两类外设:PS 或者 PL。其中 PL 外设又可以分为两类:标准 IP 和自定义 IP。标准 IP,包括 FIFO,RAM,AXI-Uart,AXI-Jtag 等等。

总线:

SoC 还有一个很重要的组成部分是总线。总线将处理器核和外设连接到一起。

处理器核的指令就通过总线传输到各个外设。

Zynq 中主要的总线是 AXI4 总线,这是一种由 ARM 提出的标准化 IP 间总线。

Zynq 中不只存在 AXI4 系列总线,在 PS 中 ARM 核和片上外设之间的连接通过 APB,AHB 总线进行,和 STM32 使用相同的总线。APB,AHB 总线和 AXI4 类似,实际上他们都属于 ARM AMBA 协议族。

在软件编程的过程中,总线操作由底层 IO 驱动负责,所以并不需要加以关注。但在编写硬件 IP 的过程中,需要对总线的接口加以了解。

PL、PS以太网:

use_axieth_on_zynq 设为0:将使用PS端以太网,

XPAR_XEMACPS_0_BASEADDR (0XE000B000)

use_axieth_on_zynq 设为1:将使用PL端以太网,

XPAR_AXIETHERNET_0_BASEADDR(0x41000000)

ZYNQ外设驱动过程:

https://zhuanlan.zhihu.com/p/58737537

驱动函数 实质是 对外设寄存器的读写操作。

BSP设置中勾选驱动,会从安装目录把驱动程序拷贝到项目下的bsp中。

硬件配置好后,外设会自动生成配置table,包括ID和绝对地址等等。

外设初始化套路:

1、定义外设信息结构体,利用ID获取外设信息,信息来自底层硬件;

XScuTimer_Config *ConfigPtr;

ConfigPtr = XScuTimer_LookupConfig(TIMER_DEVICE_ID);

2、定义外设实例结构体,调用初始化函数。作为全局变量供上层使用。

static XScuTimer TimerInstance;

Status = XScuTimer_CfgInitialize(&TimerInstance, ConfigPtr,

ConfigPtr->BaseAddr);

3、对外设的启动、停止等操作皆是读写寄存器。而读写最底层又皆是Xil_In32/ Xil_Out32 函数

void XScuTimer_Start(XScuTimer *InstancePtr)

{

u32 Register;

Xil_AssertVoid(InstancePtr != NULL);

Xil_AssertVoid(InstancePtr->IsReady == XIL_COMPONENT_IS_READY);

Register = XScuTimer_ReadReg(InstancePtr->Config.BaseAddr,

XSCUTIMER_CONTROL_OFFSET);

Register |= XSCUTIMER_CONTROL_ENABLE_MASK;

XScuTimer_WriteReg(InstancePtr->Config.BaseAddr,

XSCUTIMER_CONTROL_OFFSET, Register);

InstancePtr->IsStarted = XIL_COMPONENT_IS_STARTED;

}

串口驱动过程:

1、系统时钟配置初始化

2、UART0初始化

a)引脚的配置

b)FIFO缓冲器的使用

c)波特率的配置和数据帧格式的设置

3、串口收发程序:字节收发、字符串发送

MII、GMII、RGMII 接口

一般用于MAC和PHY的通信。

MII支持速率:10/100 Mbps

GMII支持速率:10M/100M/1000Mb/s

RGMII是Reduced GMII(吉比特介质独立接口),降低电路成本,使实现这种接口的器件的引脚数从22个减少到12个。

常见存储器

RAM、ROM和FLASH三大类。

RAM包括:SRAM、DRAM、SDRAM、DDR SDRAM、DDR2 SDRAM和DDR3 SDRAM

ROM包括:PROM、EPROM和EEPROM

FLASH包括:NOR FLASH和NAND FLASH,结合了RAM和ROM长处:

eMMC=NAND flash+controller+standard interface、

SD属于FLASH、

TF卡是(t-flash)又称micro SD、

SSD。

存储器的分级策略, 从快到慢分别是:

寄存器、

L1 cache(CPU缓存)、

L2 cache(CPU缓存)、

L3 cache(CPU缓存)、

内存、

硬盘/固态硬盘SSD。

固态硬盘的存储介质分为两种:

基于闪存的固态硬盘:采用FLASH芯片作为存储介质,这也是通常所说的SSD。

基于DRAM的固态硬盘:采用DRAM作为存储介质,应用范围较窄。

机械硬盘的原理:电磁存储

堆栈:

CPU干的活就是初始化MMU和TLB等等,其中比较关键的就是初始化堆栈(SP寄存器指向栈顶),前面也提及过,在链接的时候分配了堆栈空间,而堆栈对C语言函数是非常重要的。

栈的作用:一般来说函数调用或者中断,都会涉及到现场保护和现场恢复,被保护的现场实际上就是CPU的几个专用的reg,以及正在执行的函数的局部变量等数据,这些数据会被推进栈内,其相应的SP寄存器也会加上入栈数据的长度,在函数执行返回挥着中断返回时,栈内的数据按顺序再次出来,总体来说就是先进后出。

而堆的作用一般就是给系统动态分配存储空间的,包括用户经常调用的malloc说分配的空间,就是在堆里。简而言之,堆栈的完成初始化是为了c语言函数提供了环境。否则C语言是无法正确被执行的。

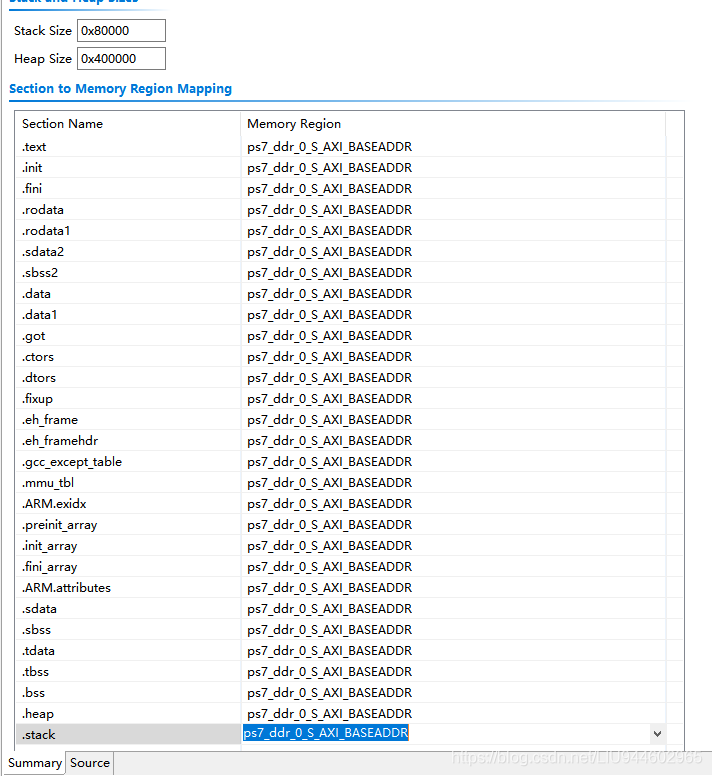

zynq启动需要OCM和DDR(也有只利用OCM启动的教程),如图可以看到堆栈都是占用的DDR内存:

STM32 :

一般我们说STM32内部FLASH的时候,都是指主存储器区域,它是存储用户应用程序的空间,芯片型号说明中的1M FLASH、2M FLASH都是指这个区域的大小。

主存储器分为两块,共2MB,每块内分12个扇区,其中包含4个16KB扇区、1个64KB扇区和7个128KB的扇区。

如我们实验板中使用的STM32F429IGT6型号芯片,它的主存储区域大小为1MB,所以它只包含有表中的扇区0-扇区11。

系统存储区是用户不能访问的区域,它在芯片出厂时已经固化了启动代码,它负责实现串口、USB以及CAN等ISP烧录功能。

STM32不可以跑Linux,

不过uclinux貌似可以,得外加nor flash和sram才可以,所以实用价值不高。

EEPROM 存储器

EEPROM 是一种掉电后数据不丢失的存储器,常用来存储一些配置信息,以便系统重新上电的时候加载之。EEPOM芯片最常用的通讯方式就是I2C协议

本实验板中的 EEPROM 芯片(型号:AT24C02)的 SCL及 SDA 引脚连接到了 STM32 对应的I2C引脚中,结合上拉电阻,构成了I2C通讯总线,它们通过I2C总线交互。EEPROM芯片的设备地址一共有 7 位,其中高 4 位固定为:1010 b,低 3 位则由 A0/A1/A2 信号线的电平决定,图中的 R/W是读写方向位,与地址无关。

1、编程要点

为了使工程更加有条理,我们把读写 EEPROM 相关的代码独立分开存储,方便以后移植。在“工程模板”之上新建“bsp_i2c_ee.c”及“bsp_i2c_ee.h”文件,这些文件也可根据您的喜好命名,它们不属于 STM32 标准库的内容,是由我们自己根据应用需要编写的。

(1) 配置通讯使用的目标引脚为开漏模式;

(2) 使能 I2C外设的时钟;

(3) 配置 I2C外设的模式、地址、速率等参数并使能 I2C外设;

(4) 编写基本 I2C按字节收发的函数;

(5) 编写读写 EEPROM 存储内容的函数;

(6) 编写测试程序,对读写数据进行校验。

引脚配置

根据硬件封装引脚为宏定义---利用宏初始化I2C GPIO引脚---使能I2C外设的时钟---使能I2C使用的GPIO的端口时钟---向GPIO初始化结构体赋值,把引脚初始化成复用开漏模式,要注意I2C的引脚必须使用这种模式---向寄存器写入参数,完成 GPIO 的初始化

模式配置

把 I2C 外设通讯时钟SCL的低/高电平比设置为 2,使能响应功能,使用 7 位地址 I2C_OWN_ADDRESS7 以及速率配置为 I2C_Speed(前面在 bsp_i2c_ee.h 定义的宏)。最后调用库函数 I2C_Init 把这些配置写入寄存器,并调用 I2C_Cmd 函数使能外设。

为方便调用,我们把 I2C的 GPIO 及模式配置都用 I2C_EE_Init 函数封装起来。

I2C总线

I2C总线是一种同步、双向、半双工的两线式串行接口总线。

SCL+SDA 两条总线

它的物理层有如下特点:

(1) 它是一个支持设备的总线。在一个 I2C 通讯总线中,可连接多个 I2C 通讯设备,支持多个通讯主机及多个通讯从机。

(2) 一个 I2C 总线只使用两条总线线路,一条双向串行数据线(SDA) ,一条串行时钟线(SCL)。数据线即用来表示数据,时钟线用于数据收发同步。

(3) 每个连接到总线的设备都有一个独立的地址,主机可以利用这个地址进行不同设备之间的访问。

(4) 总线通过上拉电阻接到电源。当 I2C 设备空闲时,会输出高阻态,而当所有设备都空闲,都输出高阻态时,由上拉电阻把总线拉成高电平。

(5) 多个主机同时使用总线时,为了防止数据冲突,会利用仲裁方式决定由哪个设备占用总线。

(6) 具有三种传输模式:标准模式传输速率为 100kbit/s ,快速模式为 400kbit/s ,高速模式下可达 3.4Mbit/s,但目前大多 I2C 设备尚不支持高速模式。

(7) 连接到相同总线的 IC 数量受到总线的最大电容 400pF 限制 。

协议层:

主机发数据会带SLAVE_ADDRESS,当主机广播的地址与某个设备地址相同时,这个设备就被选中了,没被选中的设备将会忽略之后的数据信号。

从机接收到匹配的地址后,会返回一个应答(ACK)或非应答(NACK)信号,只有接收到应答信号后,主机才能继续发送或接收数据。

写数据

若配置的方向传输位为“写数据”方向,即第一幅图,广播完地址,接收到应答信号后,主机开始正式向从机传输数据(DATA),数据包的大小为 8 位,主机每发送完一个字节数据,都要等待从机的应答信号(ACK),重复,可以向从机传输 N 个数据,这个 N 没有大小限制。当数据传输结束时,主机向从机发送一个停止传输信号(P),表示不再传输数据。

读数据

若配置的方向传输位为“读数据”方向,即第二幅图,广播完地址,接收到应答信号后,从机开始向主机返回数据(DATA),数据包大小也为 8 位,从机每发送完一个数据,都会等待主机的应答信号(ACK),重复这个过程,可以返回 N 个数据,这个 N 也没有大小限制。当主机希望停止接收数据时,就向从机返回一个非应答信号(NACK),则从机自动停止数据传输。

如果我们直接控制 STM32的两个GPIO引脚,分别用作 SCL及 SDA,按照上述信号的时序要求,直接像控制 LED 灯那样控制引脚的输出(若是接收数据时则读取 SDA 电平),就可以实现 I2C 通讯。

由于直接控制 GPIO 引脚电平产生通讯时序时,需要由 CPU 控制每个时刻的引脚状态,所以称之为“软件模拟协议”方式。

相对地,还有“硬件协议”方式,STM32 的 I2C 片上外设专门负责实现 I2C 通讯协议,只要配置好该外设,它就会自动根据协议要求产生通讯信号,收发数据并缓存起来,CPU只要检测该外设的状态和访问数据寄存器,就能完成数据收发。这种由硬件外设处理 I2C协议的方式减轻了 CPU 的工作。

UART 传输器/RS232接口 /RS485接口

RS-232、RS-422、RS-485:是电气协议,接口标准。是对电气特性以及物理特性的规定。

UART:是设备。异步收发传输器。

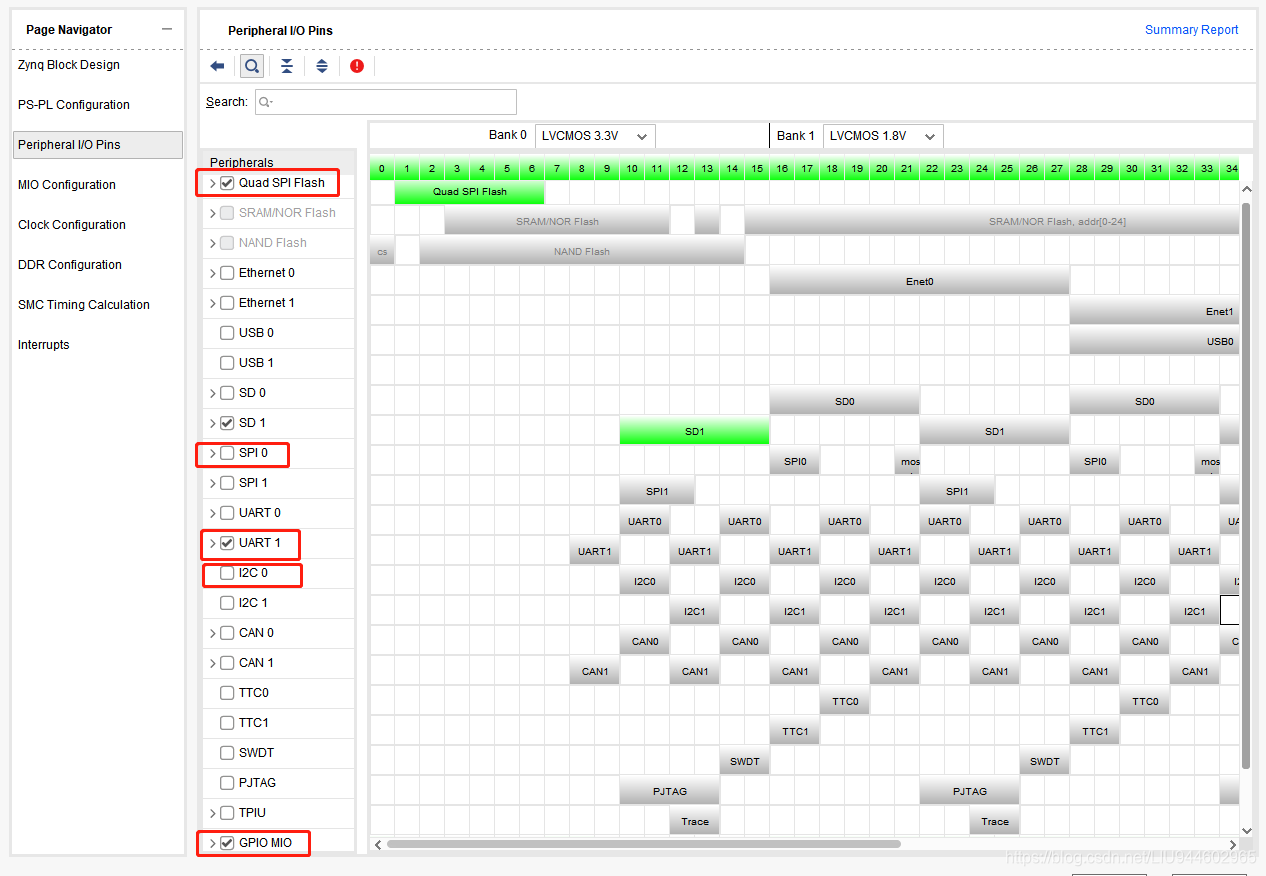

下图中我们可以看出ZYNQ中,硬件使能MIO(可连接LED或者输入等)和使能UART、SPI、I2C是相同的方式。

个人理解:

UART是设备,将并行数据转为串行(一位一位的)数据在线路上发送。

RSXXX是接口标准,它将线路上的电压信号驱动为232或485规定的电平逻辑。

网友理解:

UART可以这样理解:每个SOC芯片,内部都会有UART控制器。但是通常说的UART指的是异步串行通信。规定了数据帧格式,波特率等。

RS232和RS485:是规定了数据通信的电气特性。是物理层的概念,对应的物理器件有RS232或者RS485驱动芯片,将CPU经过UART传送过来的电压信号驱动成RS232或者RS485电平逻辑。

常说的Uart串口指的是TTL电平的串口;RS232串口指的是RS232电平的串口。

Uart串口的RXD、TXD等一般直接与处理器芯片的引脚相连,而RS232串口的RXD、TXD等一般需要经过电平转换(通常由Max232等芯片进行电平转换)才能接到处理器芯片的引脚上,否则这么高的电压很可能会把芯片烧坏。

UART是通用异步收发传输器(Universal Asynchronous Receiver/Transmitter),通常称作UART,是一种异步收发传输器,是设备间进行异步通信的关键模块。

既然是“器”,显然,它就是个设备而已,要完成一个特定的功能的硬件,它本身并不是协议。

它的最基本功能,是串行数据和并行数据之间的转换。

我们知道,计算机中的数据以Byte为基本单位,对一个Byte的存取是并行的,即同时取得/写入8个bit。

而串行通信,需要把这个Byte“打碎”,按照时间顺序来收、发以实现串行。

进一步的,比如确认一个Byte的这8个bit是什么时候开始的,又是什么时候结束的,两个byte之间至少要隔多长时间等等。这一部分,也具有协议的特征。但是与数据传输上的协议,是相对独立的。

若加入一个合适的电平转换器,如SP3232E、SP3485,UART 还能用于RS-232、RS-485 通信,或与计算机的端口连接。

RS-232是美国电子工业协会EIA制定的一种串行物理接口标准。RS是英文“推荐标准”的缩写,232为标识号。

RS-232是对电气特性以及物理特性的规定,只作用于数据的传输通路上,它并不内含对数据的处理方式。

需要说明一下,很多人经常把RS-232、RS-422、RS-485 误称为通讯协议,这是很不应该的,其实它们仅是关于UART通讯的一个机械和电气 接口标准(顶多是网络协议中的物理层面)。

NOR、 NAND、 SPI、 CFI、 JEDEC、NVRAM

Flash,按照内部访问接口不同,分为两种,

一种是就像访问SDRAM一样,按照数据/地址总线直接访问的Nor Flash,

另一种是只有8位(X8)/16位(X16)或者更多(X32/...)位宽的总线,每次访问,都要将长地址分成几部分,一点点的分别传入才能访问的Nand Flash。

而其中的Nor Flash,根据外部接口分,又有并行的CFI接口和串行的SPI接口。

另外,CFI接口是JEDEC定义的,所以又称CFI接口为JEDEC接口。

所以,可以简单理解为:对于Nor Flash来说,CFI接口=JEDEC接口=Parallel接口

NVRAM(Non-Volatile Random Access Memory) :非易失性随机访问存储器,指断电后仍能保持数据的一种RAM。

RAM(Random Access Memory):易失性随机访问存储器,断电之后信息就丢失了的RAM。

NVRAM可以随机访问。因此有些解释中,说Flash是属于NVRAM,是不准确的!!

因为从严格意义上来说,Flash分有两种:nand flash和nor flash。其中的nor属于是可以随机访问的,而nand flash不是真正的随机访问,属于顺序访问(serial access)。

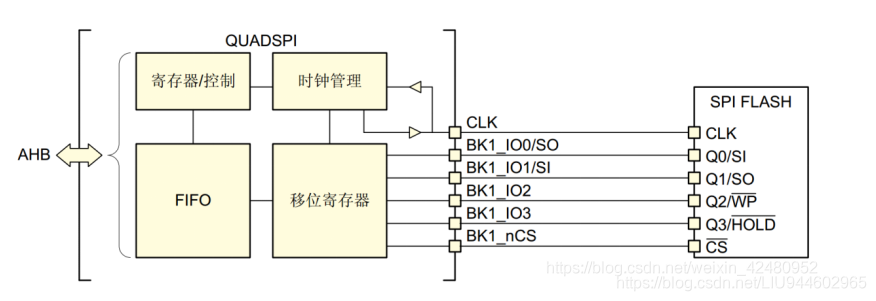

SPI总线和QSPI

SPI总线是同步、双向、全双工的4线式串行接口总线。SPI是由“单个主设备+多个从设备”构成的系统。需要说明的是:在系统中,只要任意时刻只有一个主设备是处于激活状态的,就可以存在多个SPI主设备。常运用于EEPROM、FLASH、实时时钟、AD转换器、数字信号处理器和数字信号解码器之间实现通信。为了实现通信,SPI共有4条信号线,分别是:

(1)主设备出、从设备入(Master Out Slave In,MOSI):由主设备向从设备传输数据的信号线,也称为从设备输入(Slave Input/Slave Data In,SI/SDI)。

(2)主设备入、从设备出(Master In Slave Out,MISO):由从设备向主设备传输数据的信号线,也称为从设备输出(Slave Output/Slave Data Out,SO/SDO)。

(3)串行时钟(Serial Clock,SCLK):传输时钟信号的信号线。

(4)从设备选择(Slave Select,SS):用于选择从设备的信号线,低电平有效。

上图所示芯片有2 个SPI 控制器,SPI 控制器对应SPI 主设备,每个SPI 控制器可以连接多个SPI从设备dev。挂载在同一个SPI 控制器上的从设备共享3 个信号引脚:SCK、MISO、MOSI,但每个从设备的CS 引脚是独立的.

QSPI

QSPI是Queued SPI的简写,是Motorola公司推出的SPI接口的扩展,比SPI应用更加广泛。在SPI协议的基础上,Motorola公司对其功能进行了增强,增加了队列传输机制,推出了队列串行外围接口协议(即QSPI协议)。QSPI 是一种专用的通信接口,连接单、双或四(条数据线) SPI Flash 存储介质。共有SNCS,SCLK,BK0,BK1,BK2,BK3共6根接线,可以实现多种通信模式。

主设备通过控制CS 引脚对从设备进行片选,一般为低电平有效。任何时刻,一个SPI 主设备上只有一个CS 引脚处于有效状态,与该有效CS 引脚连接的从设备此时可以与主设备通信。所以,SPI通信方式可以使用“一主多从”的结构进行通信。每个连接到总线上的器件都有唯一的地址,同一时刻只允许有一个主设备。

SPI、I2C、UART三者关系

I2C:半双工,串行同步通信;

SPI:全双工,串行同步通信;

UART:串行异步通信

总线:物理层,相当于马路。例如I2C总线;

协议:协议层,相当于交通规则。例如I2C协议;

数据:相当于车辆,在指定马路上,按照其交通规则,才能正确传输。

CAN通信

CAN总线ID是包含在报文帧中的。

1、主要用作CAN总线的仲裁使用,ID值越低,报文优先级越高,在两组不同ID报文同时上线时候,仲裁机制使得ID值低的占用总线,ID值高的退出。

2、ID域可以是11位和29位,其值和含义可以由用户自定义,例如0x0CE2505F(可定义为:优先级+功能码+DA+SA)。

数据包如下:包括帧ID、配置位、数据

TxBuf.TxCANID.Bits.ID = ((uint32)0x0C << 24) + ((uint32)0xE200 << 8) + ((uint16)0x50 << 8) + 0x5f;

TxBuf.TxFrameInfo.Bits.RTR = 0; //0数据帧、1远程帧

TxBuf.TxFrameInfo.Bits.FF = 1; //0标准帧、1扩展帧

TxBuf.TxFrameInfo.Bits.DLC = 8; //发送数据字节数

TxBuf.TDA.Bits.Data1 = 0x01 ;

TxBuf.TDA.Bits.Data2 = State ;

TxBuf.TDA.Bits.Data3 = State >> 8;

TxBuf.TDA.Bits.Data4 = State >> 16;

TxBuf.TDB.Bits.Data1 = State >> 24;

TxBuf.TDB.Bits.Data2 = 0;

TxBuf.TDB.Bits.Data3 = 0;

TxBuf.TDB.Bits.Data4 = 0;

CAN2Tx_OSQPostFront(CAN2Send, (void *)&TxBuf);

GPIO

GPIO初始化,如果是多功能IO口先进行功能选择IO功能,

配置为输入或者输出;

初始化值;

读取、或者写1写0

DMA控制器

(Direct Memory Access:直接内存存取)是一种可以大大减轻CPU工作量的数据转移方式。

当CPU初始化传输动作后,CPU把总线控制权交给DMA控制器,传输动作实际是由DMA控制器来实行和完成的。结束DMA传输后,DMA控制器应立即把总线控制权交回给CPU。

请求

CPU对DMA控制器初始化,并向I/O接口发出操作命令,I/O接口提出DMA请求。

响应

DMA控制器,向总线裁决逻辑提出总线请求。当CPU执行完当前总线周期即可释放总线控制权。此时,总线裁决逻辑输出总线应答,表示DMA已经响应,通过DMA控制器通知I/O接口开始DMA传输。

传输

DMA控制器获得总线控制权后,CPU即刻挂起或只执行内部操作,由DMA控制器输出读写命令,直接控制RAM与I/O接口进行DMA传输。

在传送过开始时需提供要传送的数据的起始位置和数据长度。

结束

当完成数据传送后,DMA控制器即释放总线控制权,并向I/O接口发出结束信号。当I/O接口收到结束信号后,一方面停 止I/O设备的工作,另一方面向CPU提出中断请求,使CPU从不介入的状态解脱,并执行一段检查本次DMA传输操作正确性的代码。最后,带着本次操作结果及状态继续执行原来的程序。

由此可见,DMA传输方式无需CPU直接控制传输,也没有中断处理方式那样保留现场和恢复现场的过程,通过硬件为RAM与I/O设备开辟一条直接传送数据的通路,使CPU的效率大为提高。

寄存器

1、什么是寄存器?

给有特定功能的内存单元取一个别名,这个别名就是我们经常

说的寄存器,这个给已经分配好地址的有特定功能的内存单元

取别名的过程就叫寄存器映射。

2、什么是存储器映射?

给存储器分配地址的过程叫存储器映射,再分配一个地址叫重

映射。

FAT32、exFAT、NTFS之间的区别

FAT32:相比以前的技术,可以减少磁盘的浪费,提高磁盘利用率。

exFAT:支持存储单个超过4G的文件。可以视为FAT32的升级。

NTFS:多见于硬盘。可以说NTFS是目前最好的磁盘文件系统。

但NTFS要经常读写存储介质,所以理论上NTFS格式的U盘比较容易损坏。

并且由于U盘带宽有限,NTFS频繁读写占据通道会让磁盘性能降低。

PS:

硬盘默认使用NTFS,也可格式化为exFAT;

U盘、TF卡、SD卡等闪存推荐使用exFAT;

windows XP 不能用 exFAT的U盘,除非打个补丁 WindowsXP-KB955704-x86-CHS(exfat补丁);

mac电脑不能用NTFS U盘;

switch使用 TF卡、SD卡、U盘、移动硬盘或者机械硬盘需要格式化为exFAT。

SD、TF卡速度等级

还有最新速度等级:A1、A2,约为10MB/S。

A1、A2速度也不算最快,但它强调的是频繁读写的稳定性,并且该标准的TF卡可当安卓手机内部空间使用。总之,稳定。

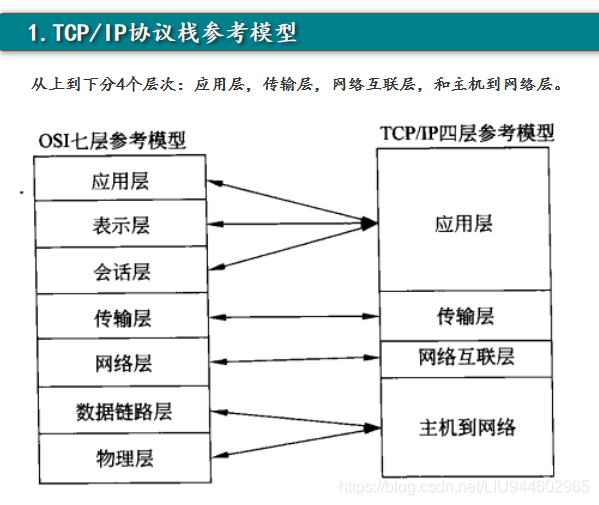

TCP/IP协议栈

UART -- FIFO缓冲区:

FIFO是先进先出缓冲区的意思,即串口接收到的数据可以先进入FIFO,不必马上进入中断服务程序接收,这样可节省CPU时间。对于发送数据也一样,可以把要发送的数据一起写入FIFO,串口控制器可按写入顺序依次发送出去。

只要开启了uart的FIFO功能,uart收到数据就会进入FIFO缓冲区。

如果不用FIFO或者缓冲区长度只有1,那么意味着uart每接收一个字节就要进一次中断,这样频繁进中断会占用CPU资源。

使用FIFO可以在连续接收若干个数据后才产生一次中断,然后一起进行处理,避免频繁进入中断。

而如果接收的数据没有达到FIFO的缓冲长度怎么办?超时中断,即在一定时间内没有接收到数据会进入接收中断,可以利用这个中断把不足FIFO长度的数据最后都读取完。

所以说使用FIFO好处是:

1)避免频繁进中断,提高吞吐率

2)避免数据因没有及时处理而丢失。

不好的地方是:

实时性受影响。比如接收到一个数据后要立刻反应,这种情况FIFO不适合。

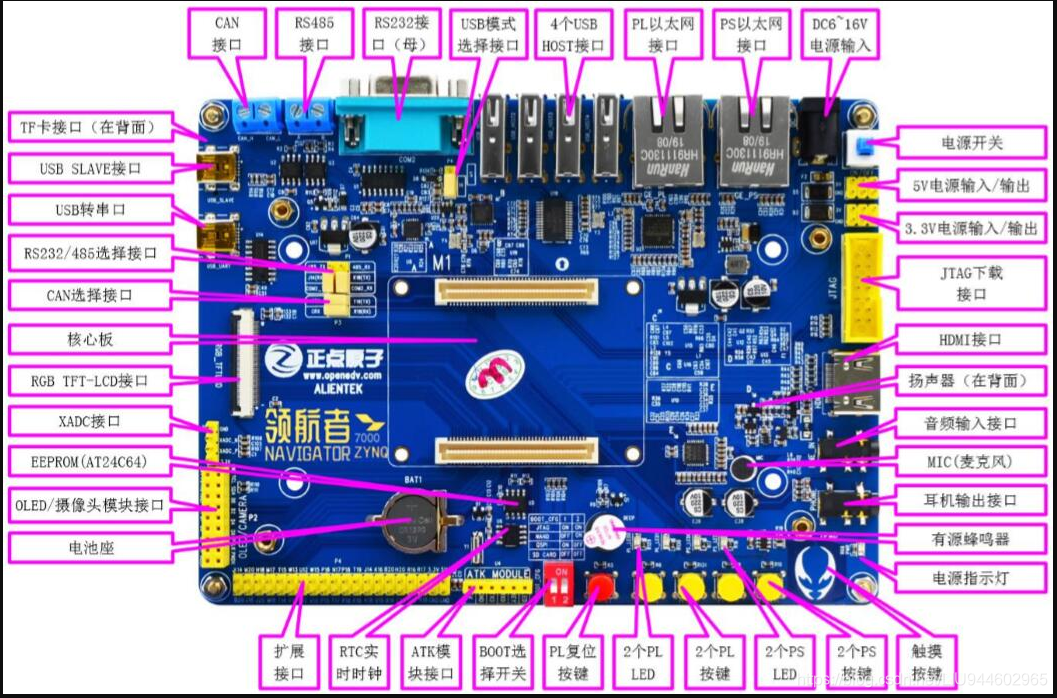

领航者ZYNQ开发板:

接口资源特别丰富,核心板与接口板独立设计:

POSIX

POSIX:可移植操作系统接口(Portable Operating System Interface of UNIX,缩写为 POSIX )

为一个POSIX兼容的操作系统编写的程序,应该可以在任何其它的POSIX操作系统(即使是来自另一个厂商)上编译执行。

简单总结:

完成同一功能,不同内核提供的系统调用(也就是一个函数)是不同的,例如创建进程,linux下是fork函数,windows下是creatprocess函数。好,我现在在linux下写一个程序,用到fork函数,那么这个程序该怎么往windows上移植?我需要把源代码里的fork通通改成creatprocess,然后重新编译...

Posix标准的出现就是为了解决这个问题。linux和windows都要实现基本的posix标准,linux把fork函数封装成posix_fork(随便说的),windows把creatprocess函数也封装成posix_fork,都声明在unistd.h里。这样,程序员编写普通应用时候,只用包含unistd.h,调用posix_fork函数,程序就在源代码级别可移植了。

POSIX标准的文件接口有:close、creat、open、read、sync、write、dup、dup2、flock、fcntl、fsync、lseek、mkstemp等。

CDT

C/C++Development Tools,eclipse插件

浙公网安备 33010602011771号

浙公网安备 33010602011771号