【原创】在仿真中如何使用好parameter?

参考:

http://www.cnblogs.com/oomusou/archive/2008/07/09/verilog_parameter.html

http://www.cnblogs.com/yuphone/archive/2010/05/31/1747871.html

Introduction

使用环境:Debussy + Modelsim

counter是最基本的循序電路應用,為了更加彈性,我們想讓使用者可以自己指定counter的大小,從什麼數字開始數,數到哪個數字停止,而不是寫死在程式裡。利用parameter的小技巧就可以。

Debussy的下载地址:

http://bbs.eetop.cn/thread-270264-1-1.html

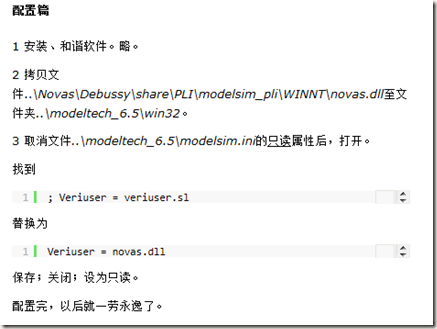

关于Debussy+modelsim联合仿真的配置可以参考:

1.首先建立文件:

--rtl.f

--sim.do

--run.bat

--rtl文件夹包含:parameter_counter.v parameter_counter_tb.v

2. rtl.f文件的内容:

rtl/parameter_counter.v

rtl/parameter_counter_tb.v

3 sim.do文件的内容:

vlib work

vlog -f rtl.f

vsim work.parameter_counter_tb

run 10us

q

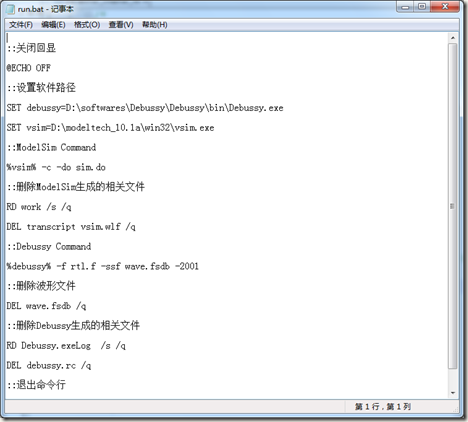

4 run.bat的内容

5 parameter_counter.v

********************************************************

`timescale 1ns/10ps

module parameter_counter (

clk,

rst_n,

cnt,

);

parameter size = 16;

parameter start = 0;

parameter stop = 100;

input clk;

input rst_n;

output reg [size-1 : 0] cnt;

always@(posedge clk or negedge rst_n) begin

if (!rst_n)

cnt <= start;

else if (cnt == stop)

cnt <= start;

else

cnt <= cnt + 1;

end

endmodule

*******************************************************

6 parameter_counter_tb.v

*******************************************************

`timescale 1ns/10ps

//`include "parameter_counter.v"

module parameter_counter_tb;

reg clk;

reg rst_n;

wire [7:0] cnt;

//parameter_counter u0 (.clk(clk), .rst_n(rst_n), .cnt(cnt));

parameter_counter # (.size(8),.start(3),.stop(11))

u0 (.clk(clk), .rst_n(rst_n), .cnt(cnt));

/*

parameter_counter u0 (

.clk(clk),

.rst_n(rst_n),

.cnt(cnt)

);

defparam u0.size = 8;

defparam u0.start = 3;

defparam u0.stop = 9;

*/

parameter clkper = 100;

initial clk = 1'b0;

always #(clkper / 2) clk = ~clk;

initial begin

rst_n = 1'b0;

#1;

rst_n = 1'b1;

end

// dump fsdb file for debussy

initial

begin

$fsdbDumpfile("wave.fsdb");

$fsdbDumpvars;

end

endmodule

********************************************************

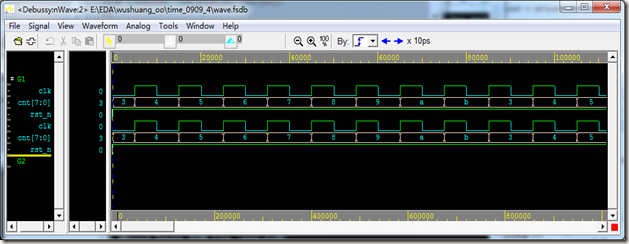

7 双击run.bat,结果如下:

在parameter_counter.v中红色字: parameter宣告,即為Verilog的參數式寫法,之後接的是預設值,如此一來,counter的大小,從什麼數字開始數,數到哪個數字停止都不在是寫死在程式裡。

要讓testbench調用module時,能動態的調整參數,有幾種寫法:

(1)parameter_counter u0 (.clk(clk), .rst_n(rst_n), .cnt(cnt));

是使用预设的参数值;

(2)parameter_counter # (.size(8),.start(3),.stop(9))

u0 (.clk(clk), .rst_n(rst_n), .cnt(cnt));

若要傳入參數,這是第一種寫法,加上#,再用()傳入參數;

(3)

parameter_counter u0 (

.clk(clk),

.rst_n(rst_n),

.cnt(cnt)

);

defparam u0.size = 8;

defparam u0.start = 3;

defparam u0.stop = 9;

這是第二種傳入參數的寫法,靠defparam將參數傳進去。

浙公网安备 33010602011771号

浙公网安备 33010602011771号