【原创】静态时序分析整理一

静态时序分析(Static Timing Analysis---STA)的前提是同步逻辑设计:通过路径计算延迟的总和,并比较相对于预定义时钟的延迟.

一 基础知识

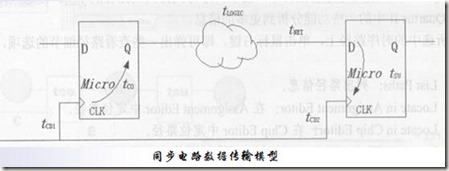

1 同步逻辑延时模型

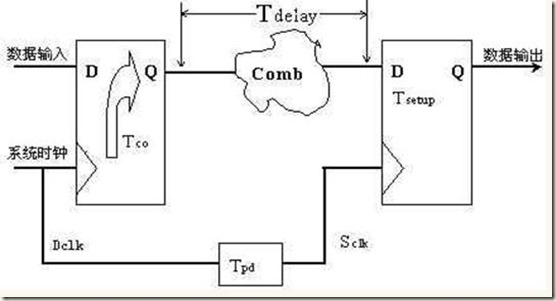

如上图所示,T = tCO+tDELAY+tSU。时钟周期大于T,触发器正常工作;时钟周期小于T,不满足建立时间,触发器可能经历亚稳态。即最高时钟频率f = 1/T。

若考虑到时钟偏斜skew,则如下图:

此时,最小时钟周期为:

tCLK = Microtco + tLOGIC + tNET + MicrotSU- tCLK_SKEW

tCLK_SKEW = tCD2 - tCD1

最高时钟频率:fmax = 1 / tCLK

结合quartus II 举例:

2 时钟抖动

时钟信号边沿变化的不确定时间称之为时钟抖动。考虑到时钟抖动之后,建立时间应该是Tsu + T1,而保持时间应该是Th + T2。

3 时钟偏斜

时序分析的起点是源寄存器(reg1),终点是目标寄存器(reg2)。时钟和其它信号的传输一样会有延时的。上图,时钟信号从时钟源传输到源寄存器的延时定义为Tclk1,传输到目标寄存器的延时定义为Tclk2。

故时钟偏斜为

Tskew = Tclk2 –Tclk1

4 建立时间与保持时间

Setup Time:即建立时间,在时钟上升沿之前数据必须稳定的最短时间。

Hold Time: 即保持时间,在时钟上升沿之后数据必须稳定的最短时间。

Th 限制了数据传输的速度。如果Tco延时太短导致上一级寄存器锁存的数据侵占了下一级寄存器正在锁存数据的保持时间,那么下一级寄存器就无法有效的锁存数据,系统时序也就无法达到要求。也可以这么理解:对于数据接收端来说,任何时钟沿采样的数据,都是发送端前一时钟周期发送的数据。发送端可能每个时钟周期都要发送数据,那么对于接收端来说,任何一个时钟沿后一段时间,数据线上的数据都会被发送端第二次发送的数据改变,所以保持时间容限其实是由于下一个时钟节拍上的数据引起的。

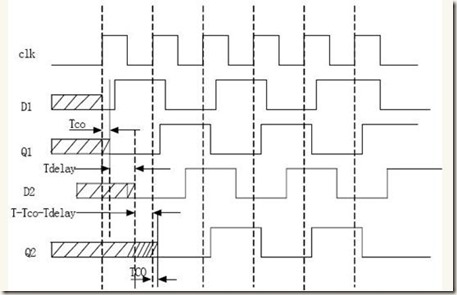

结合时序图说明:

上图中,Tco是触发器的数据输出的延时;Tdelay是组合逻辑的延时;Tsetup是触发器的建立时间;Tpd为时钟的延时。如果第一个触发器D1建立时间最大为T1max,最小为T1min,组合逻辑的延时最大为T2max,最小为T2min。

设第一个触发器的输入为D1,输出为Q1,第二个触发器的输入为D2,输出为Q2; 时钟统一在上升沿进行采样,为了便于分析假设时钟的延时Tpd(也可以暂时认为是Tskew)为零,其实这种情况在FPGA设计中是常常满足的,由于在FPGA 设计中一般是采用统一的系统时钟,也就是利用从全局时钟管脚输入的时钟,这样在内部时钟的延时完全可以忽略不计。时序图如下:

设第二个触发器D2的建立时间为T3与保持时间为T4:

结合上图,可以容易得出:

如果: T-Tco-Tdelay>T3 即:Tdelay< T-Tco-T3

那么就满足了建立时间的要求,其中T为时钟的周期,这种情况下第二个触发器就能在第二个时钟的升沿就能稳定的采到.若Tdelay过大,则可能不满足要求,第二个触发器就在第二个时钟的升沿将采到的是一个不定态,所以:

可以推出

T-Tco-T2max>=T3

这也就是要求的D2的建立时间。

再看保持时间。首先对于数据接收端来说,任何时钟沿采样的数据,都是发送端前一时钟周期发送的数据。发送端可能每个时钟周期都要发送数据,那么对于接收端来说,任何一个时钟沿后一段时间,数据线上的数据都会被发送端第二次发送的数据改变,所以保持时间容限其实是由于下一个时钟节拍上的数据引起的。

有效数据在Tco + Tdelay之后到达触发器,如果保持时间T4 > Tco + Tdelay,则下一个有效数据到达后,保持时间T4仍然没结束,但前一个数据已经被破坏,所以触发器B的保持时间T4需要满足以下条件:

T4 <= Tco + Tdelay。

至此,还可以发现触发器B的建立时间T3的最大值加上保持时间T4的最大值就是一个完整的时钟周期T,即:

Max Tsu + Max Th = T

5 恢复时间与移除时间

6 launch edge 与latch edge

Launch Edge:前级寄存器发送数据对应的时钟沿,是时序分析的起点。

Latch Edge: 后级寄存器捕获数据对应的时钟沿,是时序分析的终点。相对于launch edge通常为一个时钟周期,但不绝对,如多周期约束。

“信号跳变抵达窗口”:对latch寄存器来说,从previous时钟对应的Hold Time开始,到current时钟对应的Setup Time结束。

“信号电平采样窗口”:对latch寄存器来说,从current时钟对应的Setup Time 开始,到current时钟对应的Hold Time结束。

launch寄存器必须保证驱动的信号跳变到达latch寄存器的时刻处于“信号跳变抵达窗口”内,才能保证不破坏latch寄存器的“信号电平采样窗口”。

7 Data arrival time

8 clock arrival time

上图公式减去了setup uncertainty,即考虑最坏的情况仍需满足的data required time (setup)。

10 data required time (hold)

同理,上图公式加上了hold uncertainty,即考虑最坏的情况仍要满足的data required time (hold)。

11 setup slack

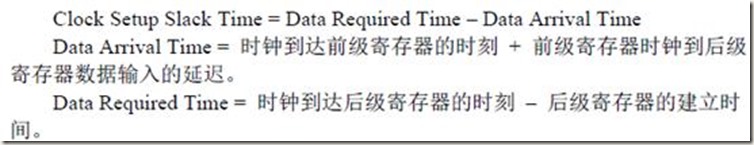

由上图可知, Setup Slack = Data Required Time – Data Arrival Time。

若Setup Slack为正,表示Data Required Time在Data Arrival Time之后,满足Setup Time;反之若Setup Slack为负,则表示Data Arrival Time在Data Required Time之后,无法满足Setup Time。

12 hold slack

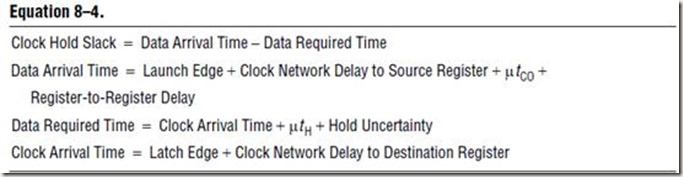

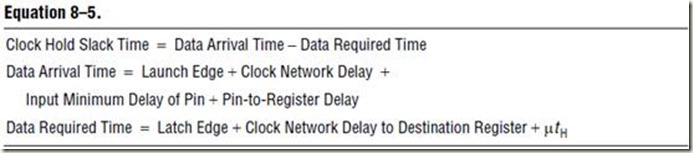

由上图可知, Hold Slack = Data Arrival Time - Data Required Time。

若Hold Slack为正,表示Data Arrival Time在Data Required Time之后,满足Hold Time;反之若Hold Slack为负,则表示Data Required Time在Data Arrival Time之后,无法满足Hold Time。

二 时序分析基本公式

Timequest 根据 Data Arrival Time 和 Data Required Time 计算出时序余量(Slack)。当时序余量为负值时,发生时序违规(Timing Violation)。

时序分析是针对时钟驱动的电路进行的,所以分析的对象一定是“寄存器-寄存器对”。在分析涉及到I/O的时序关系对时,看似缺少一个寄存器分析对象,构不成“寄存器-寄存器对”,其实是穿过FPGA的I/O引脚,在FPGA外部虚拟了一个寄存器作为分析对象。

在Timequest中,时序波形图与时序分析公式是一一对应的,看着波形图去逐项理解时序分析公式中的各个元素比较容易。

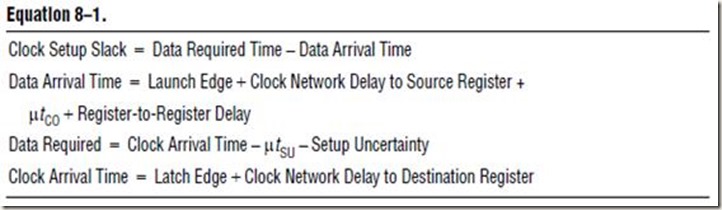

1 建立时间(setup time)检查

遵循的原则是信号从launch edge开始计时,经过一系列的时序路径,到达后级寄存器的数据输入Pin的速度不能太慢,时间不能太长,否则会侵占后级寄存器数据输入Pin相对于latch edge的建立时间。

刚好满足后级寄存器建立时间的数据到达时间是Data Required Time(相对于latch edge计算),实际的数据到达时间是Data Arrival Time(相对于launch edge计算)。显然,在建立时间检查中,Data Arrival Time要小于Data Required Time,否则就会造成建立时间违规。也就是说,Data Required Time是Data Arrival Time的最大值。二者之差就是建立时间的时序余量。

建立时间检查时,Timequest分析每个寄存器至寄存器通路的launch edge和latch edge来确定建立关系。对于目标寄存器的每个latch edge,Timequest使用最靠近源寄存器的前一时钟边沿作为launch edge。

(1)register-to-register路径检查

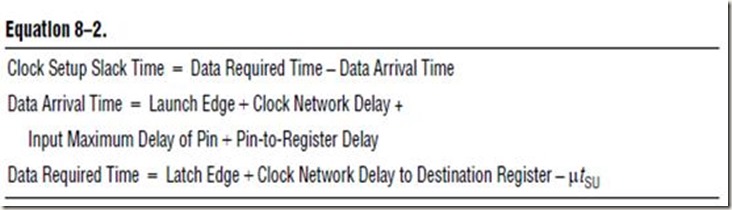

(2)Pin-to-Register路径检查

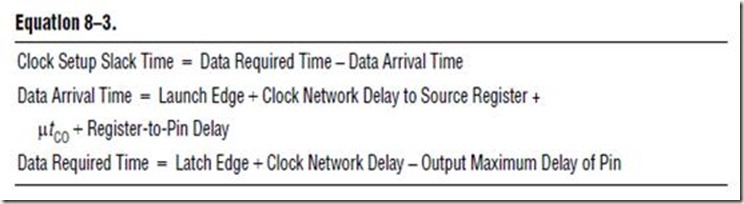

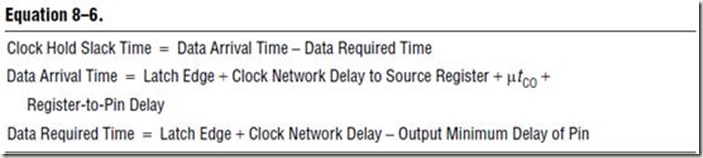

(3)register-to-pin路径检查

上面equation8-1 公式可以做个归纳:

其中,后两个公式的第二项在其他情况下适当修改即可.

2 保持时间(Hold Time)检查

遵循的原则是信号从launch edge开始计时,经过一系列的时序路径,到达后级寄存器的数据输入Pin的速度不能太快,时间不能太短,否则会侵占后级寄存器数据输入Pin相对于上一个latch edge的保持时间。刚好满足后级寄存器保持时间的数据到达时间是Data Required Time(相对于latch edge计算),实际的数据到达时间是Data Arrival Time(相对于launch edge计算)。显然,在保持时间检查中,Data Arrival Time要大于Data Required Time,否则就会造成保持时序违规。也就是说,Data Required Time是Data Arrival Time的最小值。二者之差就是保持时间的时序余量。

建立时间检查和保持时间检查都是同步逻辑设计中对同一个规则的不同解释:当前时钟沿发出的数据要在下一个时钟沿被正确捕获,不能晚,也不能早。晚了会造成下一个时钟沿的建立时间违规,当前时钟沿发送的数据不能被下一个时钟沿捕获;早了会造成上一个时钟沿发送的数据保持时间违规,上一个时钟沿发送的数据不能被当前时钟沿正确捕获。二者在计算公式上的区别在于Slack计算公式中减数与被减数关系。

Timequest分析器对每一种建立关系进行两种保持检查。第一种保持检查确定当前launch edge的数据没有被前一latch edge捕获到。第二种保持检查确定下一launch edge的数据没有被当前latch edge捕获到。

(1) 寄存器-寄存器(Register-to-Register)路径检查

(2) 输入引脚-寄存器(Pin-to-Register)路径检查

(3) 寄存器-输出引脚(Register-to-Pin)路径检查

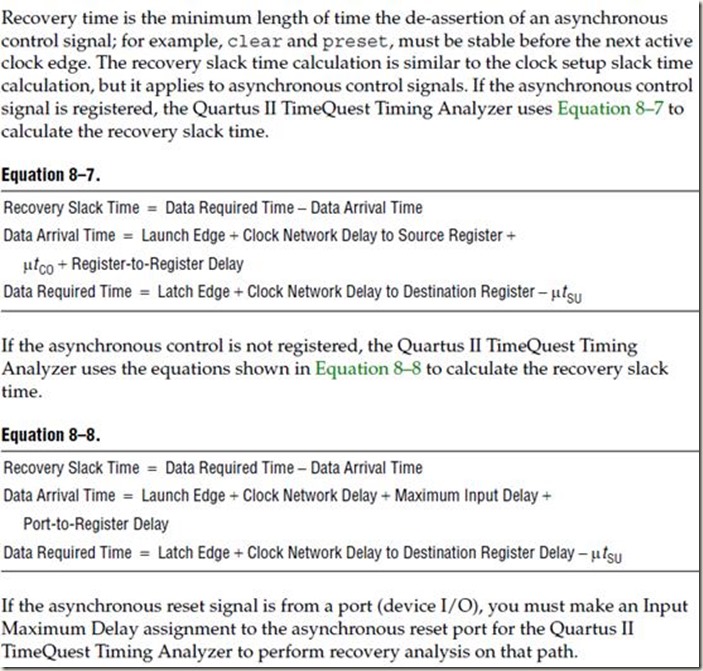

3 恢复时间(recovery time)检查

4 移除时间(removal time)检查

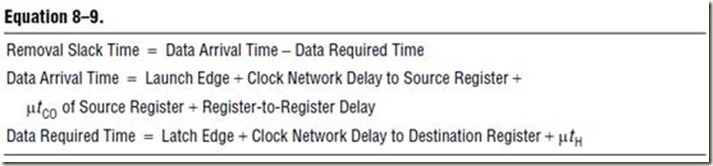

Removal time is the minimum length of time the de-assertion of an asynchronous control signal must be stable after the active clock edge. The Quartus II TimeQuest Timing Analyzer removal time slack calculation is similar to the clock hold slack calculation, but it applies asynchronous control signals. If the asynchronous control is registered, the Quartus II TimeQuest Timing Analyzer uses the equations shown in Equation 8–9 to calculate the removal slack time.

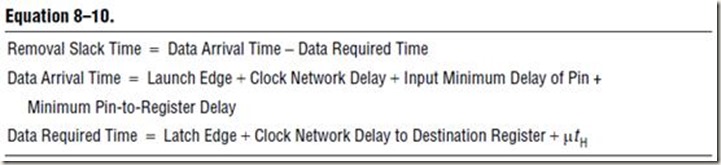

If the asynchronous control is not registered, the Quartus II TimeQuest Timing Analyzer uses the equations shown in Equation 8–10 to calculate the removal slack time.

If the asynchronous reset signal is from a device pin, you must specify the Input Minimum Delay constraint to the asynchronous reset pin for the Quartus II TimeQuest Timing Analyzer to perform a removal analysis on this path.

5 多周期路径(Multicycle Paths)检查

在上述的建立、保持时间检查中,都假设数据从launch edge开始发送,在latch edge被捕获;launch edge和latch edge是相邻最近的一对时钟沿。

在多周期路径检查中,仍然采用launch edge和latch edge的概念;但是launch edge和latch edge不再是相邻的一对时钟沿,而是间隔一定时钟周期的一对时钟沿,间隔的时钟周期个数由用户指定。

在同步逻辑设计中,通常都是按照单周期关系考虑数据路径的。但是往往存在这样的情况:一些数据不需要在下一个时钟周期就稳定下来,可能在数据发送后几个时钟周期之后才起作用;一些数据经过的路径太复杂,延时太大,不可能在下一个时钟周期稳定下来,必须要在数据发送后数个时钟周期之后才能被采用。针对这两种情况,设计者的设计意图都是:数据的有效期在以launch edge为起始到数个时钟周期之后的latch edge。这一设计意图不能够被时序分析工具猜度出来,必须由设计者在时序约束中指定;否则,时序约束工具会按照单周期路径检查的方式执行,往往会误报出时序违规。

不设置多周期路径约束的后果有两种:一是按照单周期路径检查的结果,虚报时序违规;二是导致布局布线工具按照单周期路径的方式执行,虽然满足了时序规范,但是过分优化了本应该多个周期完成的操作,造成过约束。过约束会侵占本应该让位于其他逻辑的布局布线资源,有可能造成其他关键路径的时序违规或时序余量变小。

在多周期路径的建立时间(Setup Time)检查中,Timequest会按照用户指定的周期数延长Data Required Time,放松对相应数据路径的时序约束,从而得到正确的时序余量计算结果;在保持时间(Hold Time)检查中,Timequest也会相应地延长Data Required Time,不再按照单周期路径的分析方式执行(不再采用launch edge最近的时钟沿,而是采用latch edge最近的时钟沿),这就需要用户指定保持时间对应的多周期个数。

Timequest缺省的Hold Time检查公式是需要用户修改的——针对Setup Time多周期路径的设置也会影响到Hold Time的检查。究其原因,多周期路径是为了解决信号传播太慢的问题,慢到一个周期都不够,所以要把Setup Time的检查往后推几个周期——扩大Setup Time检查的时间窗口。而Hold Time检查信号是否传播得太快,如果把检查时刻往后推,就缩小了Hold Time检查的时间窗口。

“信号跳变抵达窗口”:对latch寄存器来说,从previous时钟对应的Hold Time开始,到current时钟对应的Setup Time结束。

“信号电平采样窗口”:对latch寄存器来说,从current时钟对应的Setup Time 开始,到current时钟对应的Hold Time结束。

launch寄存器必须保证驱动的信号跳变到达latch寄存器的时刻恰好处于“信号跳变抵达窗口”内,才能保证不破坏latch寄存器的“信号电平采样窗口”。

时序检查的目的就是确认信号跳变发生在“信号跳变抵达窗口”内,而不会发生在“信号电平采样窗口”内。

多周期路径的设置是通过延后Setup Time检查的时刻,扩大了“信号跳变抵达窗口”,放松了时序约束。通过窗口的概念,也很容易理解延后Hold Time,就会缩小“信号跳变抵达窗口”。

浙公网安备 33010602011771号

浙公网安备 33010602011771号