6.15-多周期MIPS CPU数据通路(1)

单周期MIPS关键路径LW指令

- 时间延迟问题

由于系统采用单周期实现所以整个系统的时钟周期取决于最慢那一条指令的时间延迟,以LW指令为例,涉及到指令存储器以及数据存储器的访问,所以是最慢的那条指令

- LW的最长路径部分

- 首先经过PC将数据输出,当时钟上跳沿来临的时候,PC要将值输出必须要有一个触发器延迟也就是我们的CLK_TO_Q,经过延迟后我们PC的值会输出到指令存储器的地址端然后经过指令的存储器延迟Tmem,可以得到一个指令字

- 解析指令字中的Rs,Rt,Rd访问寄存器堆,寄存器读也需要一个延迟,通常这里是里面多路选择器的时间延迟(就是一个时钟周期),将对应寄存器的值输出以后

- 在经过运算器运算地址,所以将立即数进行扩展以后和Rs值相加得到一个地址,所以这里还需要经过一个运算器ALU延迟之后算得地址

- 有了地址之后再经过一个地址延迟之后才能够将我们需要的操作数取出送回到寄存器堆,要将对应的数据要在写输入端,保持一个稳定的时间这部分时间称为寄存器值的建立时间Tsetup所以我们一个单周期MIPS CPU关键延迟就可以用这及部分时间累加起来

- 所以单周期是所有时间延迟的累加,性能取决于最慢的那个周期时间过长

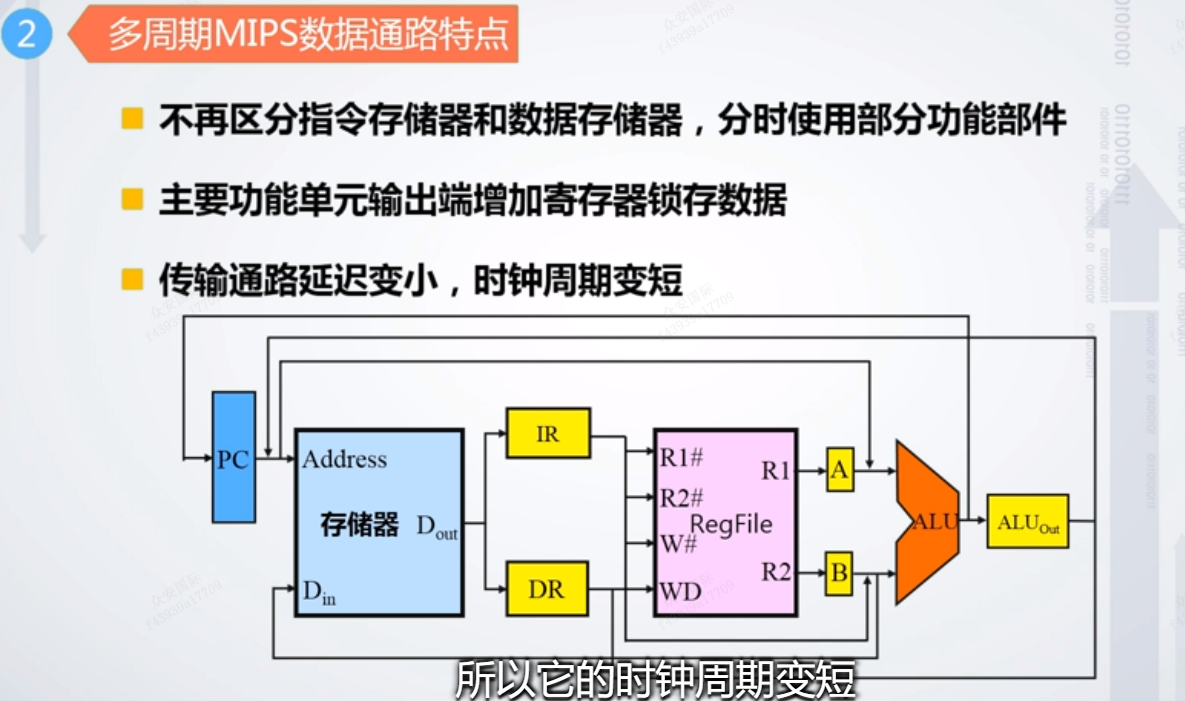

多周期MIPS数据通路特点

多周期MIPS指令是将一个指令执行的很长过程细分成若干段,取指,译码,执行甚至可以同时执行不再区分指令存储器和数据存储器需要分时的对同一个存储器进行分时复用,取指的时候取出数据在时间上错开,错开时间是一个比较小的时间单位所以时钟周期变小,传输通路变短,整个完整的数据通路演变成了放存通路以及ALU通路,在每一个通路之间都增设了若干的寄存器用来锁存数据,在主要单元的输出端,比如存储器的输出端增加了一个IR,DR,这是在原有单周期CPU中是不存在的在寄存器文件,寄存器堆输出后,增加了一个A寄存器和一个B寄存器,直接锁存两个寄存器的值运算器运算完的结果输出到ALUout的一个寄存器通过若干个黄色的寄存器,就把整个的关键路径细分成了若干段。这段是存储通路,这段是取操作数通路,这段是运算通路,而每一个通路由于内部功能部件功能非常单一所以时钟周期会变短

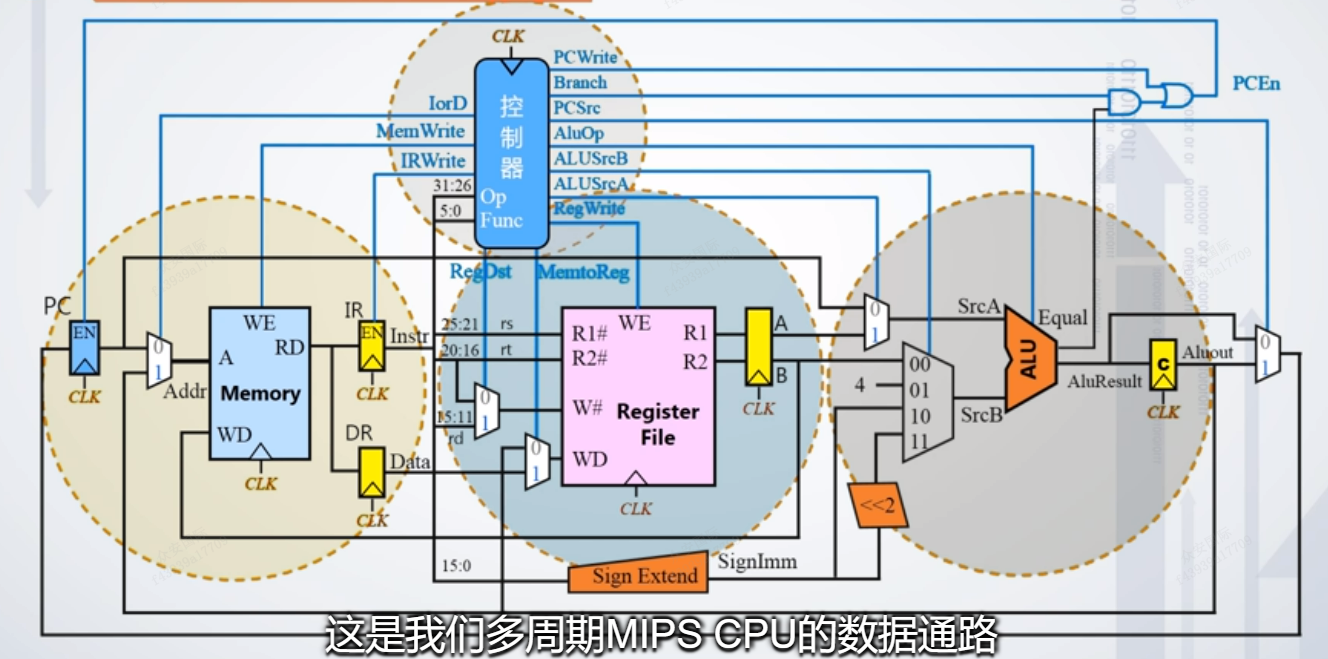

多周期MIPS CPU数据通路框架

- 可以看到刚才给出的IR,DR, A,B,A和B合并化成了一个寄存器因为是同步工作,AB寄存器没有写使能所以时钟到来一定会写入新的数据,DR也没有写使能,IR增加了一个写使能,IR是可以控制的,DR是不能控制的时钟到来一定会改变,运算器的结果增加了一个C寄存器用来锁存运算器的运算结果,增加了A,B,C三个寄存器还有一个DR寄存器这四个寄存器没有写使能,时钟没到来一次他们的值就会更改一次。控制器产生所有功能部件所需要的控制信号,控制器不在和单周期CPU不再一样,它有了一个时钟输入原因这是一个多周期的控制器所以是有时序的,不是一个纯组合逻辑

- 黄色圆圈部分是访存通路既可以访问指令也可以访问操作数

- 蓝色圆圈部分是取寄存器操作数的通路

- 最后一部分是ALU的运算通路

- 核心部分是由控制器来进行控制控制所有部件进行动作

在不同阶段数据通路建立过程

- 取指令

所有的取指令都是以PC为地址访问内存送指令字到IR同时PC累加。所以要先完成PC累加的动作,由于PC和我们ALU之间存在着直接的数据通路所以可以直接将PC的值拿过来这个多路选择器的输入端就是4,直接将4选择给出对应的控制信号和PC做加法运算结果送回PC端。所以完成PC + 4要给出三个控制信号,才能完成对应的数据通路,当时钟到来PC + 4值就会送入 PC端。在进行PC+的过程中

- 在进行PC+的过程中在进行指令存储器的访问,在这里指令存储器和数据存储器合并为一个存储器。在这里PC给出一个地址送到指令存储器取出指令送到IR,这个多路选择器应该选择0路所以给出0信号,指令字会送入到IR的输入端,要想将指令送入IR必须给出IRWrite的控制信号当时钟到来时我们可以实现指令字写入IR的动作,时钟到来时PC的值会被更新为PC + 4.IR的值锁存当前取出的指令这就是取指令的通路,这个通路需要一个时钟周期称为T1

- 当IR值锁存,PC+4完成后,下一个时钟周期要完成第一个译码,因为指令已经取出所以指令字会将Funct和OP送到控制器进行译码生成译码控制信。第二个要进行取操作数根据指令字产生控制信号后R1,R2都有正确的值会读对应寄存器进行读出响应的立即数也会进行立即数的扩展这是我们的取操作数部分同时这个节拍还可以将PC + 4的值传输进来将立即数左移两位和它相加进行计算条件分支的地址所以在第二拍除了由寄存器组取操作数以外还可以进行分支地址的同时计算这两部分是并行的,当时钟周期到来寄存器的R1,R2的值已经就绪所以它的值可以传送到A和B两个寄存器时钟到来时A,B值会改变另外运算的分支地址由ALU会传送到C寄存器,后面节拍会用到。PC+4和IR的写入信号不会改变所以IR一直锁存当前指令。PC + 4值由于没有PCWrite的信号所以PC+4值也会一直锁定这就是取指令的第二个节拍:译码+取操作数+计算分支指令地址。所以整个MIPS取指需要两个时钟周期,取指完成以后会进入执行指令阶段