6.14-单周期MIPS CPU(2)

数据通路综合

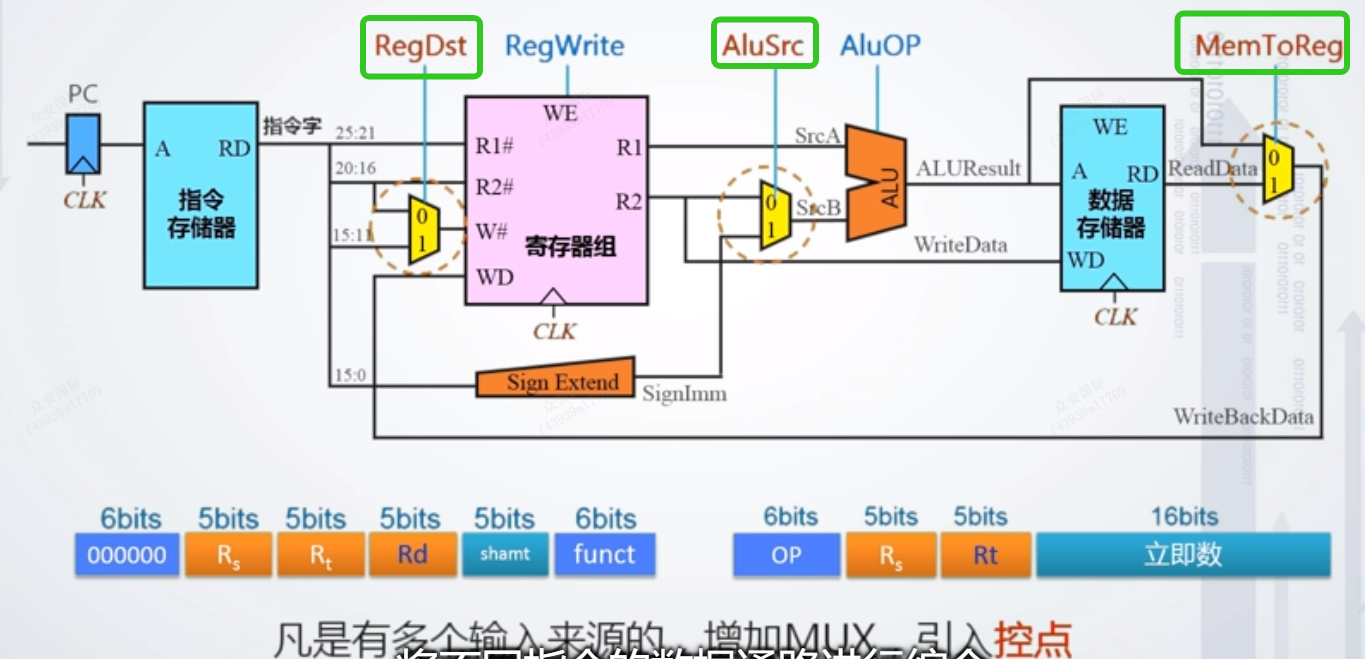

前面介绍R型指令格式有三个寄存器操作数和I型指令格式有两个寄存器操作数和一个立即数。R型指令的写入寄存器编号是Rd,而对于I型指令写入寄存器的编号可能是Rt。所以在将R型指令和I型指令进行综合的时候要在同一个数据通路上能够运行两种不同的指令称为数据通路的综合。进行综合的时候对于具有多个输入源的引脚必须加上多路选择器进行信号的选择,所以要加一个多路选择器。

多路选择器会有个选择信号RegDst这么一个选择信号,就是可以控制到底选择Rd还是选择Rt作为写入寄存器编号,同样对于运算器来说第二个操作数有可能来自于寄存器组的第二个寄存器输出也可能来自立即数的符号扩展,所以也要增加一个多路选择器,也增加了一个控制信号AluSrc.写回的时候对应的数据有可能来自于数据存储器也可能来自于ALU的运算结果 ,所以也要增加一个多路选择器对应的信号是MemToReg用来控制到底是从内存写回还是从ALU的运算结果写回。所以按照这种方法将不同指令的数据通路进行综合。凡是有多个输入来源的要增加多路选择器引入空点。

RegWrite还有数据存储器也有一个WE信号这些信号是功能部件的对应的控制信号,所以多路选择器的选择信号以及各执行功能部件的控制信号加在一起够成整个计算机的控点

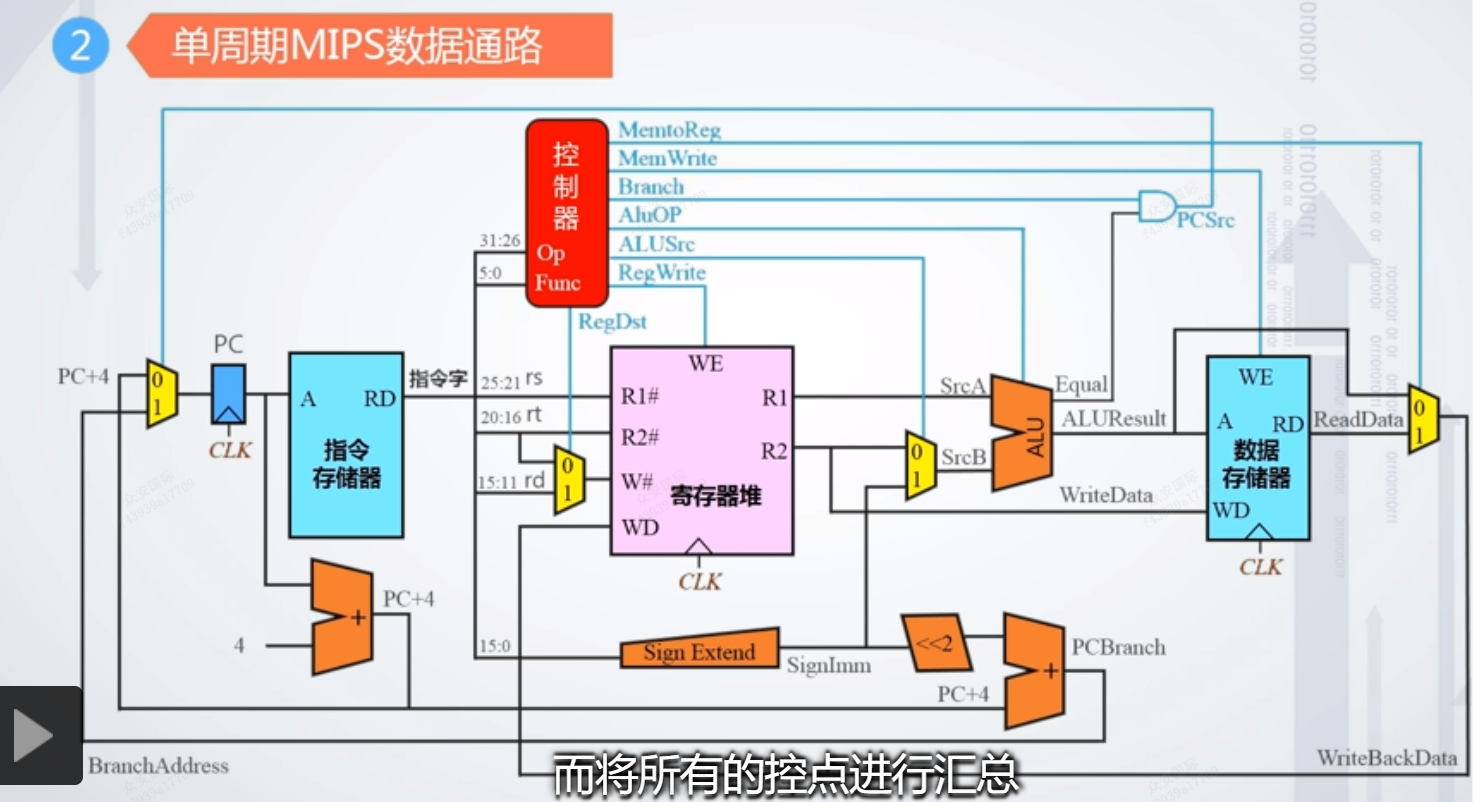

单周期MIPS数据通路

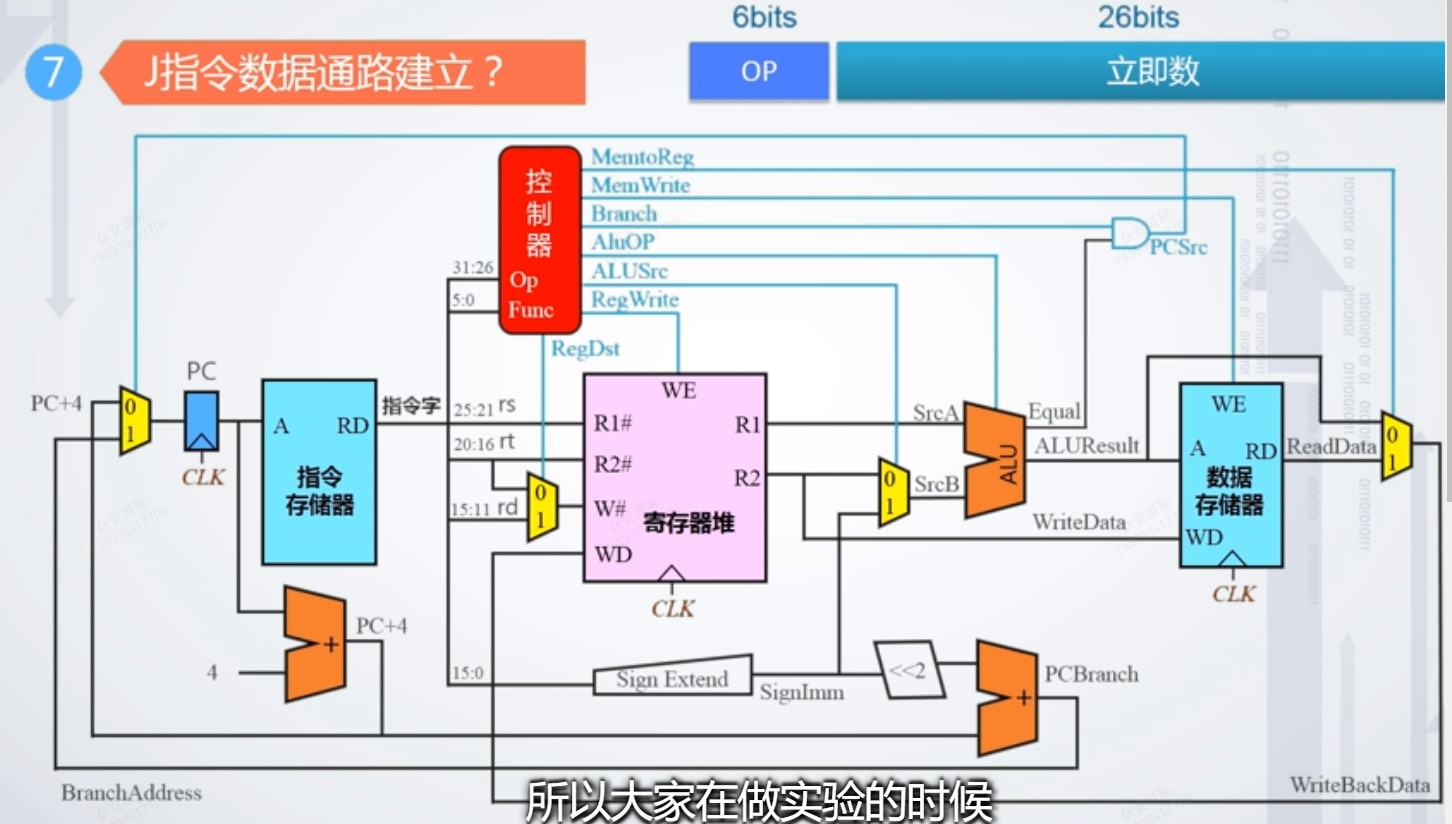

将所有指令R,I,J型数据指令进行综合就可以得到单周期MIPS指令总的数据通路

将所有指令的空点进行汇总就可以得到控制器的输出,而控制器的输入来自于指令,存储器指令字的OP端就是操作码端以及Funct端,根据OP可以知道是R型指令还是I型指令。根据Funct就可以知道R型指令的具体功能。所以控制器在这里输入是我们指令中的部分字段,输出就是我们所有控点,由于是单周期CPU。所以控制器是一个纯组合逻辑所有的信号只跟当前指令有关系,没有时序的概念。在整个综合的数据通路中我们会发现需要重复设置的部件比如说棕色的部分运算器,计算跳转地址的这个加法器,左移部分还有符号扩展部分以及计算PC加4的加法器部分这些都是运算部件需要进行并发所以需要设置不同的功能部件。还有指令存储器和数据存储器在这里也分成了两部分,黄色部分就是多路选择器,需要多个输入源的时候就需要加多路选择器

R型指令数据通路建立过程

- 当PC给出一个地址访问指令存储器得到指令字以后直接将Rs的值解析出来,将Rt的指令解析出来,Rd的值解析出来,Rd由于是目标寄存器,所以必须写入,这里是多路选择器必须给出一个对应的信号所以RegDst给出一个具体的红色的值表示给出了一个高电平选择选择下面的输入来源也就是Rd直接进行写入。这是第一步将Rd送到写入寄存器编号中

- 完成第一步之后访问寄存器,经过一个寄存器多路选择延时,因为内部读出有一个多路选择器经过一个读的延时之后得到Rs和Rt的值,将Rs,Rt的值送入到ALU,注意在传送的过程中对于ALU的B端也有一个多路选择器所以这里必须给出一个AluSrc的对应信号才能将正确的Rt值传送到ALU,ALU选择一个合适的运算操作码,运算以后得到一个结果直接由相应的通路传输进行写回,写回的时候一样也有个控制信号要给出MemToReg这样一个控制信号才可以建立这样一个数据通路

- 当时钟到来时由于数据已经运算完毕R型指令已经运算的结果已经送到WD端写入寄存器的编号就绪,此时只需要给出一个写入的信号RegWrite在时钟配合下就可以将对应的数据写入到寄存器中。

- 在R型指令进行执行的同时RC + 4的逻辑也在同时工作,PC + 4逻辑传入到多路选择器由于当前是R型指令所以直接选择这一条通路,将PC + 4送入到PC当时钟到来时将PC + 4的值写入到PC寄存器中

- 对于R型指令的特殊指令移位指令,Rs是没有用的偏移量部分是有用的在这样架构中移位指令的实现,在这个架构中并没有将对应的移位的偏移量传送到ALU所以要实现移位指令只需要将指令字中对应的移位偏移量传送到ALU。可以把对应的偏移量经过一个多路选择器送到SrcB端也可以改造一下ALU增加一个移位偏移量的输入端这种方式更好,避免了增加一个控点直接由移位指令的时候选择对应真正的实际操作数为另外新增的引脚

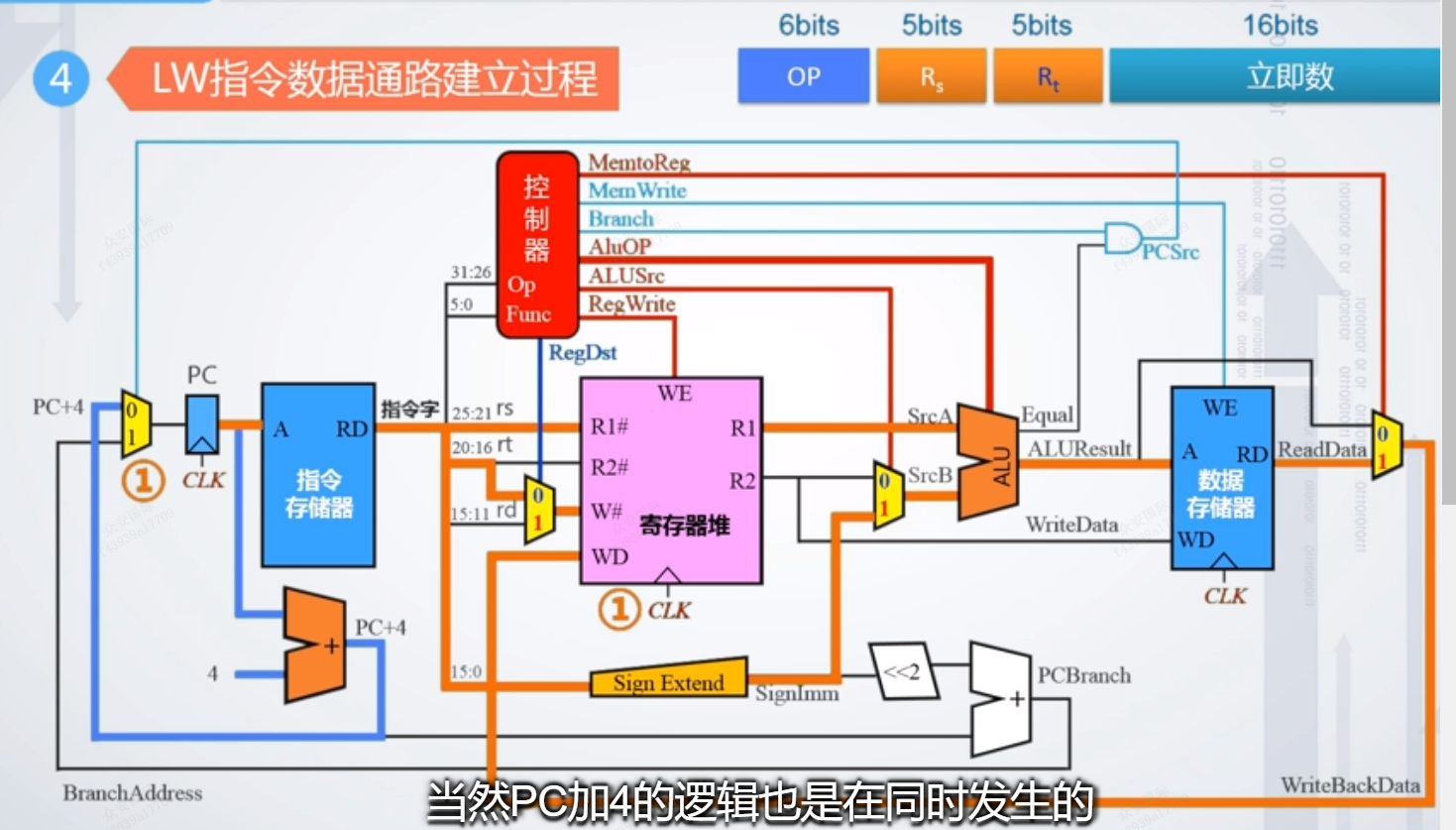

I型指令中以LW型指令为例数据通路建立过程

- 当PC给出一个地址取出一条指令的时候,解析出Rs,Rt字段,Rt在LW指令里面是作为目标寄存器存在,所以Rt在这里应该送到写入寄存器编号那么对应控制器应该给出一个RegDst为0,选择这一路将Rt的值送入到写入寄存器编号所以给出一个RegDst为0,选择Rt的值到W#这个输入端

- 经过寄存器的读出延迟以后Rs值会读出另外立即数的值会经过符号扩展得到32位的立即数经过多路选择器送入到ALU端所以对应的多路选择器也要给出对应的控制信号,能够选择对应的立即数到ALU端ALU给出响应的运算操作这里应该给出一个加法操作来计算内存地址,所以运算结果是一个内存地址再由地址去访问我们的数据存储器取操作数,经过一个存储时延以后得到响应的操作数

- 要想将存储器的数据输出到寄存器的写入段一样要对多路选择器进行响应的控制。最后将从内存读出的数据写入到寄存器中所以要给出一个写使能信号,当时钟到来时,我们的数据就会写入到寄存器中

- PC+4的指令也是在同时发生

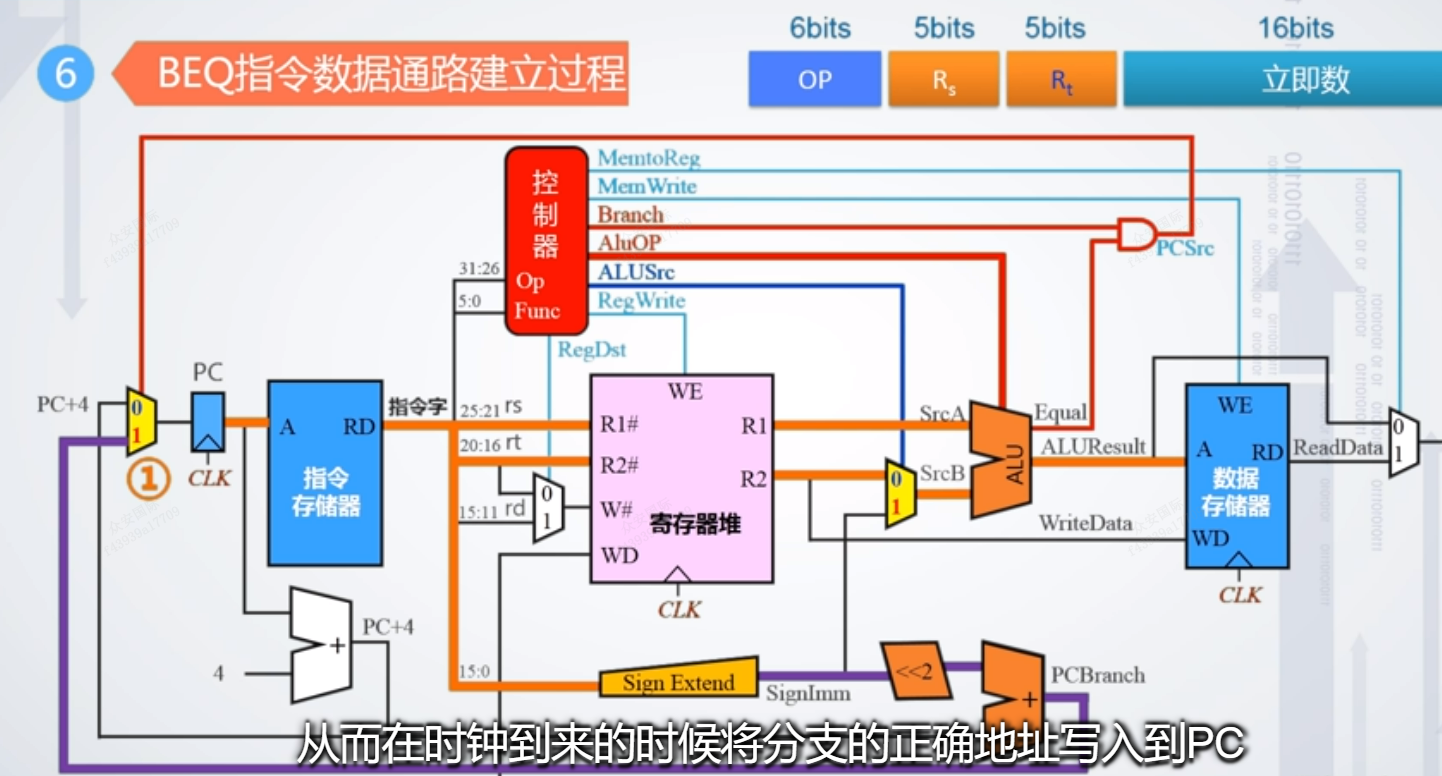

BEQ指令数据通路

- 判断Rs值和Rt值是否相等,如果相等进行条件跳转。直接将两个寄存器Rs和Rt的值经过寄存器取出给出对应多路选择器的控制信号在ALU端做运算。我们在实验中涉及的ALU有个equal来判断两个值是否相等,所以不用关心做什么运算只要是固定运算这个equal都会发生作用当A和B相等即Rs和Rt相等的时候就会打开这个与门。而这个Branch信号就是BEQ的译码信号

- 两个信号做与之后就可以选择对应这个多路选择器的第二个输入进行PC的修改

- 第二个输入正好是具体指令之中对应的立即数进行左移两位在累加上PC + 4的值也就是分支地址正好转移到这上面来所以当时BEQ指令并且运算结果相等的时候会产生这样一个选择信号,正好是我们的分支地址从而当时钟到来的时候将分支正确的写入到PC端,从而达到改变程序顺序的目的

J型指令数据通路

- J型指令结构非常简单只有一个OP6位 + 26位立即数,26位立即数可以通过PC + 4的高4位加上这26位再补2个0构成32位的跳转地址所以在上面的通路上没有报案J型指令的通路

- 如果要安排一个J型指令的通路首先控制器要有有一个Jump或者说J型指令的译码信号Jump,这个信号控制具体的PC + 4+ 26位偏移量的值送到PC端所以我们PC的来源这里应该又多一个多的选项就是跳转地址,这个跳转地址的控制端由我们的Jump来控制所以要引入Jump的数据通路第一个要生成Jump的的译码信号增加一个多路选择器同时指令字出来以后要将26位立即数转换成最终要跳转的地址送到这个多路选择器

单周期MIPS控制器设计

- 输入端就是指令的OP段6位,Funct字段6位共12个输入

- 输出是各多路选择器的选择控制信号以及功能部件的控制信号比如寄存器的写使能和内存寄存器的写信号,将控制器看成一个纯组合逻辑由于信号与指令之间的对应关系非常简单。单周期没有时序逻辑就是一个纯组合逻辑输入时12位输出是多路选择器的选择信号