6.13-单周期MIPS CPU(1)

MIPS CPU控制器设计

- 定长指令周期:单周期实现

所有指令在一个周期内完成, CPTI = 1

性能取决于最慢的指令,时钟周期过长

- 变长指令周期:多周期实现

缩短时钟周期,复用器件或数据通路

可支持流水操作,提升性能

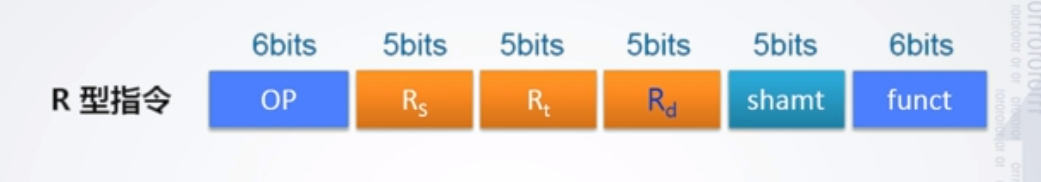

MIPS指令格式

相对于X86,MIPS指令是精简指令,一共包括R型指令和I型指令,J型指令三种指令

- R型指令:高6位OP的值为全0,表示R型指令,确定后后面三个5位表示寄存器的编号分别为Rs,Rt,(两个源寄存器)Rd(目的寄存器用来做写入),由于是5位所以提供32个通用寄存器地址,后面5位shamt用来做移位偏移量,最多31位,0-31一共32个选项,最后6位funt,用来描述R型指令的具体功能,十进制32位加法,十进制34为减法,相当于扩展操作码

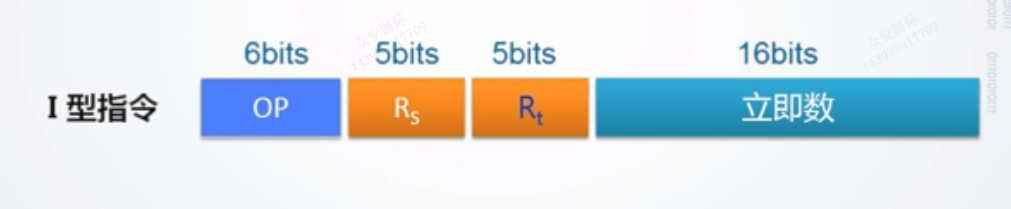

- I型指令:只有两个寄存器编号Rs和Rt,其中Rt有可能作为目标寄存器,后面16位长度表示16位立即数用来计算对应的分支地址或者对应的立即数

- J型指令:OP6位操作码和26位立即数组成

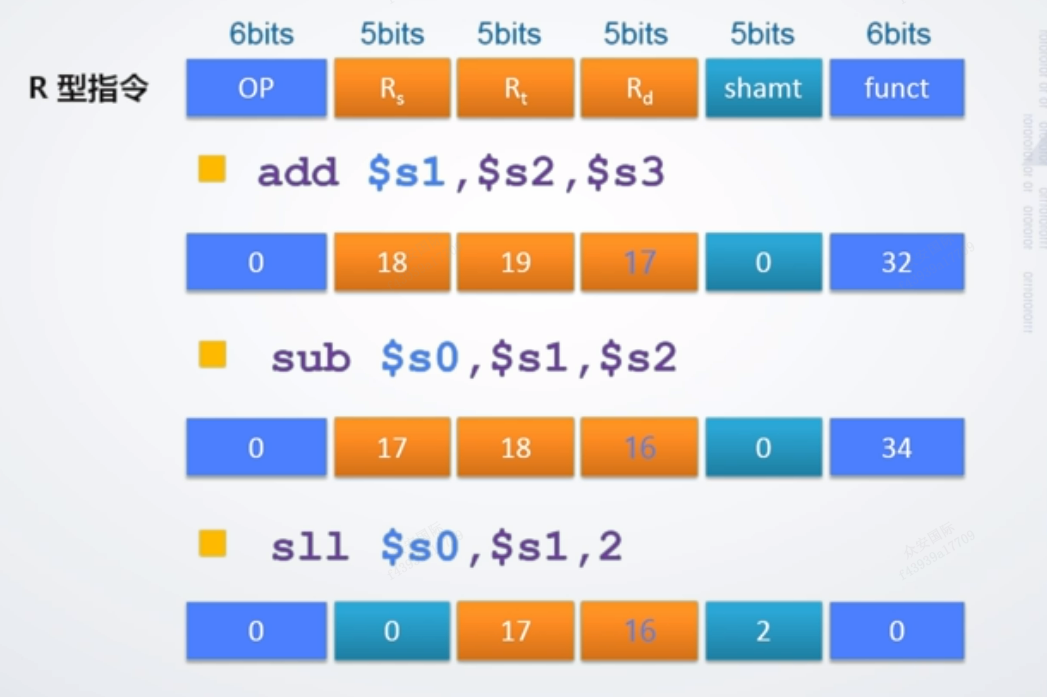

R型指令格式

以加法为例:

ADD $s1, $s2, $s3

S1对应目标寄存器Rd是17号寄存器s2,s3分别对应18号19号寄存器,获得三个寄存器通过funct字段进行加法。减法和左移是一样的

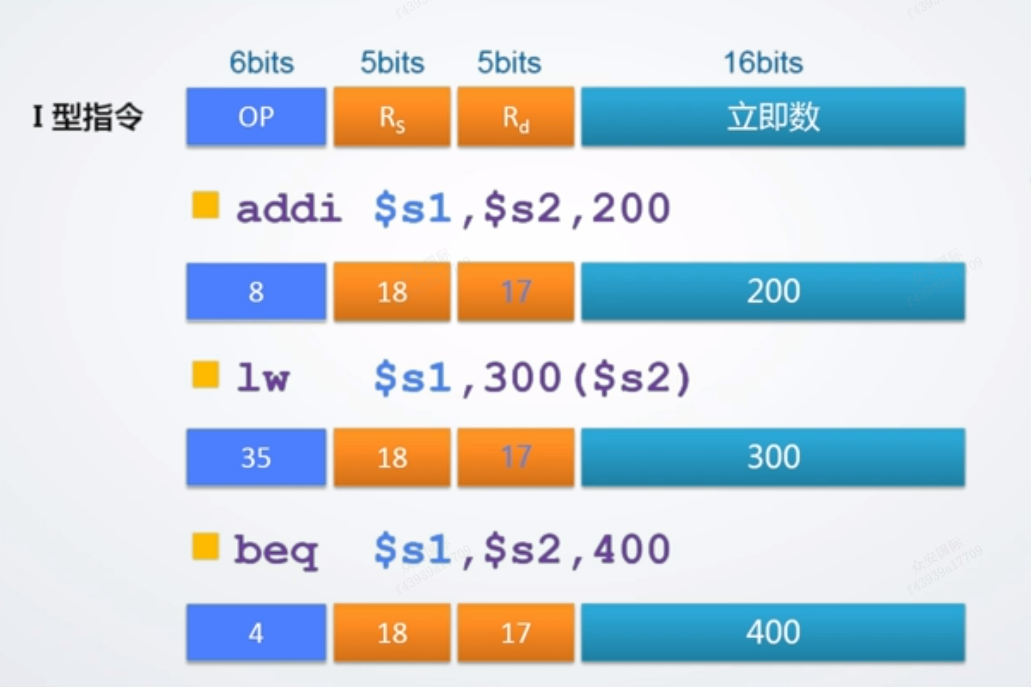

I型指令格式

Add指令Rd变成了目标寄存器,所以目标寄存器可能是Rt也可能是Rd,计算完成后跳转到PC + 8 + 200的指令地址

单周期取指令数据通路

Mem[PC++] ->IR

以PC为例访问内存,将取出来的数据存入寄存器IR,同时PC做累加操作,PC++累加的是指令的字节长度.需要在一个周期内完成整个指令,取指,取操作数

所以直接以PC为地址直接访问指令存储器不需要地址缓冲器,为什么是指令存储器,因为指令进行执行的时候首先要取指令在执行阶段还需要取操作数,取指令和去操作数都要访问主存,这个时候就发生了器件的争用,为了解决这个问题我们需要将系统中多次共用的功能部件分开,所以将存储程序,存储指令和数据存储器分开,所以使用指令存储器,数据存储器。现代计算机系统中CPU内部存在着单独的指令cache和数据cache也相当于把指令和数据分开。当多次用到运算器比如做PC累加的操作以及实际运算的运算器运算器也需要争用,取指的时候也要设置一个单独的加法器

- 由于是单周期不能设置AR, IR,DR寄存器

- 程序和数据分开存储----哈佛结构

指令存储器,数据存储器

指令cache,数据cache

- 运算和PC累加分离

所以完成上面的指令需要如下操作,取指令数据通路

- 以PC为地址直接访问指令存储器,经过一个存储周期后就会活得一个指令字

- 同时指令地址经过一个加法器+4之后送回到PC当时钟到来的时候PC就变成了PC+4

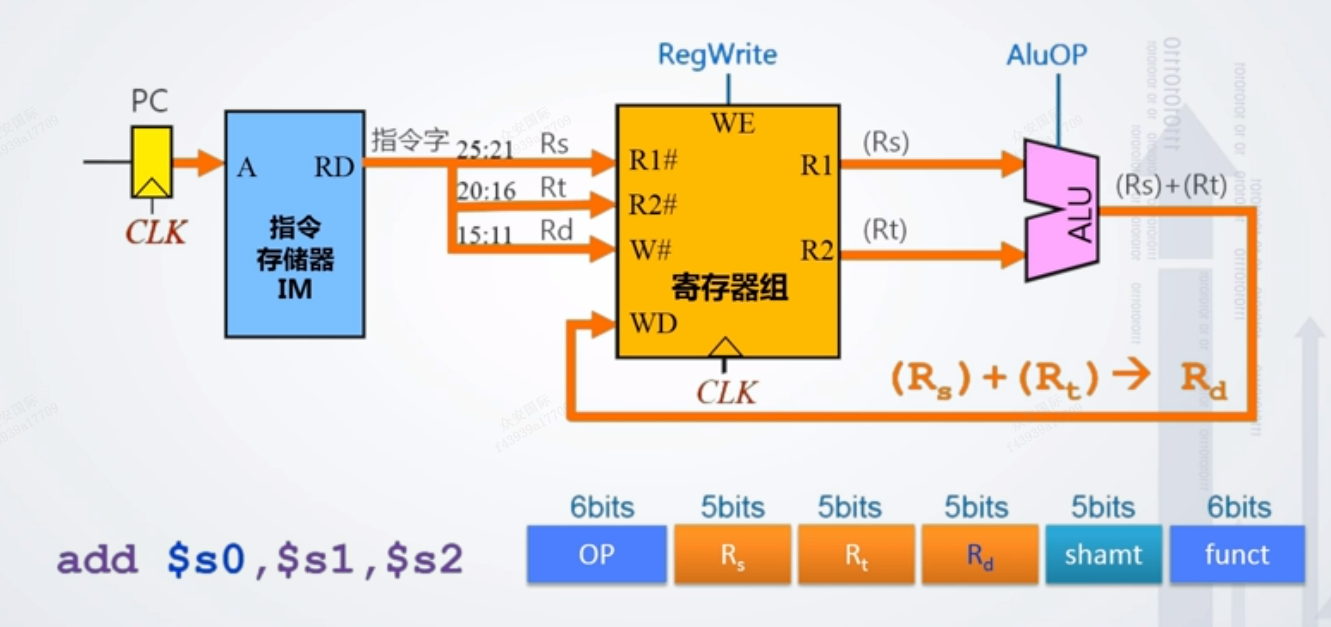

R型指令数据通路

以加法为例:add $s0, $s1, $s2 代表s0=s1+s2

即:Rs + Rt ->Rd

- 以PC为地址访问指令寄存器得到当前MIPS指令,标准的32位字长

- 根据指令格式32位很容易得到Rs(25位-21位), Rt(20位-16位),Rd Rt(15位-11位)三个字段值全部解析出来

- 有了三个字段需要提供一个通用寄存器模型通用寄存器堆,可以提供两路寄存器读,给出Rs和Rt的能够得到R1和R2对应寄存器的输出,所以寄存器组能够同时读取两个寄存器的值,同时可以通过Wd端写入到目标寄存器Rd中。所以目标寄存器组要支持两路读一路写

- 将Rs和Rt取出以后直接送入运算器ALU进行响应的运算,运算完以后,结果送入到写入端WD,当时钟到来时给寄存器一个写的使能,将对应的数据写入到寄存器组完成R型指令功能

I型指令数据通路

以lw指令为例(从存储器取值写到寄存器)

Lw $s0,32($s1)

Rt对应的是s0作为目标寄存器,对应的内存地址是s1地址加上16位立即数求和以后得到地址去访问内存取出对应的数据送入到目标寄存器

- 将指令取出以后将指令解析,解析出Rs(是要访问寄存器组取出Rs和立即数相加)所以将Rs直接连接寄存器组的R1端

- 同时将16位立即数送入符号扩展单元,由于16位必须扩展成32位才能送入ALU进行运算

- 当Rs取出后16位也扩展成32位后将Rs值和对应的立即数直接相加求得实际的访存地址,将地址送去实际地址存储器,经过一个存储器延时以后,就可以从存储器当中取得数据送回到寄存器的写入段WD

- 将数据从WD写入到目标寄存器Rd中就完成了整个操作

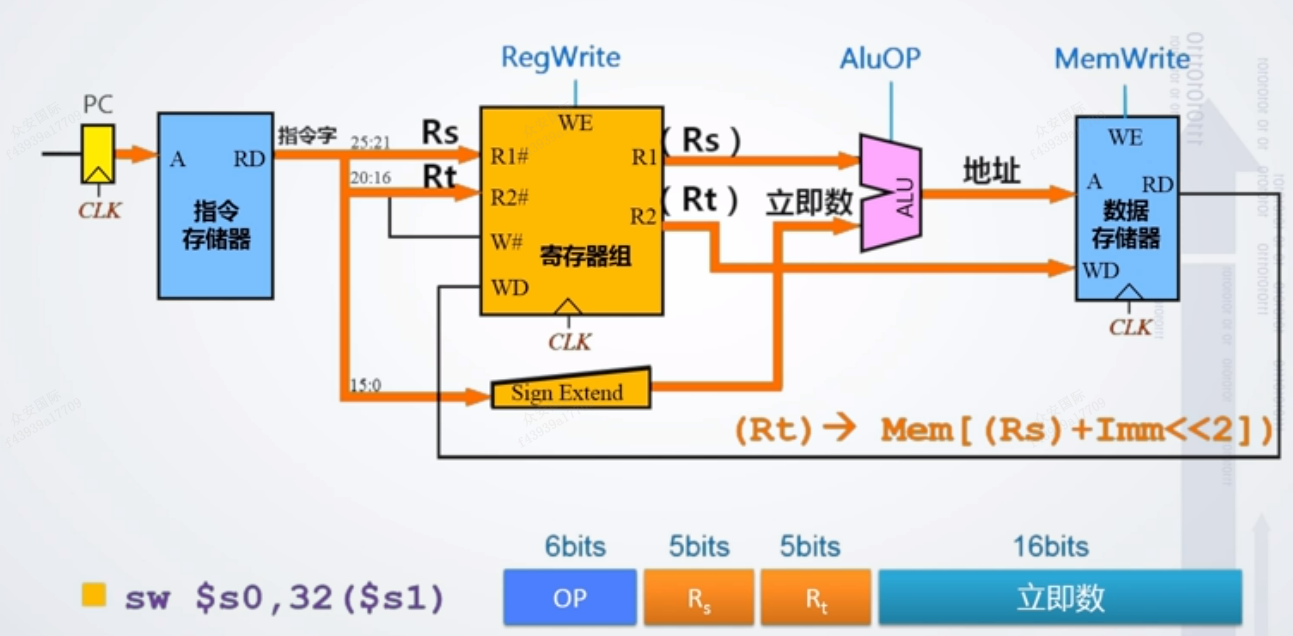

Sw指令数据通路(是将寄存器值写入到存储器)

Rs+立即数得到地址,将Rt的数据写到数据存储器,所以Rt可能是目标寄存器也可能是数据