6.11-微程序控制器

微程序控制器组成原理框图

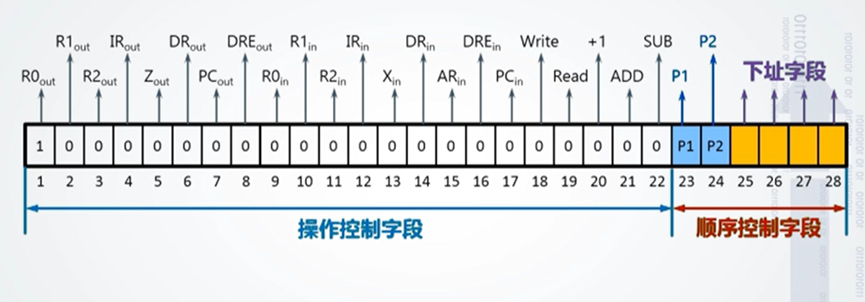

1. 单总线架构下的微指令格式

(1) 每一个控点对应一个信号,一共有22个控制信号,判别字段2两位,下址字段四位,一共包括28位

(2) 一条微指令对应一个时钟周期,微指令可以并发的给出控制信号所以只需要一个时钟周期

(3) 微指令操作信号的持续时间就是一个时钟周期,微指令操作控制字段的信号在该时钟周期内有效

(4) 指令在执行时候需要多少个时钟周期就设计多少个微指令

1. 单总线下微指令取指令执行指令通路

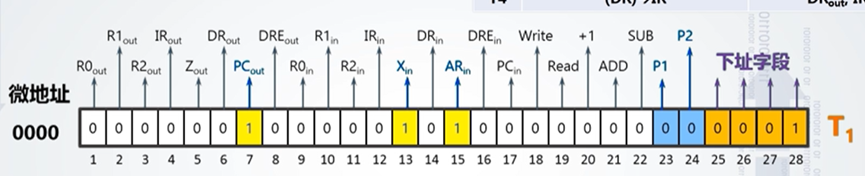

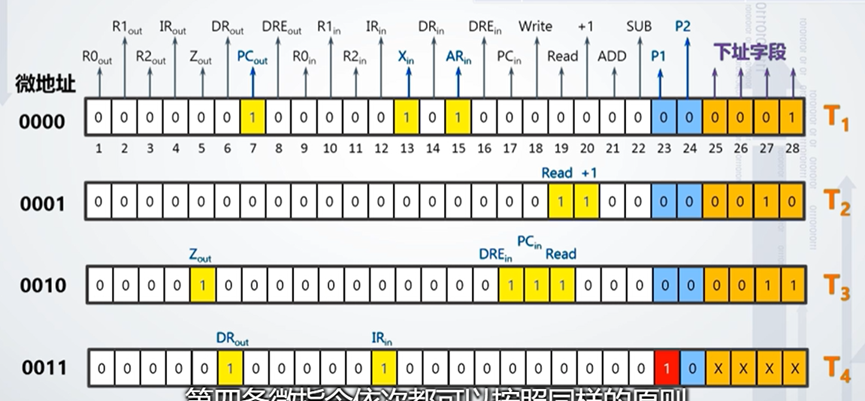

Mem[PC++] ->IR的执行过程

(1) T1第一个时钟节拍要完成PC到AR,PC到X的动作

(2) T2第二个节拍要完成PC累加,然后送回PC这样一个动作,同时要读内存

(3) T3第三个时钟节拍要完成读内存,将结果送到DR中工作

(4) T4第四个时钟将DR送到IR中来

需要四个时钟周期就需要四个微指令,一下为设计

- 第一个时钟周期给出第一个微指令,我们将这条微指令的地址成为0000,因为系统上电就要进入取指令状态,这条指令要给出的控制信号PC 要out送入AR中来,给出AR in,然后X要X in,黄色部分标识,执行这条指令可以并发给出三个控制信号,下址字段为0001,判别字段00,表示下一条微指令地址要有下址字段给出

- 第二条微指令就是0001,要完成X累加同时要读内存动作,ALU+1,以及内存的读信号

同样第三条第四条可以按照同样的原则设计

上面第四条指令完成DR到IR的传递要给出一个DR out,IR in,需要注意的是判别字段是1表示小一条指令不再有下址字段给出,也就是我们的微程序控制器根据事先约定的规则根据指令的功能寻找微程序入口地址,P1为1由地址转移逻辑决定

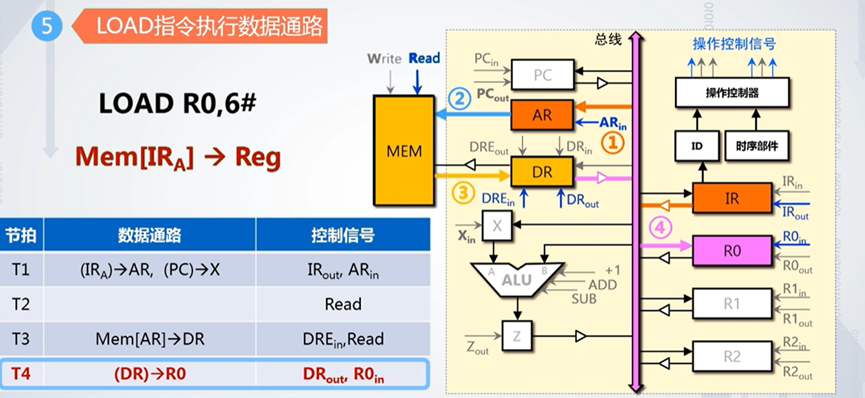

1. Load指令执行数据通路

Load R0,6#

Mem{Ira} ->Reg

(1) 第一个节拍先将IR的地址码部分送到AR

(2) 第二个节拍读内存

(3) 第三个节拍继续读内存,将内存值送到DR

(4) 最终将DR的值输出到对应的寄存器中

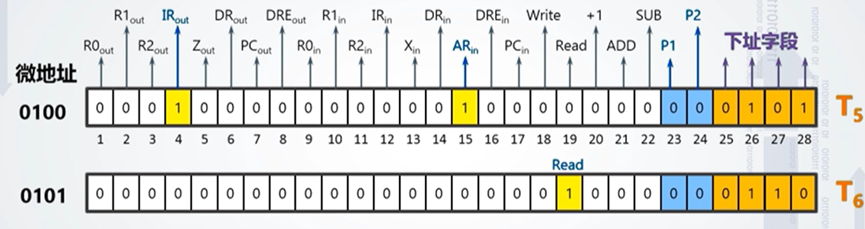

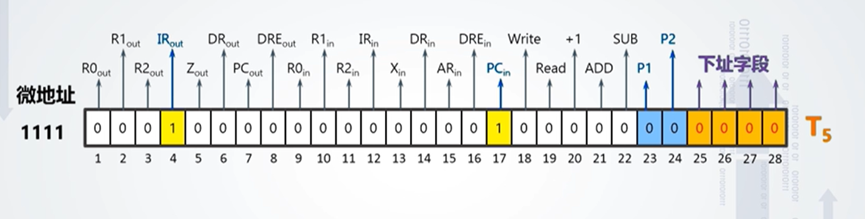

微程序设计

(1) 第一条微指令地址对应0100,操作控制字段IR out, AR in,判别字段全0,下址字段因为需要四个节拍需要顺序执行四个微指令,是相邻的指令0101

(2) 第二条微指令只需要读内存

(3) 第三个节拍也需要读内存,同时送入到DR中所以要DRE in

(4) 最后一个节拍完成DR送R0的数据通路,DR out R0 in,最后一个执行完成后要进入取指令阶段,所以下址字段就不是连续的了而应该跳回到取指微指令,或者取指微程序的第一条微指令,也就是0号单元,所以下址字段是0000也就是公共的微程序部分

2. Mov微指令

3. Add微指令

4. Store微指令

5. JMp微指令

6. 单总线指令

每一条指令最后一个执行完成后都要进入到0000起始取指地址,按照这个方法把CPU所有指令都构造完成后,并在微程序控制器中控制存储器中安排好位置,当这个微程序入口地址一旦确定,就可以根据指令的操作码与位置之间的关系设计微程序控制器的地址转移逻辑,微程序控制器的地址逻辑和微程序控制器的控制存储器的内容都安排好后整个控制器就设计完毕了