6.8-中央处理器硬布线控制设计(1)

基本原理

- 将控制器看成生产固定时序控制信号的逻辑电路

- 输入信号:指令译码,时钟信号,反馈信号作为输入

- 输出信号:功能部件控制信号序列

- 设计目标:最少原件,最快速度

- 理论基础:布尔代数

- 组成器件:门电路,触发器

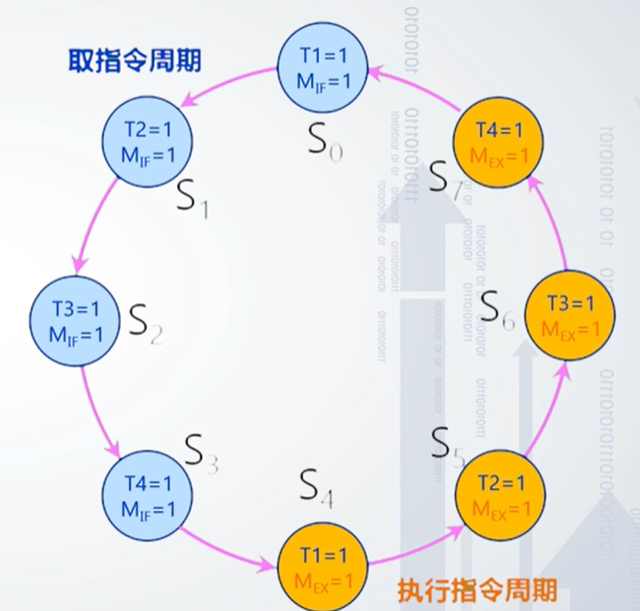

定长指令周期时序产生器 传统三级时序

要设计定长指令周期时序产生器,首先构建它的时序产生器,就是生成我们传统的三级时序的时序产生器,最重要的是时钟,就是所说的节拍,由节拍脉冲生成一个具体的状态周期电位,包括一下几点

- 取指令周期电位

- 执行指令周期电位

电位信号去标识对应当前指令处于哪个周期,取指高电平以后,马上进入低电平,正好是我们执行指令的高电平,这样依次的取指执行,取指执行,构成一个不断这样的循环,从而完成程序的自动执行

时序产生器状态机

- 由于上面所有指令都需要8个节拍,所以可以用8个状态,S0代表第一个状态进入取指令周期的第一个节拍,T1=1,当前MIF=1,表示现在处于取指令周期的第一个节拍,当时钟周期到来的时候,进入第二个节拍

- 第二个节拍T2=1,同时还是取指令周期MIF=1,依次第三第四个节拍,都是取指令周期的状态变化,进入第四个节拍以后,再来一个时钟周期,就要切换到我们的指令执行周期,进入S4状态

- 进入执行指令周期S4,T1=1,Mex=1,以此类推,到达S7,执行完执行指令周期后,就要重新进入到取指令周期S0

- 整个过程不依赖电平的信号,只依赖时钟的方波,可以用一个三位计数器来表示,一共8个状态从0-7依次做加法运算

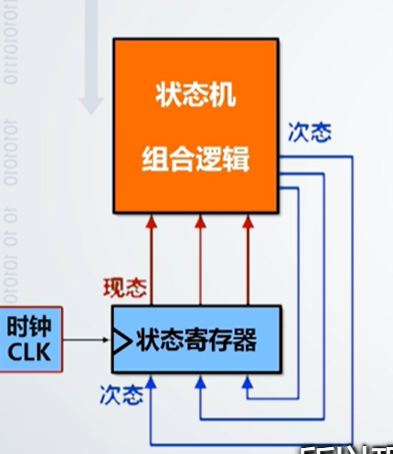

如何构建这个三位的时序计数器

- 有一个状态寄存器三位来表示状态,状态寄存器的输出就是现态,这个现态会经过一个状态机组合逻辑生成我们的次态,次态就是指S0,完成后要到S1,S0就是现态S1就是次态,那么S2就是S1的次态

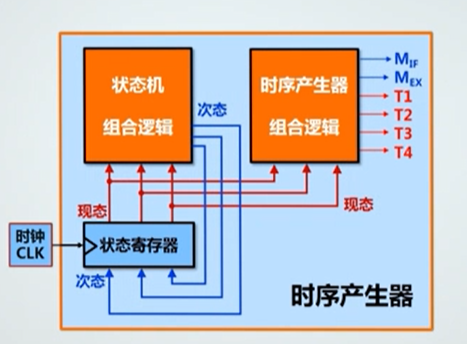

构建周期电位输出电路

- 在上面的基础上加上一个时序产生组合逻辑,直接生成我们所需要的状态周期电位MIF,MEX以及具体的四个节拍电位T1,T2,T3,T4

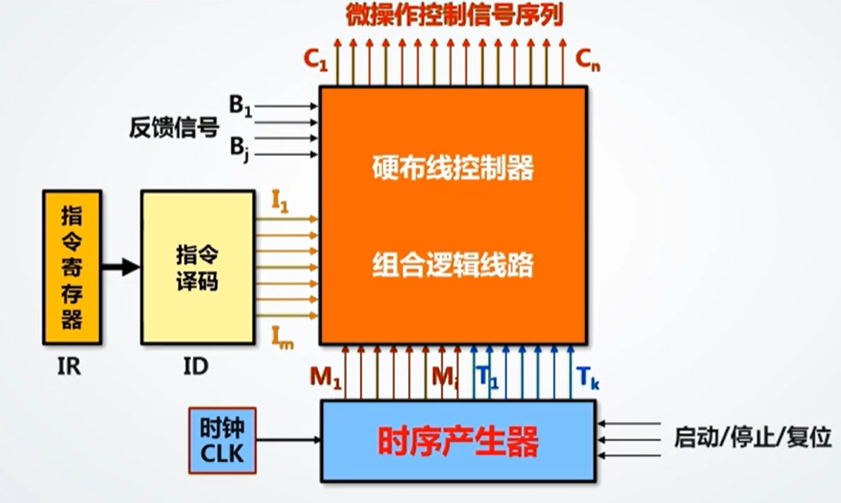

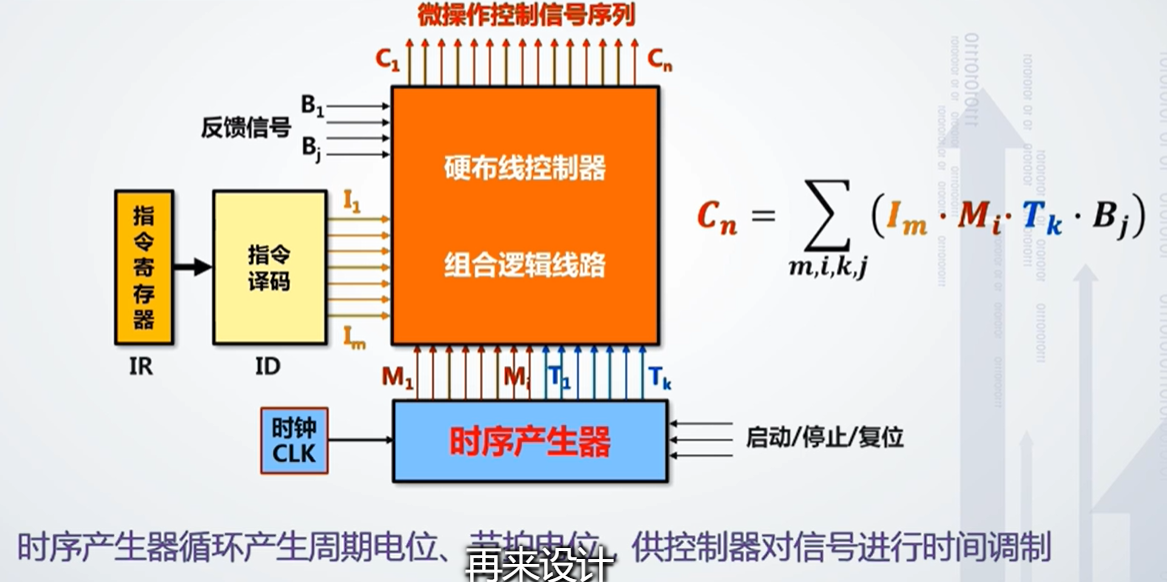

硬布线控制基本架构

- 有了时序产生器之后,就可以生成周期电位信号,节拍电位信号M和T,再在对应的这个译码信号配合下,反馈信号的配合下,由我们的硬布线控制器来生成对应的控制信号序列,由于时序产生器已经承担了时序功能,所以硬布线控制器变成了纯组合逻辑

- 设计硬布线控制器的逻辑思路,我们每一根信号都可以变成我们的指令译码信号,以及这些周期电位信号,以及反馈信号的这样一个函数表达式Cn等于某一条指令Im(什么指令译码情况,比如说是加法指令,还是减法指令)在什么周期电位,在什么节拍电位,在什么条件下产生累加求和,就是一个纯组合设计逻辑设计方法,如下图

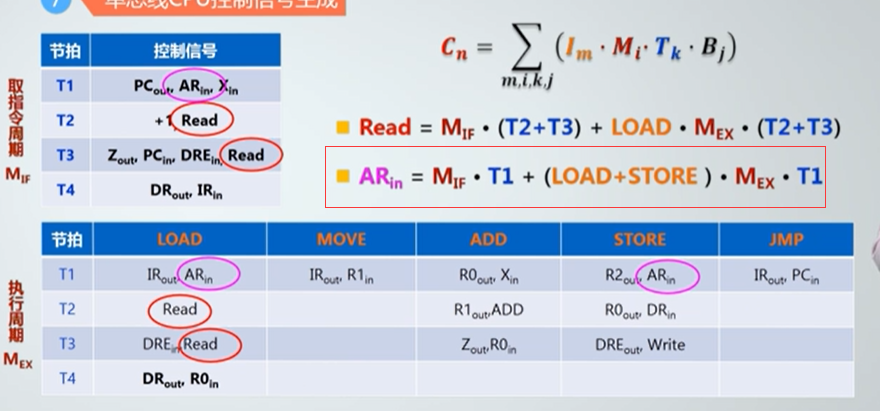

单总线CPU控制信号生成

以内存读信号为例:内存读信号在取指令周期的第二个节拍第三个节拍给出,就是在我们执行指令周期Load指令的第二个周期的第二个和第三个节拍给出

所以可以写出

Read = Mif * (T2 + T3)+ LOAD*Mex*(T2+T3)

它会在第一个取指令周期MIF的第二个节拍,第三个节拍,或者在Load指令的执行周期的第二个节拍和第三个节拍给出

同样AR in的逻辑表达式可以写成

固定指令周期硬布线控制器设计过程总结

- 设计三级时序产生器:所有指令固定机器周期数,节拍数

- 列出所有机器指令周期流程图,明确每个节拍的控制信号

- 找出产生同一微操作控制信号的条件,把条件累加起来构成逻辑表达式

- 写出各微操作控制信号的布尔表达式

- 化简各表达式

- 利用组合逻辑电路实现

浙公网安备 33010602011771号

浙公网安备 33010602011771号