6.6-总线结构与CPU指令周期(1)

单总线架构基础上如何执行指令

指令功能

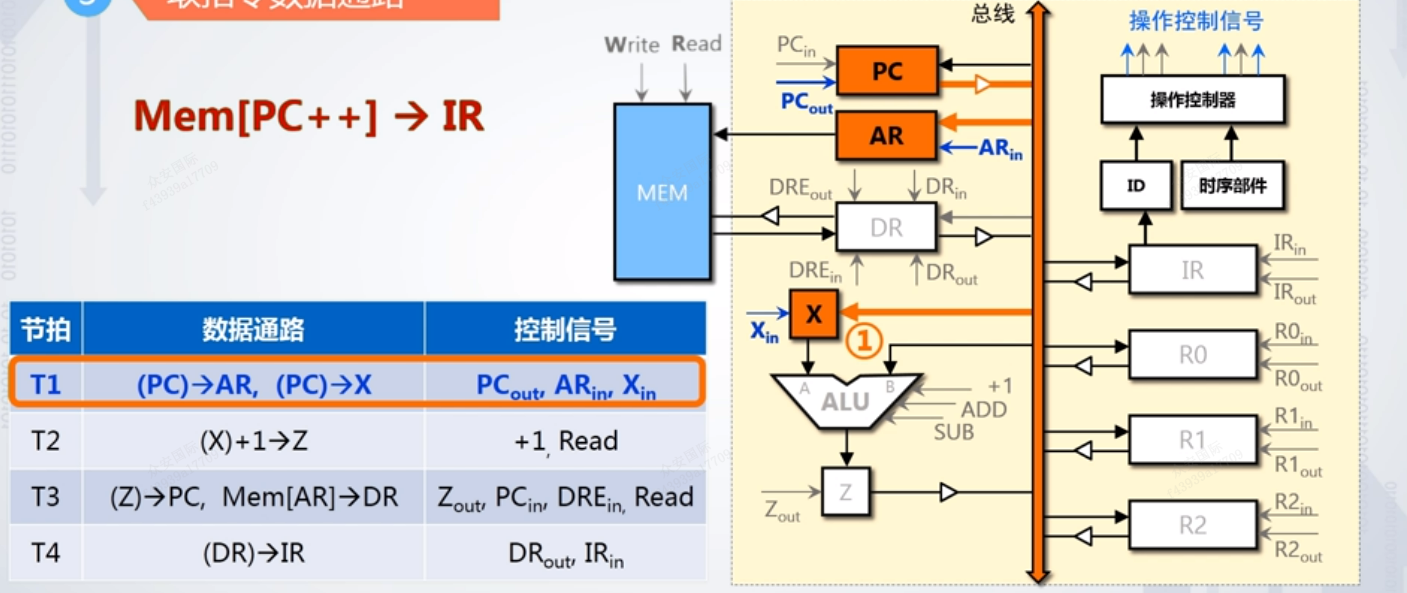

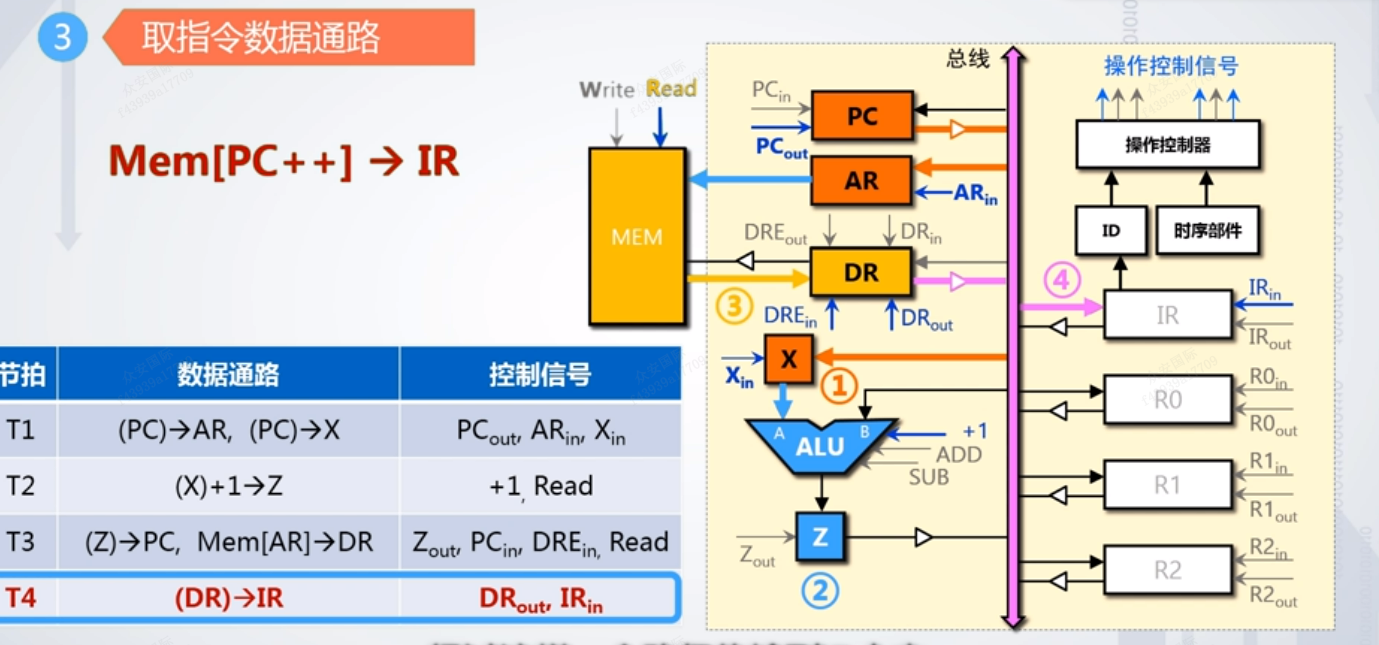

- Mem[PC++] ->IR取指令的数据通路

- 取指令,将指令从主存取出送到指令寄存器IR中,然后再将PC++,取指令需要反复的通过数据总线传递数据。首先以PC为地址访问主存,所以首先我们要将PC的值传递到AR中来,另外PC++,送到运算器的一个X中,第一步要将PC的值取出,给出一个PC-out的信号控制这个三态门值输出到总线,然后再由总线输入到AR中,需要给出一个Arin的写使能信号,在下一个时钟到来时将对应的PC值输出AR,同时PC的值要完成+1的操作,通过总线传递到这里,一样要给出一个Xin的这样一个操作,保证数据能够输入到X,在时钟到来之后我们给出对应的写使能以后,我们对应PC的值就会传递到AR和X中,所以第一个时钟到来的时候X和AR中所存放的值就是我们PC的值

-

- 第二个时钟周期到来之后,做+1的动作,给出ALU的运算选择信号+1,让PC的值加上1送到结果,同时给出读内存的信号

-

- 第三个节拍数据已经在总线上,我们要把对应的数据写入到DR中来,将Z的值送到PC,需要给出Z out控制信号,将Z的值输出到数据总线,再给出一个PC in,在写使能的配合下在时钟的配合下,我们总线上的数据才能够传递到对应的PC,另外将存储器的值由数据总线传送到DR中来这个是在第三个时钟完成的

-

- 最后一步当数据已经在DR,也就是我们的指令已经从主存取到DR,最后要将DR送到IR,而DR到IR还要经过总线,所以第四个时钟周期我们需要将DR送到IR,需要给出DR out, IR in,就可以控制IR从总线输入一个数据,在第四个时钟周期完成响应的动作,当指令取出以后,再送到指令译码器生成操作控制信号,这就是完整的取指令的数据通路

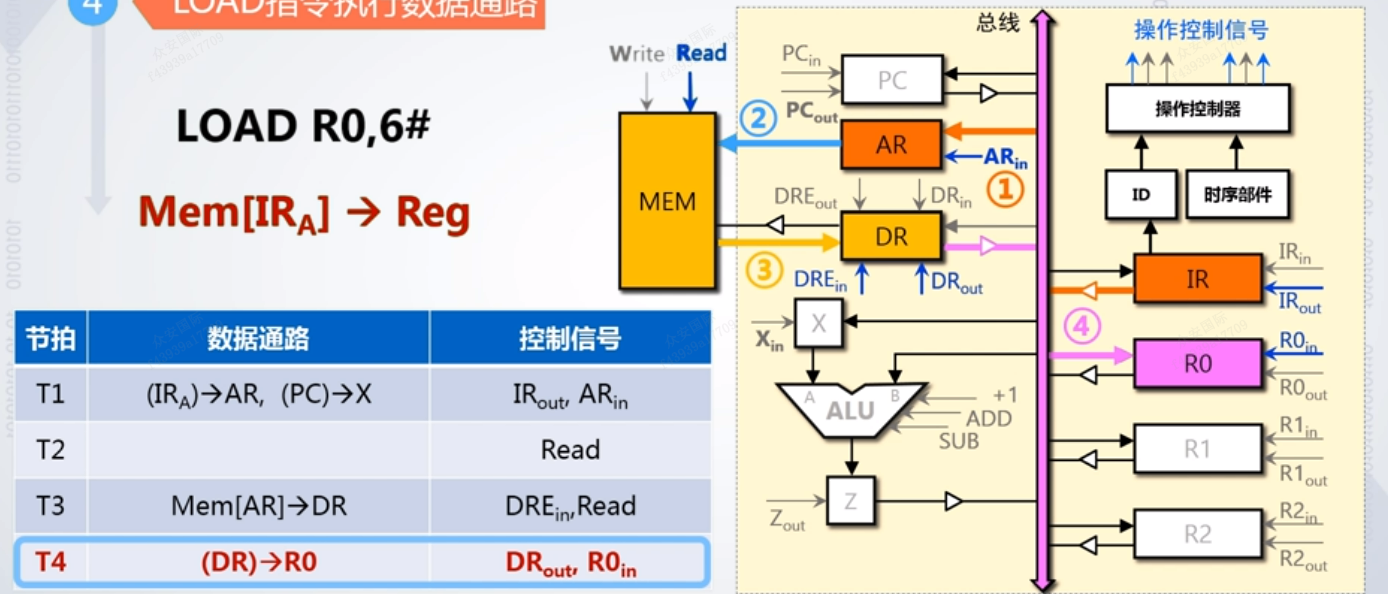

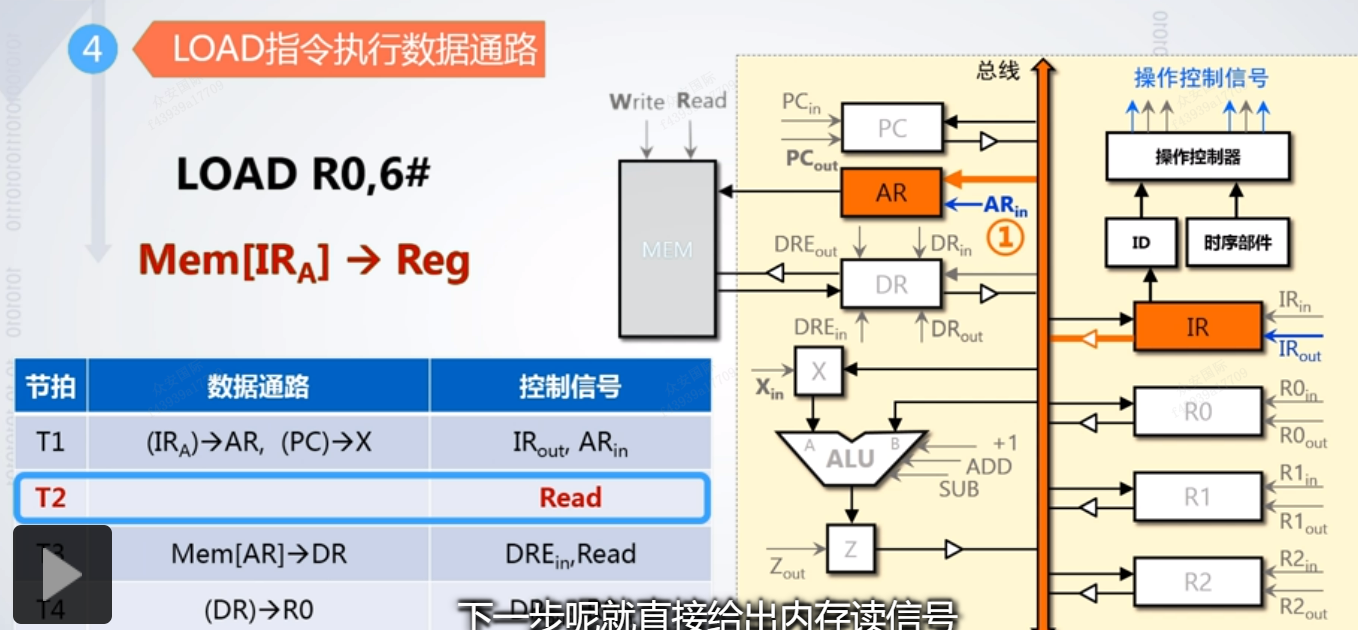

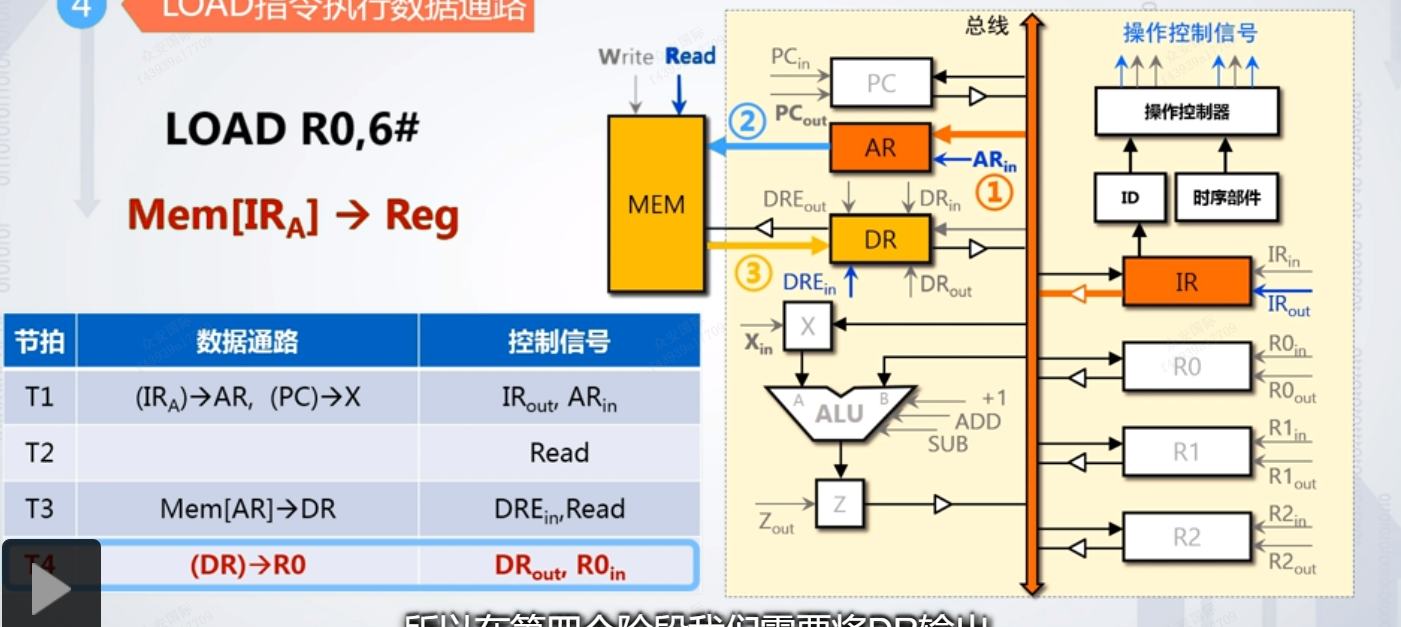

- 当指令取出后生成对应的控制信号后,进入到指令执行阶段,以Load指令为例,Load R0,6#是将6号存储单元取出以后送到R0中

- 首先要将IR的地址码送到AR去访问主存,所以第一步要给出IR out,将对应的输出总线送到AR的输入端,给出AR in再第一个时钟的配合下我们可以将对应的IR的地址码也就是我们6的值送到AR中来,当6一旦再AR里面,下一步就可以访问主存了

-

- 下一步直接给出内存读信号 Read

- 第三拍我们再开始将读数据取出送到DR中,跟上面的取指令一样,只要将对应的写使能打开,第三个时钟到来的时候,就可以将能存的数据写入到DR中,所以6号存储单元的数据就到DR中了

-

- 第四拍的时候我们需要把DR传输到我们对应的R0寄存器,所以再第四个阶段我们需要将DR输出,给出DR out信号,将数据传递到总线,送入到R0的输入端,给出一个R0 in,再第四个节拍的时候,第四个时钟脉冲到来的时候,响应的数据就会写入到R0中来