6.5-指令周期

指令执行一般流程

- 不同指令功能不同,数据通路不同,执行时间不同,如何安排时序

访存指令,寄存器运算指令,加减法指令与除法指令

- 程序执行一般流程

系统在上电之后,就一直进入取指令,操作指令的死循环

- 从取指令开始,以PC为地址访问内存将指令从内存取出,送到指令寄存器,然后PC自增1,PC+一条指令的长度

- 取完指令之后,进行指令译码,将指令产生的的指令译码信号生成对应的控制信号,然后进入执行阶段,可能要取操作数,所以有操作数地址计算这个阶段(可能需要两个时钟周期)

- 进入执行阶段,进行最终的执行,甚至是运算或者是数据传输,在执行阶段做数据的操作

- 执行完毕以后要进行写回操作,也可能要进行地址的计算以及数据的写回

- 当一条指令结束后会判断当前系统是否存在中断,如果有中断,要进行中断响应,如果没有中断或者异常直接返回取指令的公共操作。如果有中断,需要进入中断响应周期,叫做中断隐指令,要判断当前中断是什么样的中断,如果有多个中断源,还要根据优先级进行判断并且要找到对应中断 的中断程序入口,将中断程序的地址入口送入到PC,同时把原有的PC要保存到系统的堆栈区,这样才可以完成中断后返回主程序

指令周期的基本概念

- 时钟周期

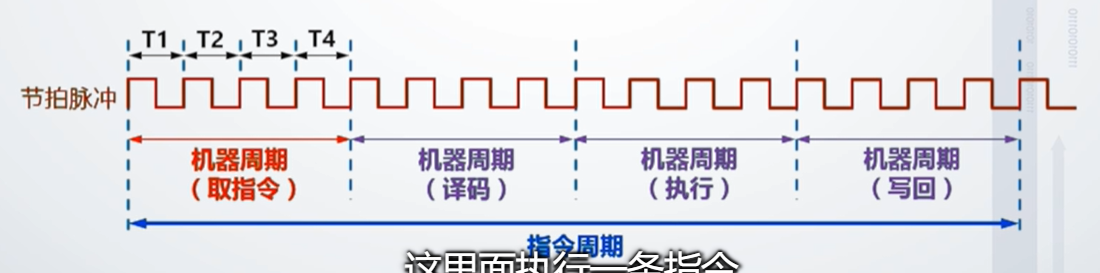

时钟周期 = 节拍脉冲 = 振荡周期 可以完成一次简单的操作

振荡器按照固定的频率进行震荡,也就是我们所说的主频,产生基础的方波,在一个时钟周期内,并不能完成非常复杂的操作,只能完成一次微操作,比如一次寄存器的写入操作,可能需要一个时钟周期完成

- 机器周期

机器周期 = CPU周期,从主存中取出一条指令的最短时间,因为有cache,可以理解为从cache取出指令的最短时间,成为一个CPU周期。机器周期比时钟周期要长,在一个时钟周期是无法取出一条指令的。可以完成复杂操作

比如4个时钟周期是一个CPU周期,根据CPU架构和需求定的

- 指令周期:

从主存去一条指令并执行指令的时间

包括:机器周期(取指令)+机器周期(译码)+机器周期(执行)+机器周期(写回)16个节拍

指令控制同步

不同指令功能不同,复杂度不同,如何进行时间控制,指令同步控制有两种方式

- 定长指令周期:早期三级时序系统

机器周期数固定,节拍数固定,按机器周期同步,mips周期

- 变长指令周期:现代时序系统

机器周期数可变,节拍数可变,按时钟周期同步,mips多周期

三级时序系统

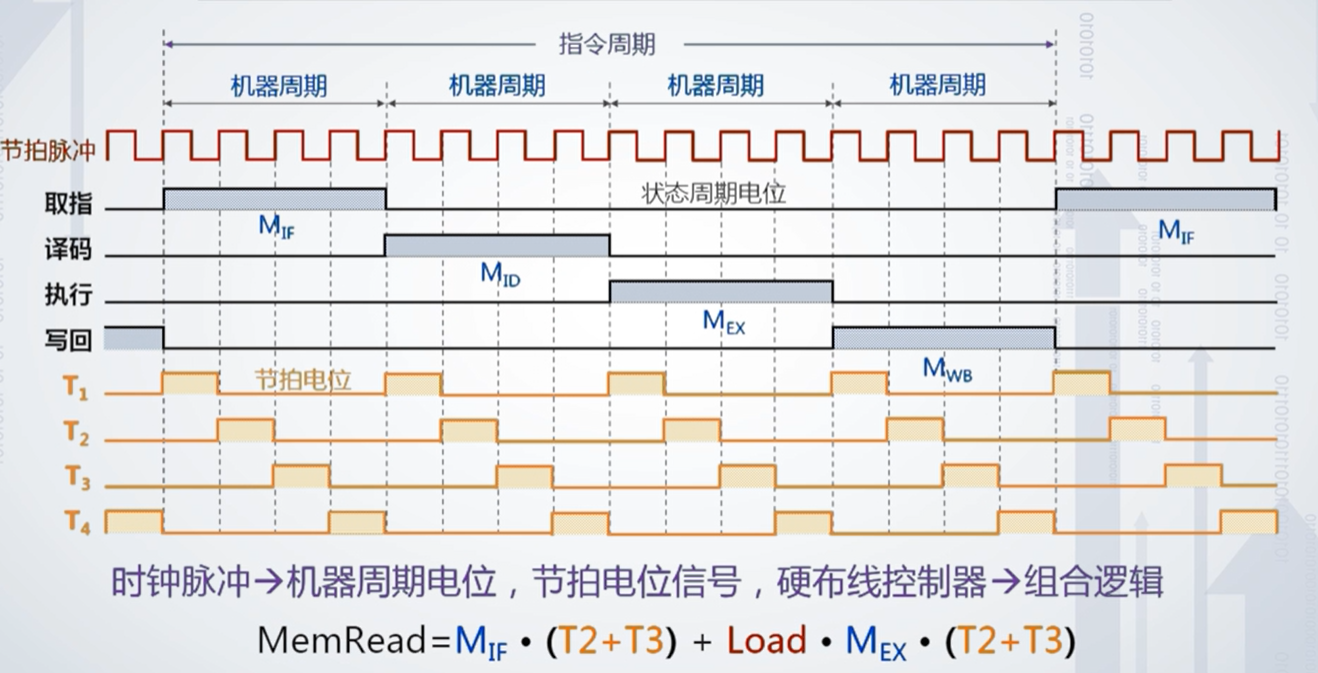

- 最基本的方波节拍脉冲,在这个基础上,我们可以生成一个机器周期电位,用电平来表示当前处于什么阶段,比如说当前处于取指令阶段,那我们就用取指周期电位这样一个状态周期电位表示当前处于取指周期

- 进入取指令周期之后下一个节拍就进入了译码阶段,叫做MID阶段也是一个电位

- 第三个状态周期电位,成为执行周期电位

- 第四个为写回周期电位,每个电位都包含四个节拍,根据系统设计的

- 完成后又返回取指周期,不断的循环执行

- 除了状态周期电位还有节拍电位,高与低也表示处于某一个周期的某一个节拍,节拍就是用来代表某个周期的某一个节拍。比如取指周期的第一个节拍。一个机器后期需要16个节拍,也就是所有机器周期都需要16个节拍才能完成

- 设计实现比较简单,所有跟时钟有关的信号都变成了电平信号,将时钟周期电位变成了机器周期电位,时钟信号变成了逻辑信号使得我们最终要设计实现的硬布线控制器不再是同步时序电路,变成了组合逻辑电路。可以控制信号的产生时序

比如内存读取信号:

时序产生器与控制器产生逻辑

- 从指令寄存器取得的指令送到指令译码器产生所有指令的译码信号,这个译码信号的高电平和低电平可能就代表一个指令,假设这个信号是高电平代表加法指令,另一根代表减法指令,有多少个指令就有多少根译码信号

- 这个信号作为输入送入到硬布线控制器

- 基本的时钟在时序产生器

- 时序产生器的作用就是循环产生这些周期电位节拍电位,控制器对信号进行时间调制

现代时序系统

不再采用这种固定的时序,所有指令都采用固定的机器周期数,对慢速指令有利,对快速指令不公平,所以对整个系统结构做了一个变化,刚才的时序产生器演变成一个状态寄存器,时钟作为输入到状态寄存器,寄存器的现态,他的值输出到一个有限状态机的组合逻辑,由它对现态进行加工,生成次态,次态作为输入送到状态寄存器,每来一个时钟输入,次态就会变成现态,所以指令执行到什么时间,完全由指令的状态决定,这个状态机就是一个逻辑组合,它的输入来自于指令信号以及对应的现态,而当前控制信号怎么产生和这边的电路没有关系只与状态寄存器有关系,当前处于什么状态就给出什么信号,每一个状态的改变是受时钟信号驱动的,这种方式最大的好处是可以按照时钟脉冲来进行同步,指令需要多少个时钟周期就给多少个时钟,而不是固定的需要多少个时钟周期。性能最佳

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· 没有Manus邀请码?试试免邀请码的MGX或者开源的OpenManus吧

· 【自荐】一款简洁、开源的在线白板工具 Drawnix

· 园子的第一款AI主题卫衣上架——"HELLO! HOW CAN I ASSIST YOU TODAY

· Docker 太简单,K8s 太复杂?w7panel 让容器管理更轻松!