k64 datasheet学习笔记25--Multipurpose Clock Generator (MCG)

0.前言

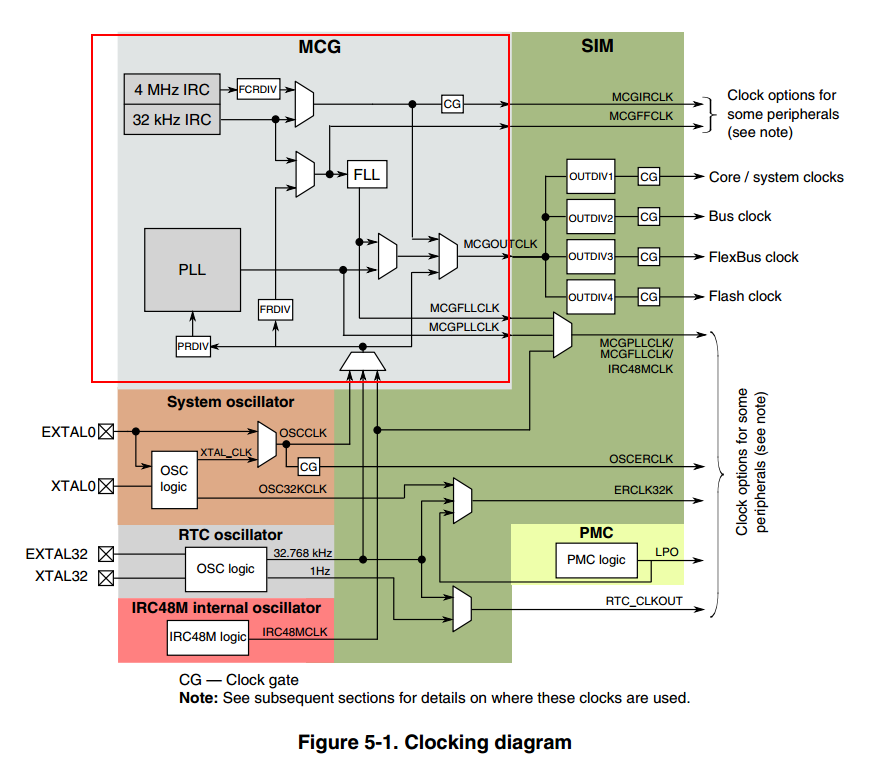

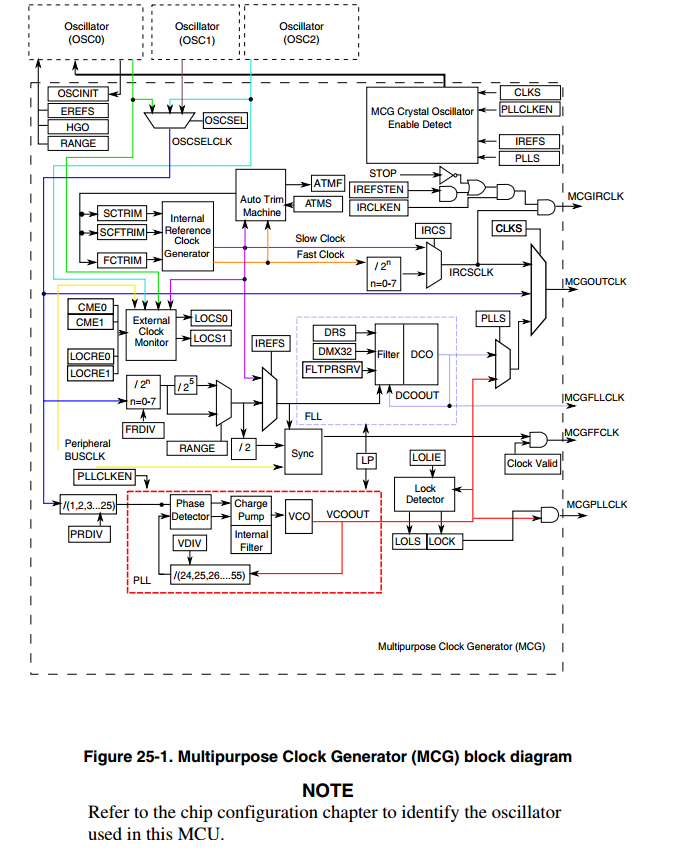

MCG模块为MCU提供了几种可选时钟源。模块包含一个FLL和一个PLL。FLL使用内部或外部参考时钟是可控的,PLL受外部参考时钟控制

模块可以选择FLL或PLL输出时钟,或内/外部参考时钟作为MCU系统时钟源

1.特性和模式

1.1 特性

1.FLL

数字控制OSC(DCO)

DCO频率范围可通过编程达到4个不同的频率范围

对于低频外部参考时钟源通过编程最大化DCO输出频率

如果FLL参考频率未变,切换时钟模式时可保证当前的频率不被重置??

内部或外部参考时钟可用做FLL时钟源

可以用作其它片上外设的时钟源

2.PLL

电压控制的OSC(VCO)

外部参考时钟用作PLL源

Modulo VCO frequency divider

Phase/Frequency detector

Integrated loop filter

可以用作其它片上外设的时钟源

3.内部参考时钟产生器

• Slow clock with nine trim bits for accuracy

• Fast clock with four trim bits

• Can be used as source clock for the FLL. In FEI mode, only the slow Internal

Reference Clock (IRC) can be used as the FLL source.

• Either the slow or the fast clock can be selected as the clock source for the MCU.

• Can be used as a clock source for other on-chip peripherals.

4.Control signals for the MCG external reference low power oscillator clock generators

are provided:

• HGO, RANGE, EREFS

5.来自晶振的外部时钟

可以用作FLL或PLL的源

可以选择作为MCU的源

6.来自RTC的外部时钟

可以用作FLL或PLL的源

可以选择作为MCU的源

7.当运行在FBE, PEE, BLPE, or FEE 模式,用RESET和中断请求来监控外部时钟

8.中断请求锁定使用的PLL?

9.Internal Reference Clocks Auto Trim Machine (ATM) capability using an external

clock as a reference ?

10.PLL和FLL分频支持

11.快速内部参考时钟分频支持

12. PLL CLK作为其它外设的时钟源

13.FLL CLK作为其它外设的时钟源

14.MCG Fixed Frequency Clock (MCGFFCLK) 作为其它外设的时钟源

15MCG Internal Reference Clock (MCGIRCLK) 作为其它外设的时钟源

1.2 操作模式

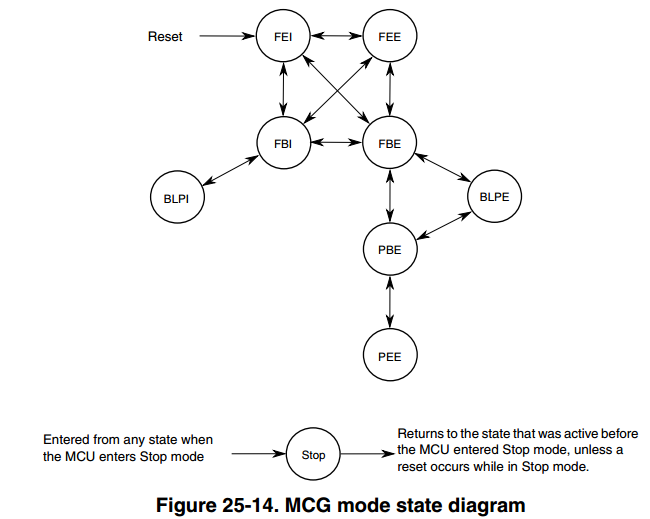

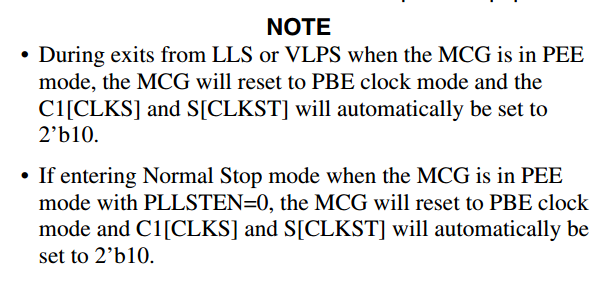

The MCG has the following modes of operation: FEI, FEE, FBI, FBE, PBE, PEE, BLPI,BLPE, and Stop.

2. 外部信号

3. Memory Map/Register Definition

TODO

4.功能描述

4.1 MCG模式状态图

MCG模式包含如下几种:

参考spec p598

浙公网安备 33010602011771号

浙公网安备 33010602011771号