k64 datasheet学习笔记4---Clock distribution

1.前言

本文主要讲述K64时钟配置相关的内容.

2.clock overview

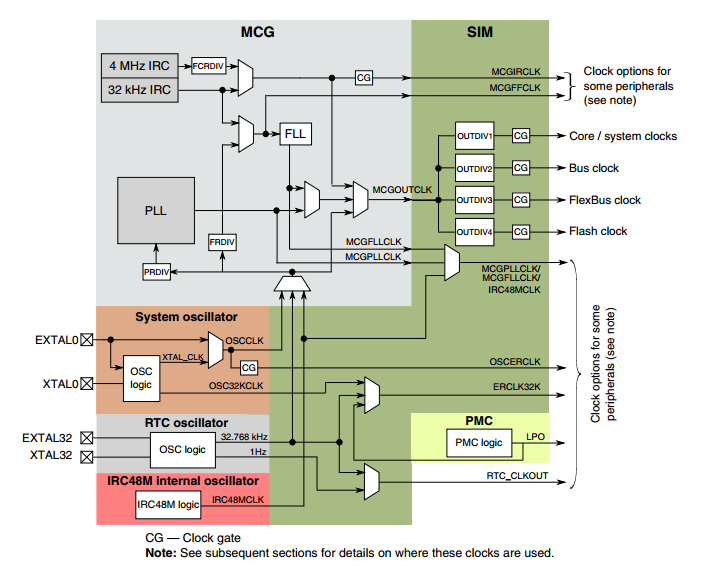

2.1 clock diagram

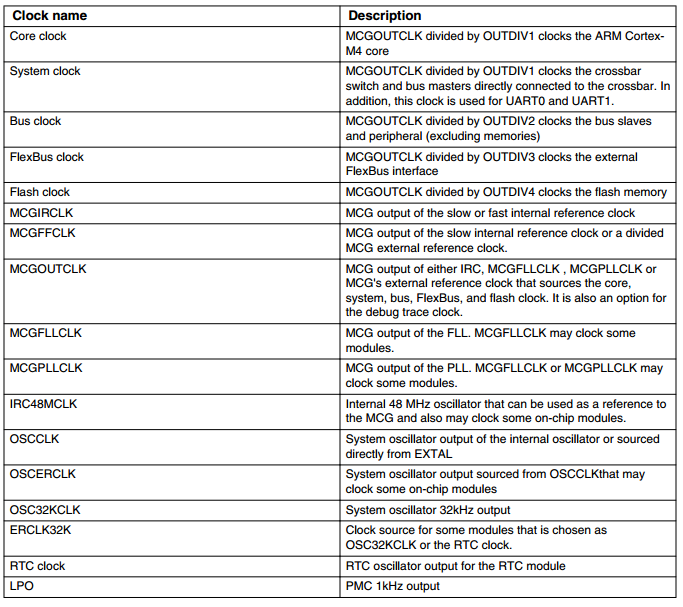

2.2 对clock diagram的信号说明

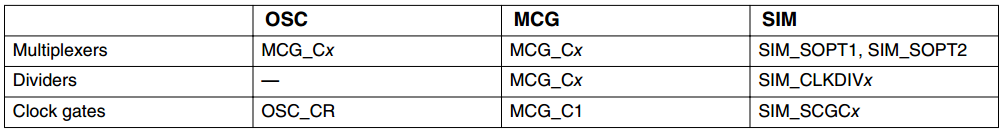

(1)MCG决定哪个clock source用作系统时钟,系统主要的时钟来自于MCGOUTCLK

(2)系统时钟源的选择和配置主要由MCG模块控制

(3)时钟分频和clock gate的配置主要SIM模块控制

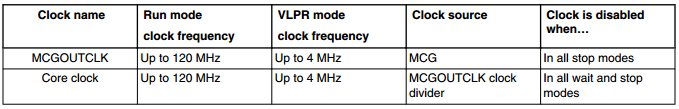

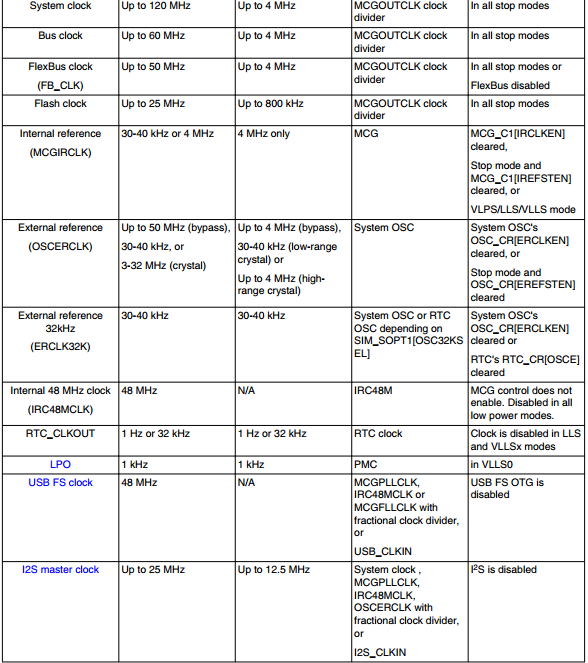

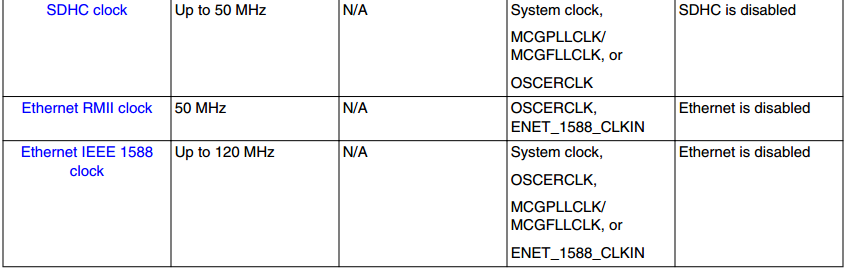

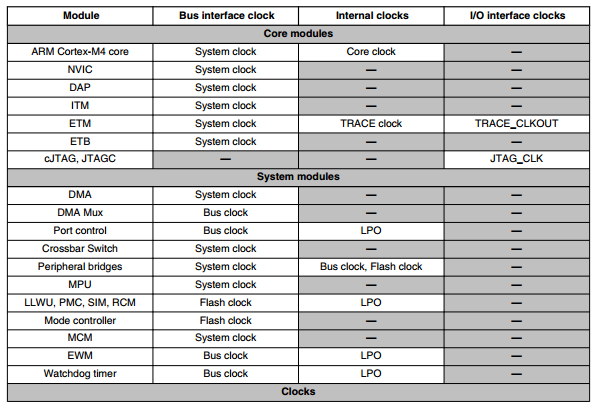

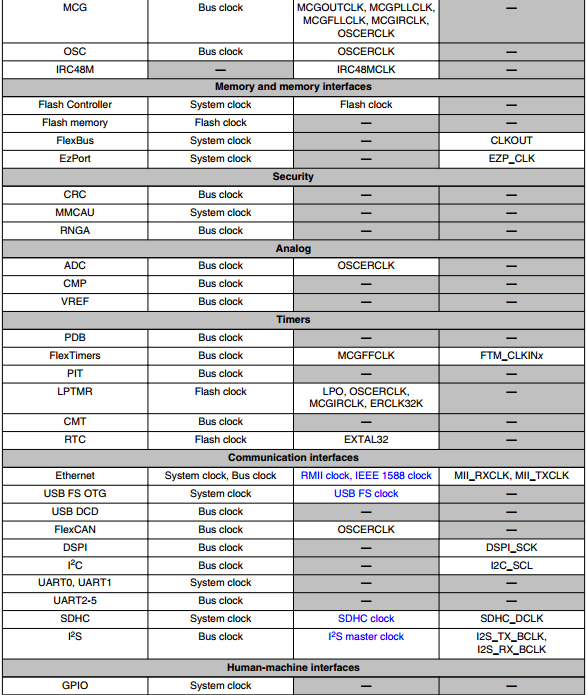

2.3 device clocks summary

注:

如下为内部时钟需求

1. The core and system clock frequencies must be 120 MHz or slower.

2. The bus clock frequency must be programmed to 60 MHz or less and an integer

divide of the core clock.

3. The flash clock frequency must be programmed to 25 MHz or less and an integer

divide of the core clock.

4. The FlexBus clock frequency must be programmed to 50 Mhz or less and an integer

divide of the core clock

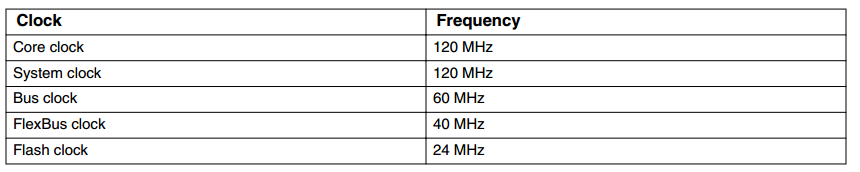

下面是一个示例:

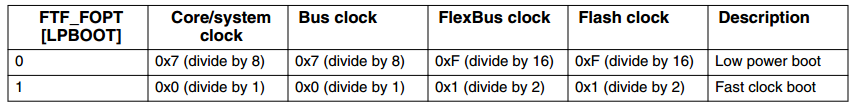

3. Clock divider values after reset

The flash memory's FTF_FOPT[LPBOOT] bit controls the reset value of the core clock, system clock, bus clock, and flash clock dividers as shown below:

4. VLPR mode clocking

TODO

5.CLOCK GATING

The clock to each module can be individually gated on and off using the SIM module's SCGCx registers

6.Module clocks

- UART clocking

UART0 and UART1 modules operate from the core/system clock, which provides higher performance level for these modules. All other UART modules operate from the bus clock.

7.参考文档

[1] K64P144M120SF5RM.pdf

浙公网安备 33010602011771号

浙公网安备 33010602011771号