eMMC基础技术2:eMMC概述

0.前言

本文主要参考eMMC规范,从总体上对eMMC 进行简要介绍。主要包含如下的内容:

(1)eMMC系统的总体架构

(2)eMMC的总线协议

(3)device controller

(4)flash memory

1.eMMC系统总体架构

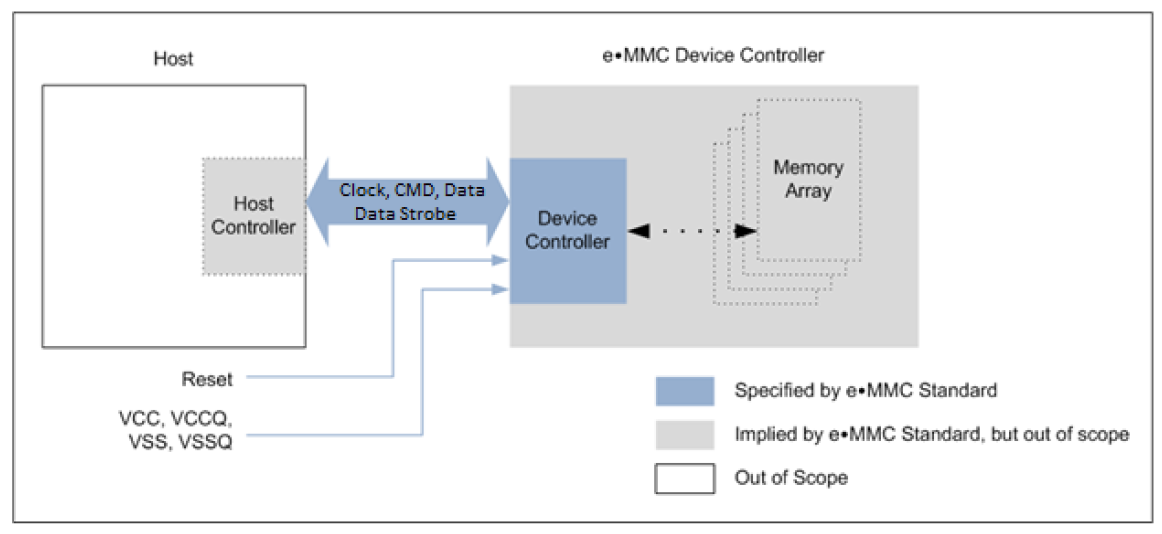

图 eMMC 系统总体架构

eMMC规范主要定义了Device Controller和接口的相关规范,如图中蓝色部分标识

- power部分

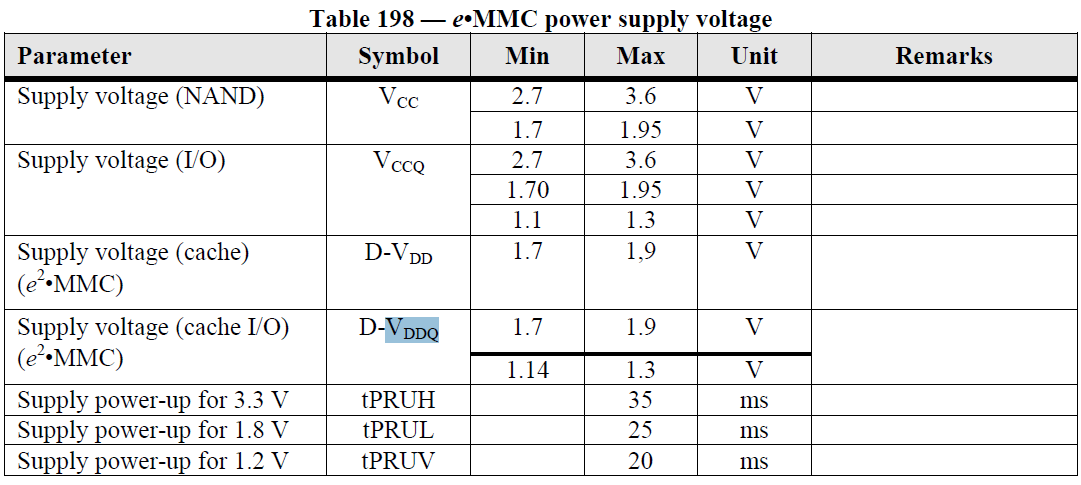

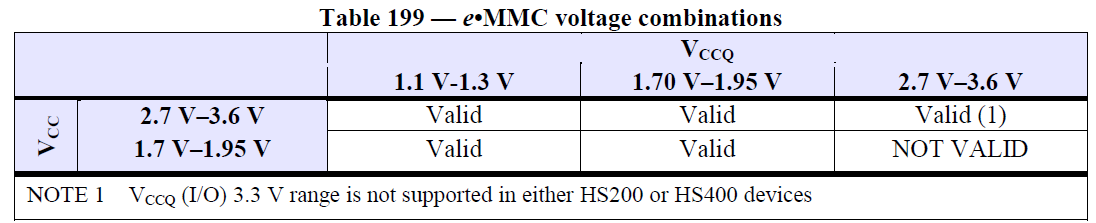

(1)VCCQ主要用于MMC IO BLOCK的供电也就是与host接口IO部分的供电,同时也给eMMC core供电;

VCC主要给eMMC内部的flash memory,以及eMMC core与flash接口部分IO的供电;VCCQ和VCC分为两种电压,一种电压是high voltage(2.7v~3.6v),一种电压是dual voltage(1.70v~1.95v和2.7v~3.6v)

(2)VSSQ是IO的地也就是eMMC内部的CORE的地,VSS是eMMC内部的flash的地;

图 eMMC供电

注:VCCQ一定要小于或等于VCC

- bus部分

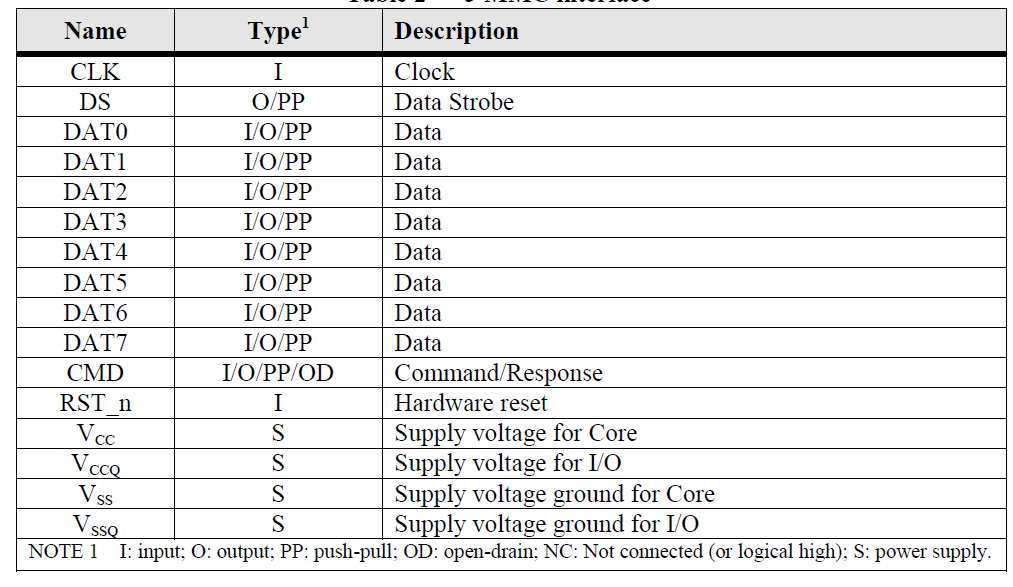

有11条信号线:(1)clk, 0~200MHZ,每个cycle可以在上升沿或下降沿传输,也可以在上升沿和下降沿都传输;(2)data strobe,由slave device 发送给host controller,主要用在HS400 mode(5.1规范?),频率与clk一致,用于host同步接收device的data(上升沿和下降沿有效),response和CRC status(只有上升沿有效);(3)cmd,双向信号线,用于从host发送命令给device和device发送response给host,有两种操作模式:open drain(初始化模式)和push pull(fast command transfer)(4) 8 bit data bus,双向信号线,工作在push pull mode,支持 1bit, 4bit, 8bit传输,默认上电或reset后只有DATA0用于数据传输,可以通过命令配置有多少条数据线用于传输数据。在device内部,DAT1~DATA7包含上拉电阻,平时不使用时保持上拉状态(也就是高电平??),使用时则断开上拉。

- Host Controller

通过发送CMD读写device端数据或通过CMD对device端进行配置

- eMMC device controller

实现对memory的管理,接收bus端的CMD,实际读写I/O寄存器

- flash memory

包含了实际的存储介质nand flash

图 eMMC接口

注:

1.4.1规范之前使用32位地址,最高容量达到2G;

2.4.1之后采用512B扇区访问模式,可支持大于2G的存储空间

2. eMMC总线

2.1 eMMC总线协议

eMMC 总线中,可以有一个 Host,多个 eMMC Devices。总线上的所有通讯都由 Host 端以一个 Command 开发发起,Host 一次只能与一个 eMMC Device 通讯。

系统在上电启动后,Host 会为所有 eMMC Device 逐个分配地址(RCA,Relative device Address)。

当 Host 需要和某一个 eMMC Device 通讯时,会先根据 RCA 选中该 eMMC Device,只有被选中的 eMMC Device 才会响应 Host 的 Command。

- command: 任何操作都要以CMD开始,只能由host发往device,且要串行完成;

- response: 在接收到host端发送的CMD,device作为回应将通过command line发送一个response,只能有device发往host,且只能通过command line串行传输;

- data: data可由host发送device(写)可以由device发往host(读),data线可采用1线,4线,8线传输,对于每条data线,可以选择单沿传输(single data rate)还是双沿传输 (dual data rate)

- crc status:用于device发送给host告知接收到的写入数据校验是否成功

2.2 bus speed modes

随着 eMMC 协议的版本迭代,eMMC 总线的速率越来越高。为了兼容旧版本的 eMMC Device,所有 Devices 在上电启动或者 Reset 后,都会先进入兼容速率模式(Backward Compatible Mode)。

在完成 eMMC Devices 的初始化后,Host 可以通过特定的流程,让 Device 进入其他高速率模式,目前支持以下的几种速率模式

2.3 clk control

1.总线速率在任何时刻都可以改变;

2.不带回应的命令,命令结束位后有8个clock;

3.带有回应的命令,设备响应结束位后有8个clock;

4.读数据传输。在上个data blcok的结束位后有8个clock;

5.写数据传输,CRC status token结束位后有8个clock

2.4 Error conditions

1.CRC and illegal command

如果发送给某地址的设备的命令的CRC检测错误,则不会执行这条命令,也不会回应

2.Time-out conditions

读写擦除操作的超时时间,一般超时时间是典型时间的10倍,spec中规定了每种操作的超时时间

3.Read ahead in multiple block read operation

为了提高效率,当有多个块读取时,设备可能会超前读取,如果host读取的最后一个物理地址,那么device会出错,因此host要忽略这个错误

2.5 Minimum performance

TODO,参考spec6.9.2

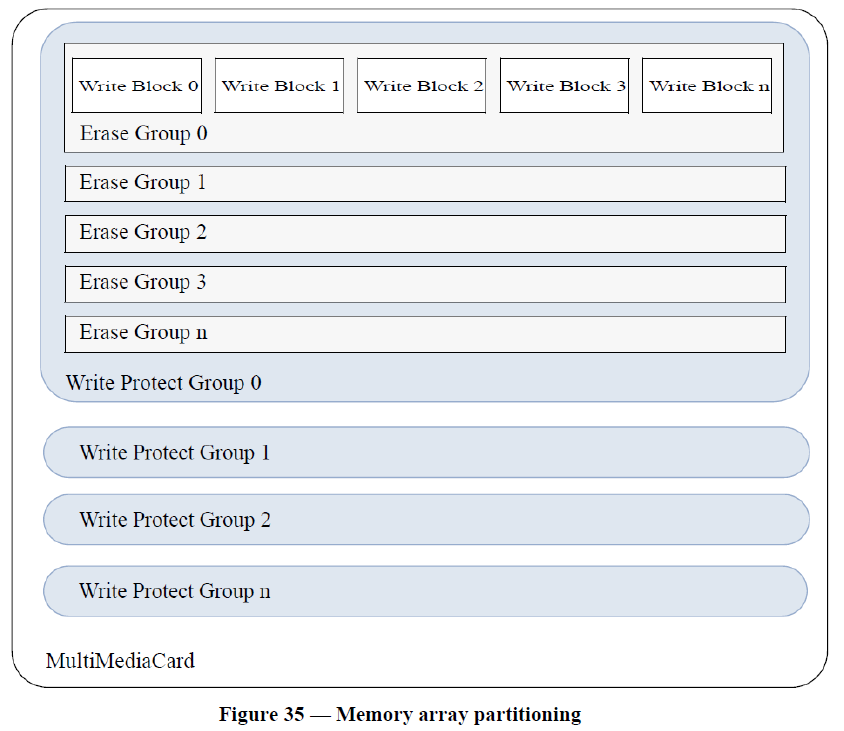

2.6 Memory array partitioning

BYTE:基本的传输单元

BLOCK:面向读写命令的操作单元

GROUP: for erase and WP

2.7 timing

TODO 见 spec 6.15

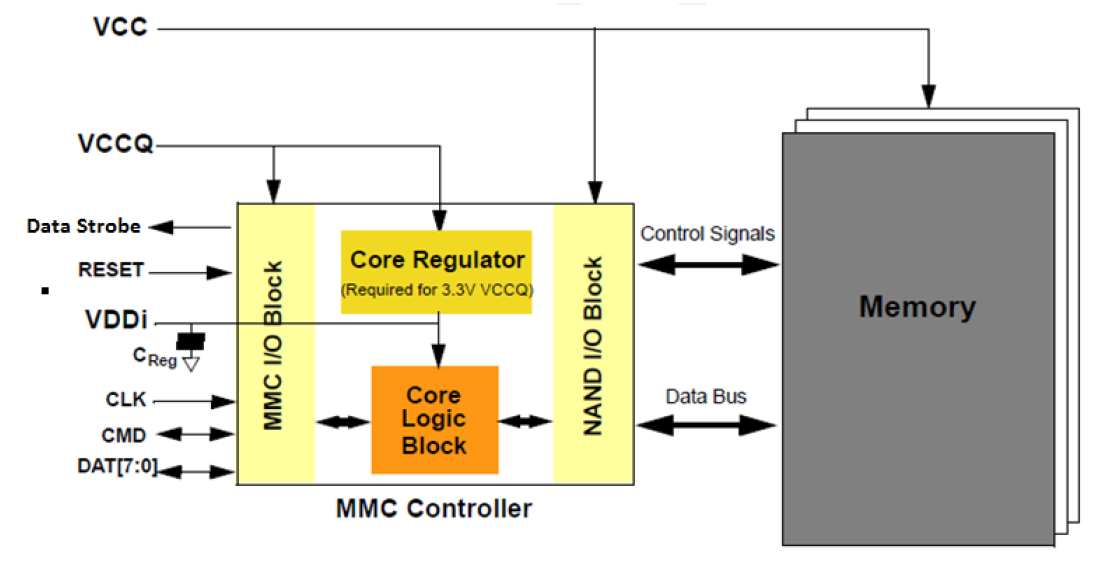

3. device controller

NAND Flash 直接接入 Host 时,Host 端通常需要有 NAND Flash Translation Layer,即 NFTL 或者 NAND Flash 文件系统来做坏块管理、ECC等的功能。

eMMC 则在其内部集成了 Flash Controller,用于完成擦写均衡、坏块管理、ECC校验等功能。

相比于直接将 NAND Flash 接入到 Host 端,eMMC 屏蔽了 NAND Flash 的物理特性,可以减少 Host 端软件的复杂度,让 Host 端专注于上层业务,省去对 NAND Flash 进行特殊的处理。

同时,eMMC 通过使用 Cache、Memory Array 等技术,在读写性能上也比 NAND Flash 要好很多。

图 NAND Flash 与 eMMC

3.1 eMMC操作模式

3.2 device寄存器

图 eMMC寄存器

有三种方式可以对设备reset:

1.断电在上电;

2.reset信号;

3.发送特定命令

4. flash memory

4.1 分区管理

-

BOOT Area Partition 1 & 2

此分区主要是为了支持从 eMMC 启动系统而设计的。

该分区的数据,在 eMMC 上电后,可以通过很简单的协议就可以读取出来。同时,大部分的 SOC 都可以通过 GPIO 或者 FUSE 的配置,让 ROM 代码在上电后,将 eMMC BOOT 分区的内容加载到 SOC 内部的 SRAM 中执行。 -

RPMB Partition

RPMB 是 Replay Protected Memory Block 的简称,它通过 HMAC SHA-256 和 Write Counter 来保证保存在 RPMB 内部的数据不被非法篡改。

在实际应用中,RPMB 分区通常用来保存安全相关的数据,例如指纹数据、安全支付相关的密钥等。 -

General Purpose Partition 1~4

此区域则主要用于存储系统或者用户数据。 General Purpose Partition 在芯片出厂时,通常是不存在的,需要主动进行配置后,才会存在。 -

User Data Area

此区域则主要用于存储系统和用户数据。

User Data Area 通常会进行再分区,例如 Android 系统中,通常在此区域分出 boot、system、userdata 等分区。

更多 eMMC 分区相关的细节,请参考 eMMC基础技术: 分区管理 章节。

浙公网安备 33010602011771号

浙公网安备 33010602011771号