FFT实现——有趣的移位寄存流水线形式

FFT实现——有趣的移位寄存流水线形式 1

一.功能描述:

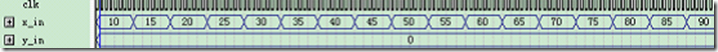

对w(自定义)位(带符号位)数据进行16(易扩展为32点64点128····1024····)FFT计算

可两路w位数据输入

两路w位数据串行输出

使用此方法设计FFT的原因是 ‘FFT算法8点12位硬件实现 (verilog)’中的算法,当点数增加时,资源消耗太大,(而且扩展时,要写好多好多的代码····)

二.设计结构:

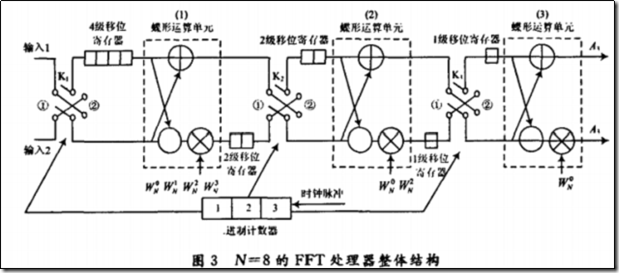

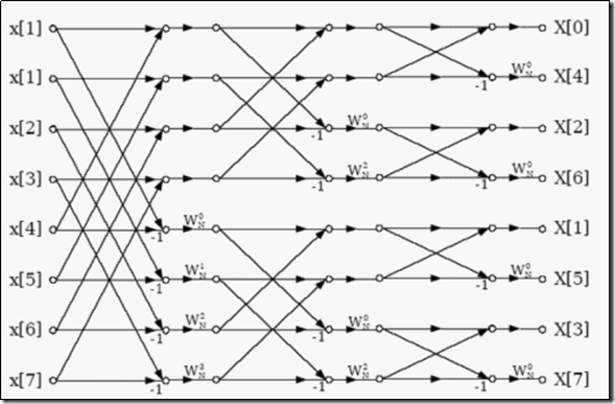

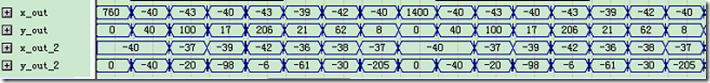

图2.0 以八点FFT为例

图2.1 算法结构

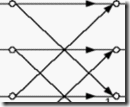

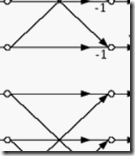

硬件实现概要:每8个clk进2个数据(w位)其实是两路FFT 挑一路来说:数据进来后与此数据之后的第4个数据进行蝶形运算。减法输出要先移位寄存,因为先要进行加法输出的第二级蝶形运算 而第2级的碟型运算也要用移位寄存实现‘交叉’运算 相隔一个数进行一次运算····(表达好混乱····)

相隔一个数进行一次运算····(表达好混乱····)

三.设计模块介绍

按数据流动方向依次介绍

1.数据选择器

图中出现啦三个数据选择器。作用是三个模块的数据连接控制。为此专门设计了一个控制模块。

设计要求即考虑要点

1.由算法结构可见(以左倒右为第1级2,3级)第一级在4个数据后是连续进行4次碟新运算。而第二级, 如图 出现1次不连续的运算,对于连续数据其实是每8个点FFT出现2次不连续情况。 第三极同理,对于连续数据每8点FFT出现4次不连续情况。 凡出现不连续情况就要用数据选择器是数据进行‘跳变’。

出现1次不连续的运算,对于连续数据其实是每8个点FFT出现2次不连续情况。 第三极同理,对于连续数据每8点FFT出现4次不连续情况。 凡出现不连续情况就要用数据选择器是数据进行‘跳变’。

2.要考虑数据选择器间的逻辑运算的时钟个数。(在本设计中为8*4个时钟)

从而确保数据在流水线中逻辑运算正确。(*注意数据的加减顺序,相反的数据选择,可导致相反的加减顺序(a-b成了b-a))

3.从右到左数据选择频率成倍增加。(联想到在累加运算中2进制数每一位的0,1,变化)

4.数据选择器是对蝶形运算输出的数据进行选择 故要与数据对齐 注意每级的数据延时。

KEY1 与 KEY2周期为2clk与4clk过 计算式发生的4clk延时对其无影响 ,有整数个周期。

Angle比key块4个clk 注意angle与输入的数据对齐

2.移位寄存器

设计要求即考虑要点

1.根据算法选择每级的移位数

2.每8个CLK移位一次

3.蝶形运算

设计要求即考虑要点

1.分三个小模块:‘交叉的加减运算’‘ro_cordic’‘除法模块’。(后两个是为了实现旋转因子乘法)(详见‘FFT算法8点12位硬件实现 (verilog)’)

2. 用补码实现减法 注意时钟 流水线实现时每级要保证时间相同

用补码实现减法 注意时钟 流水线实现时每级要保证时间相同

旋转因子的乘法 采用CORDIC 算法来实现 此算法所耗的时间为全流水线的时间单位(即8个clk)。

旋转角度的变化要按一定的规律出现 防止时钟使数据的逻辑顺序错位(如数据在经过第一个W0时在第几个clk后进过第二个W0)。

4.因为使用了CORDIC算法 所以 必须有一个除法模块接在输出上。

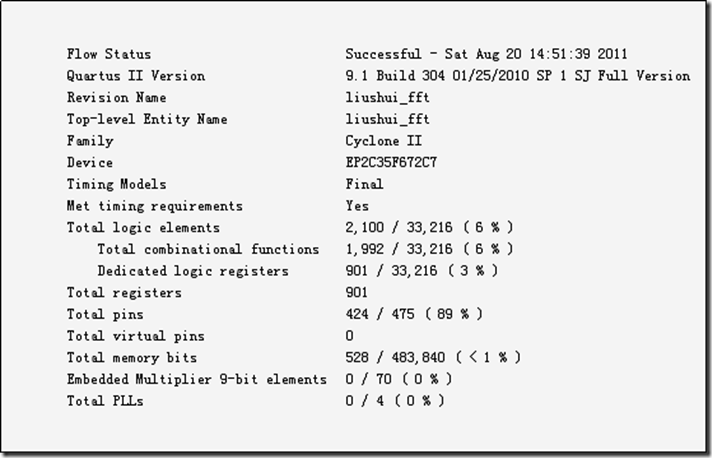

12位 16点FFT资源利用情况 基本上点数每翻一倍LE加500

顺序为:

1

5

3

7

2

6

4

8

9

13

11

15

10

14

12

16

MATLAB结果对比

>> x = [10:5:120];

>> y = fft(x,16)

y =

1.0e+002 *

Columns 1 through 3

7.6000 -0.4000 + 2.0109i -0.4000 + 0.9657i

Columns 4 through 6

-0.4000 + 0.5986i -0.4000 + 0.4000i -0.4000 + 0.2673i

Columns 7 through 9

-0.4000 + 0.1657i -0.4000 + 0.0796i -0.4000

Columns 10 through 12

-0.4000 - 0.0796i -0.4000 - 0.1657i -0.4000 - 0.2673i

Columns 13 through 15

-0.4000 - 0.4000i -0.4000 - 0.5986i -0.4000 - 0.9657i

Column 16

-0.4000 - 2.0109i

其他修改方案记录:

1.在每级加尺度变换 防止溢出 减小量化误差