时序分析 基本术语 摘记 (ALTERA 官方教程)

跟交通系统似的

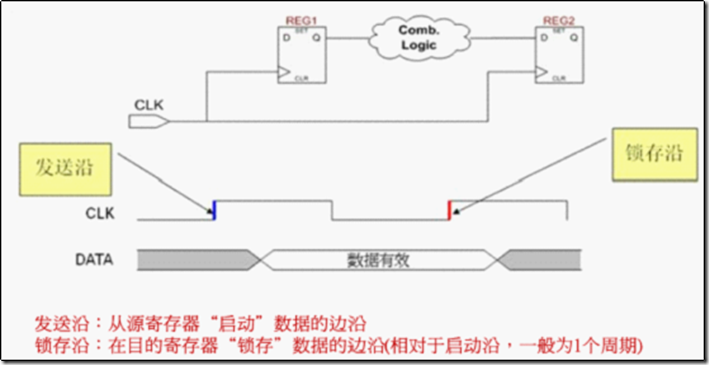

我们将要讨论的所有内容都基于这张原理图。 源寄存器把信号驱动至目的寄存器。 这些寄存器可能都在FPGA设计中,也可能其中一个来自板上FPGA的外部第三方器件。 源寄存器和目的寄存器都由某一时钟源提供时钟,一般是这里显示的同一时钟源,但是,也可以是两个不同的源提供时钟。 对于这样的寄存器至寄存器通路,我们把发送沿定义为激活源寄存器的时钟沿。 锁存沿是激活目的寄存器的时钟沿。 这些时钟沿之间的关系被用于确定寄存器至寄存器的数据传送是否正常。 这些关系来自设计人员输入的时钟约束。 还要注意的是数据有效窗口,两个寄存器之间通路上数据信号有效的时间,在锁存沿之前稳定一些时间,锁存沿之后还要等待一些时间。

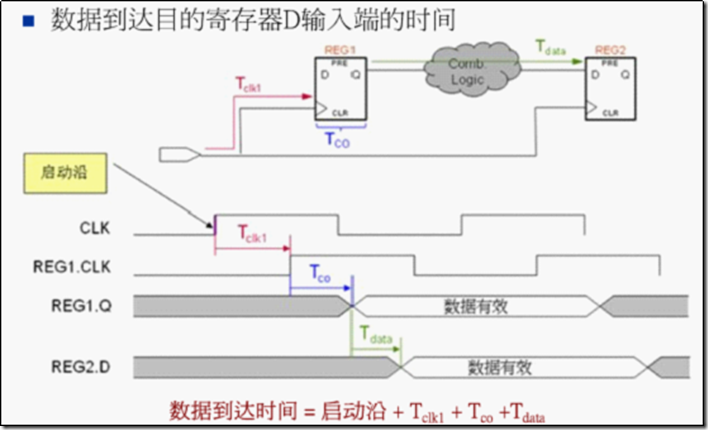

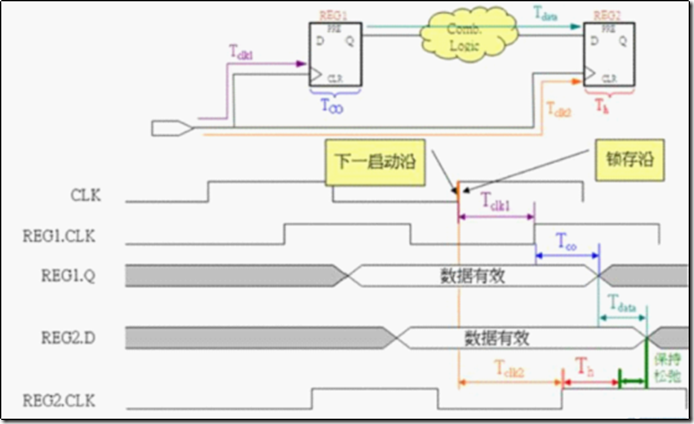

在启动沿基础上,我们定义数据到达时间,时钟发送沿使数据从源寄存器开始发送,最后到达目的寄存器d输入端的时间。 请看图中定义的数据到达通路,计算数据到达时间时需要把以下时间加起来:按照零基准调整后的发送沿延时,源寄存器时钟延时,源寄存器的时钟至输出时间tco,源寄存器和目的寄存器之间的延时。 数据到达时间定义了目的寄存器数据有效窗口的开始,采用这一公式进行计算。

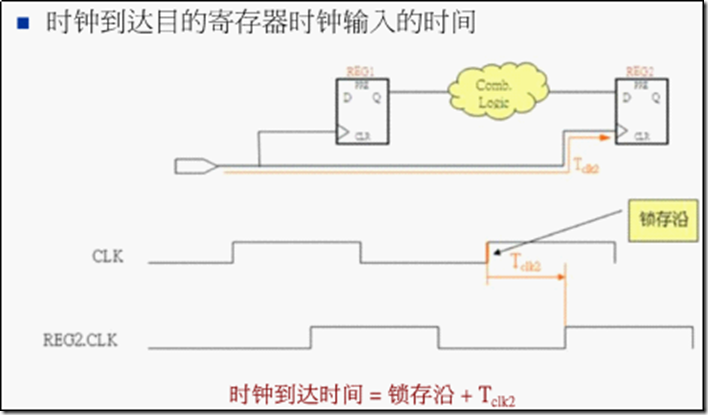

时钟到达时间是锁存沿到达目的寄存器时钟引脚的时间。 它等于按照零基准调整后的锁存沿加上从时钟源到目的寄存器时钟输入之间的延时。 如果源寄存器和目的寄存器在同一时钟域上,那么锁存沿相对于发送沿晚一个周期。 如果时钟来自两个不同的时钟域,将采用发送沿和锁存沿之间实际的时间差

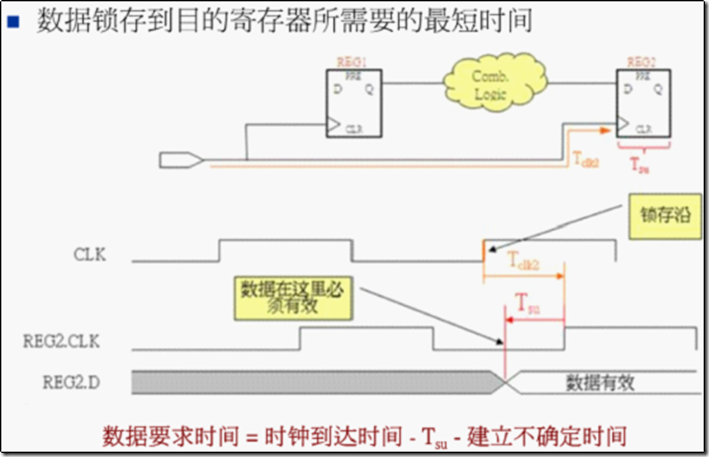

数据要求时间是信号由源寄存器发送,必须到达目的寄存器d输入端的时间,以便进行正确采样。 相对于有效同步传送所需的时间,这一计算保证了数据到达目的寄存器不会太迟。 在锁存沿和时钟到达时间基础上,建立数据要求时间取决于目的寄存器的建立时间,这直接与硬件有关。 在建立时间开始时,数据必须有效。 建立所需的时间等于时钟到达时间减去目的寄存器建立时间t,再减去可选的建立不确定时间。 建立不确定时间含在计算中,有助于定义非理想时钟,支持时钟抖动或者保护带。

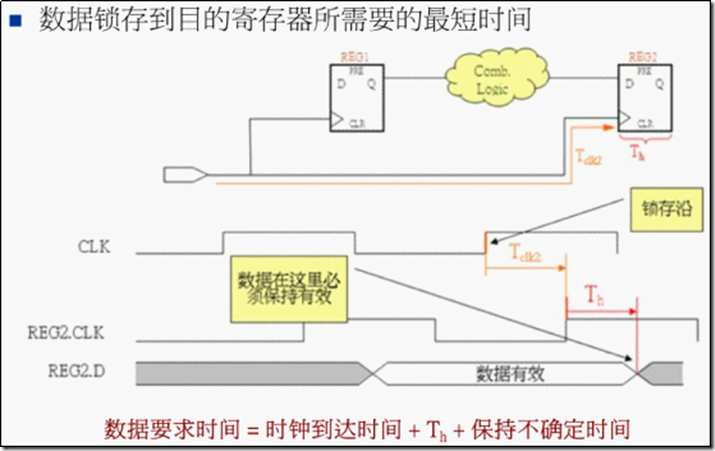

保持数据要求时间是新信号到达目的寄存器d输入最早的时间,并且该数据没有和前一锁存沿采样的数据发生冲突。 相对于有效同步数据传送所需的时间,这一计算保证了新数据不会到达太快。 与建立时间相似,保持时间也取决于实际的硬件。还是基于锁存沿,保持要求时间等于时钟到达时间加上目的寄存器的保持时间要求。 在这一点之前数据必须保持有效,此时新数据能够到达目的寄存器。 与建立不确定时间相似,可以增加可选保持不确定时间。

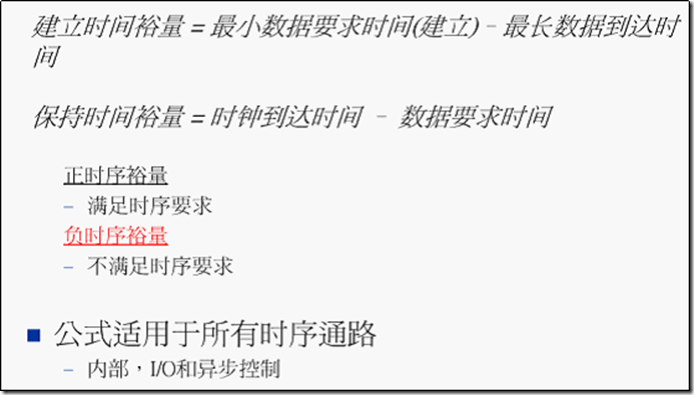

我们在设计中所有通路时序上的最终目标是有正时序裕量。 时序裕量用于衡量设计满足或者不满足时序要求的程度。 为了使电路能够正常工作,裕量计算的结果必须是正的,意味着有额外的余量以满足建立或者保持时序要求。 这样,确定裕量时需要进行两次计算,一次用于建立时间裕量,一次用于保持时间裕量。 通过在图中加入时钟到达、数据到达和数据要求通路,我们可以看到这里显示的建立时间裕量。 建立时间裕量是数据要求时间以及已经定义为数据到达时间的数据有效窗口打开之间的差值。

以相似的方式定义保持时间裕量。 它基于保持数据要求时间,以及数据处理的锁存沿是下一处理操作锁存沿这一事实。 为下一数据处理操作填充数据要求通路以及数据到达通路,我们看到保持时间裕量是下一处理操作数据到达时间和保持数据要求时间之差。有正保持时间裕量还防止了双时钟。 在一个时钟周期期间,与数据同步通过两个连续寄存器级的时钟到达时间相比,数据到达时间较慢时,就会出现“双时钟”。

这里总结了两个松弛公式。在这两种情况下,如果计算值为正,满足时序要求。如果计算值为负,数据通路上的时序失败。我们讨论内部通路、I/O通路或者异步控制信号通路时,会用到这些公式。