efuse

efuse

背景知识

Secure Boot

安全启动Secure Boot,其主要目的是:以限制消费者能力,防止消费者从软硬件层面,对产品的部分关键系统进行读写,调试等高级权限,达到对产品的商业保密,知识产权的保护。

安全启动的安全模型是建立在消费者是攻击者的假设之上,一般常见的操作有:

- 刷机安装自定义的操作系统

- 绕过厂家封闭的支付平台

- 绕过系统保护,复制厂家保护的数字产品。

除此之外呢,有的比较专业的消费者,还可以:

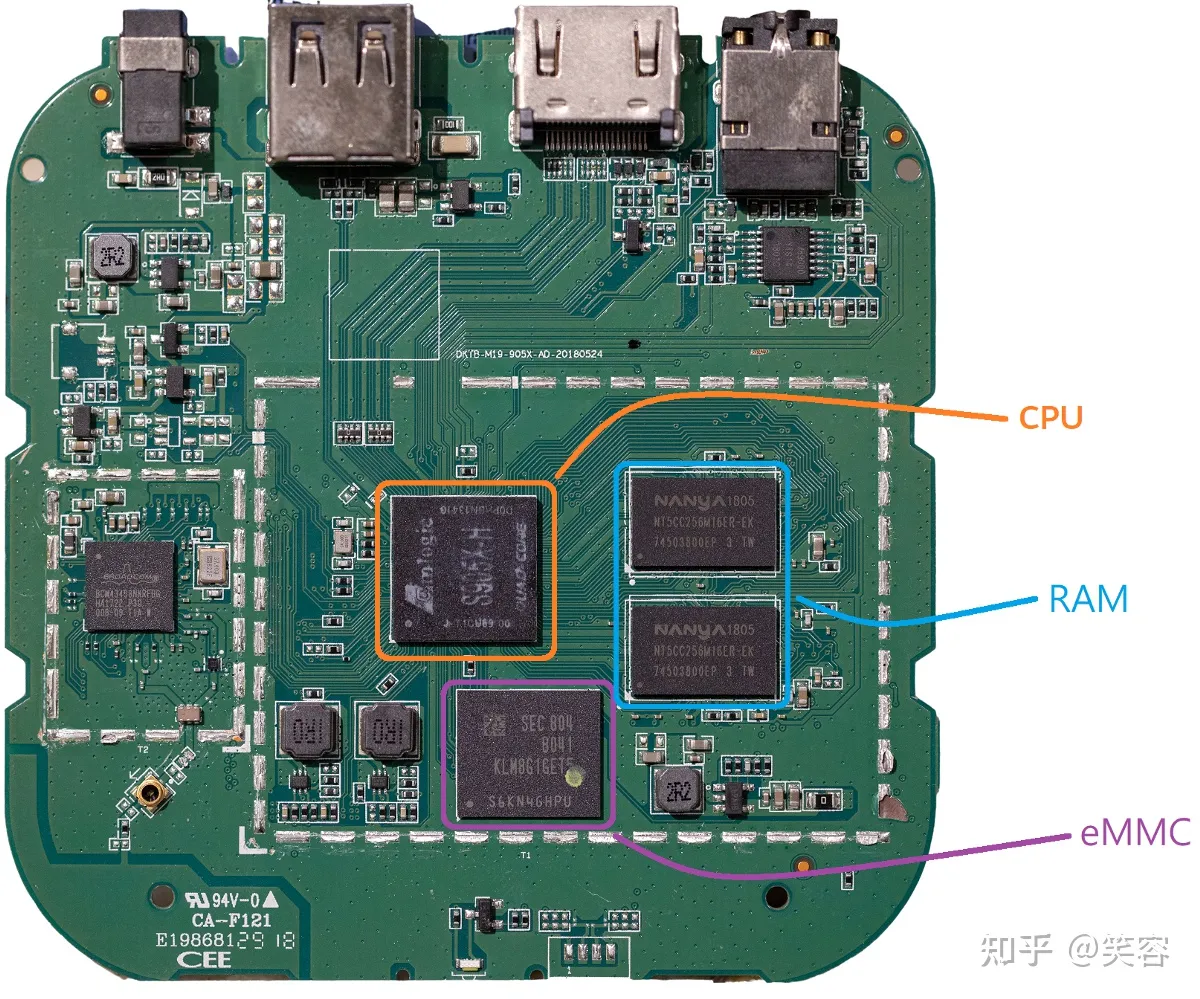

- 使用数字示波器监听

CPU和RAM、eMMC之间的数据传输来读取非常底层的数据传输 - 而且像

eMMC这种芯片通常都是业界标准化的,攻击者甚至可以把芯片拆下来,然后用市面上现成的通用eMMC编程工具来读写上面的内容。

安全启动等级也有一个上限:这个上限通常是认为攻击者不至于能够剥离芯片的封装,然后用电子显微镜等纳米级别精度的显像设备来逆向芯片的内部结构。

简单来说:能成功攻破芯片安全机制的一次性投资成本至少需要在十万美元以上才可以认为是安全的。

CPU内部安全机制

bootROM

BootROM是集成在CPU芯片的一个ROM空间,其主要用于存放一小段可执行程序,出厂的时候被烧录进去写死,不可修改。

CPU在通电之后,执行的第一条程序就在BootROM,用于初始化Secure Boot安全机制,加载Secure Boot Key密钥,从 存储介质中加载并验证 First Stage Bootloader(FSBL);最后跳转进 FSBL 中。

iRAM

为了避免使用外部的RAM,支持Secure Boot的CPU都会内置一块很小的RAM,通常只有 16KB 到 64KB ,我们称之为 iRAM。

这块 iRAM 上的空间非常宝贵,bootROM 一般会用 4KB 的 iRAM 作为它的堆栈。FSBL 也会被直接加载到 iRAM 上执行。

efuse

如上面所述,在Secure Boot中存放的是根密钥,用于安全启动的验证。

- 一般有两种根密钥:一个是加密解密用的对称密钥 Secure Boot Key,一般是 AES 128 的,每台设备都是随机生成不一样的;

- 另一个是一个 Secure Boot Signing Key 公钥,一般用的 RSA 或 ECC,这个是每个

OEM自己生成的,每台设备用的都一样,有些芯片会存公钥的Hash来减少eFUSE的空间使用。

Security Engine

有些 CPU 中还会有一个专门负责加密解密的模块,我们称为 Security Engine。这个模块通常会有若干个密钥槽(Keyslots),可以通过寄存器将密钥加载到任意一个 Keyslot 当中,通过寄存器操作 DMA 读写,可以使用 Keyslot 中的密钥对数据进行加密、解密、签名、HMAC、随机数生成等操作.

First Stage Bootloader(FSBL)

FSBL 的作用是初始化 PCB 板上的其他硬件设备,给外部 RAM 映射内存空间,从 外部存储介质中加载验证并执行接下来的启动程序。

根信任建立

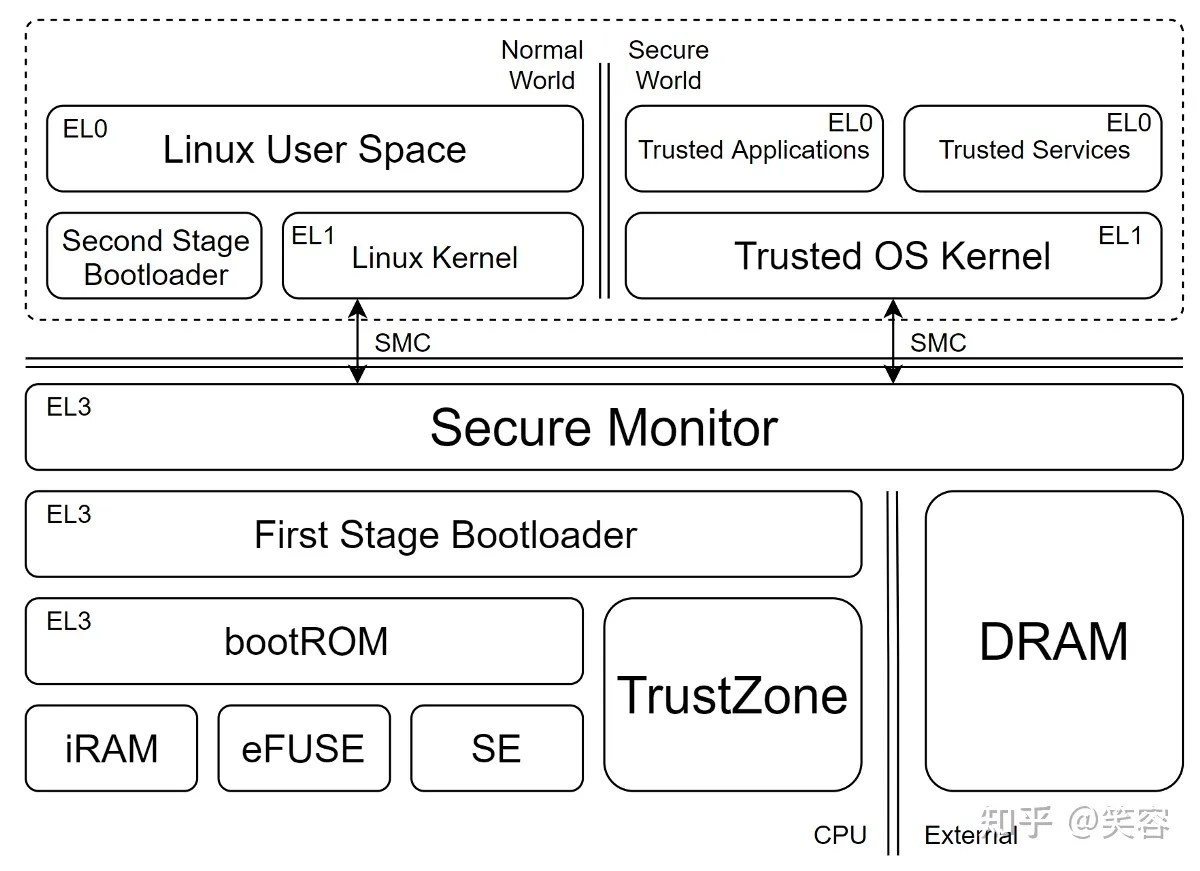

CPU上电后执行Boot ROM的程序,其这一小段程序用于初始化RAM,并加载Efuse上的内容,判断其所处的运行模式是不是生产模式。- 如果在生产模式,开启

Secure Boot功能,把Efuse上保存的Secure Boot Key加载到Security Engine加密模块中处理。 - 从外部存储介质中加载

FSBL,FSBL里面会有一个数字签名和公钥证书,bootROM 会验证这个签名的合法性,以及根证书的Hash是否和eFUSE中的Signing Key的Hash相同。 - 如果验证通过,说明

FSBL的的确确是OEM正式发布的,没有受到过篡改。 - 然后

bootROM就会跳转到FSBL执行接下来的启动程序。

NVM

非易失性存储器(NVM,Non-Volatile Memory)

PROM & OTP

PROM

PROM, Programmable read-only memory, 是ROM 的一种,相较于传统ROM, 其数据不是在制造过程中写入的,而是在制造完成之后通过『 PROM programmer 』写入的。PROM 中的每个bit 由熔丝 ( fuse ) 或反熔丝 ( antifuse ) 锁定,根据采用的技术不同,可以在晶圆、测试或系统级进行编程。

典型的PROM 出厂后所有比特的值都是"1", 所谓的编程就是熔断对应比特将其值改写成"0", 这样的改写只能做一次。

熔断过程:通过在薄氧化物晶体管的栅极跟衬底之间施加一个高压脉冲,来熔断栅极跟衬底间的栅氧,如2nm 厚的栅氧需要大概6V 电压。晶体管栅极上的正向电压在栅极和衬底间形成一个反向通道,使隧穿电流通过栅氧,并在栅氧中产生更多电子陷阱,从而增加通过栅氧的电流,并最终使栅氧熔化并形成从栅极到衬底的导电沟道。形成导电通道所需的电流约为100 µA / 100 nm2,击穿发生的时间约为100 µs 或更短 。

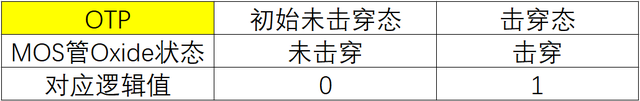

OTP

OTP, One time programmable, 是一种特殊类型的非易失性存储器 ( non-volatile memory ),只允许编程一次,一旦被编程,数据永久有效。

OTP(One Time Programmable)是反熔丝的一种器件,就是说,当OTP存储单元未击穿时,它的逻辑状态为0;当击穿时,它的逻辑状态为1,也属于一次性可编程存储器。它的物理状态和逻辑状态正好和

eFuse相反!

OTP和efuse的区别:

- 从成本上讲,

eFuse器件基本上是各个Foundry厂自己提供,因此通常意味着免费或者很少的费用,而OTP器件则通常是第三方IP厂家提供,这就要收费。 - 从器件面积上讲,eFuse的cell的面积更大,所以仅仅有小容量的器件可以考虑。当然如果需要大容量的,也可以多个eFuse Macro拼接,但是这意味着芯片面积的增加,成本也会增加;OTP的cell面积很小,所有相对来讲,可以提供更大容量的Macro可供使用。

OTP比eFuse安全性更好,eFuse的编程位可以通过电子显微镜看到,因此其存储的内容可以被轻易破解,但OTP在显微镜下无法区分编程位和未编程位,因此无法读取数据。eFuse默认导通,存储的是"1",而OTP默认是断开,存储的是"0",因此OTP的功耗也较eFuse小,面积也较eFuse小。

相较于MTP (multi-time programmable ) 如EEPROM, OTP 的面积更小而且不需要额外的制造步骤,因此广泛应用于low-cost 芯片中,OTP 常用于存储可靠且可重复读取的数据,如:启动程序、加密密钥、模拟器件配置参数等。

memory 结构

Memory Hierarchy - 存储器层次结构_memory结构

[memory学习_memory 结构](https://blog.csdn.net/te55gybo/article/details/118499919#:~:text=存储器内部结构一般由存储阵列,地址译码器和输出控制电路组成。 我们把存储阵列以外的电路都称为外围电路(Periphery)。,存储阵列是memory的核心区域,它有许多存储单元组成,每个存储单元存放一位二值数据。 每次读出一组数据,称为一组字。)

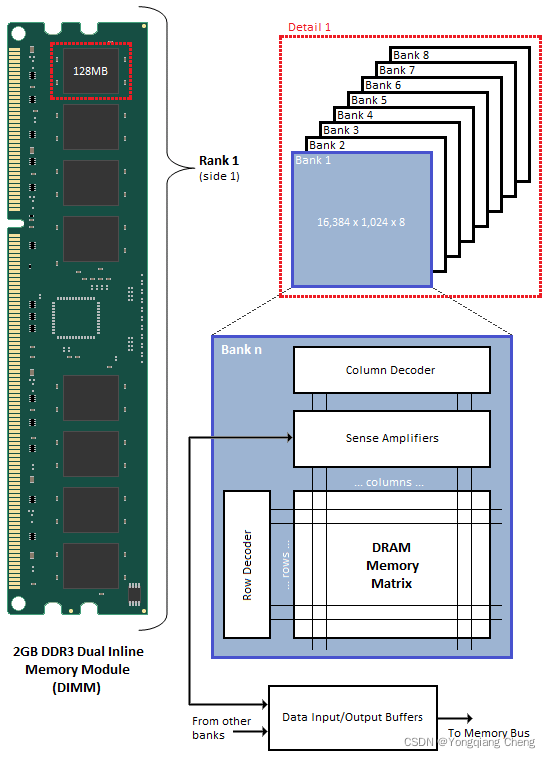

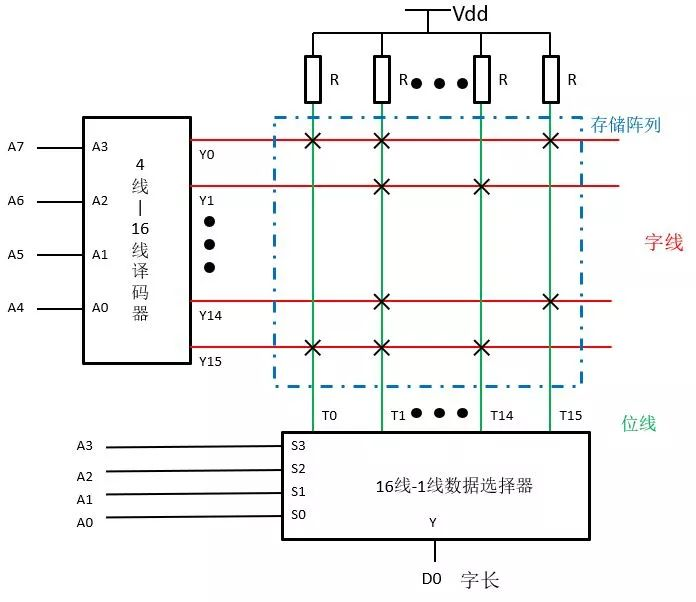

存储器内部结构一般由存储阵列,地址译码器和输出控制电路组成。我们把存储阵列以外的电路都称为外围电路(Periphery)。

存储阵列是memory的核心区域,它有许多存储单元组成,每个存储单元存放一位二值数据。每次读出一组数据,称为一组字。一个字中所含的位数称为字长(Bit)。为了区别各个不同的字,给每个字赋予一个编号,称为地址,由译码器将地址代码转译。地址单元个数就是字数(Depth),用N表示,数值为2n次方,n为地址码的位数。

实际运用中,我们经常以字数(Depth)和字长(Bit)的乘积来表示存储器的容量。如下图中的ROM容量为28 X 1,有256个字,字长为1位,总共256个存储单元。容量越大,意味着能存储的数据越多。

通常,大家还会看到类型HD,HC,HP等缩写,这些都是表征不同类型Bitcell和外围电路(Periphery)组成的。

HD:High Density Bitcell ,面积较小

HC:High Current Bitcell 高工作电流,access time较小

HP:High Performance Periphery ,速度快

LP:Low-Power Periphery ,功耗较小

ULP:Ultra-Low Power Periphery,超低功耗

ULL:Ultra-Low Leakage Periphery,超低漏电流

memory repair

通常,设计Soc时,如果存储器的容量比较大,那么存储器在生产时出现坏点的概率就会增加,也就是说某个地址可能用不了。为了防止因为一个坏点就导致整个IC不能用,一般会选择在存储器内设置row redundancy或者column redundancy。

什么是soft repair 和 hard repair?_memory hard repair

什么是repair?

Repair是一个过程,是存储器修复缺陷(信号线短路、断路等情况)的过程。

存储器中一般存在冗余的信号线和单元,通过检查发现有问题的单元,从而用冗余的模块替换有缺陷的模块,保证存储的正常使用。

Lane repair 一般存在于芯片上电的初始化流程中。Lane repair过程用来修复两个模块之间的连线,模块在设计的时候是有冗余的连线的。用冗余的连线替换有问题的连线就是Lane repair 过程。

Lane repair 又分为hard lane repair 和 soft lane repair。Hard lane repair 通过读取出厂时写入到efuse中的固定数据来完成通道修复。soft lane repair 通过自身的硬件检测哪条信号有问题来完成通道修复。

在上电初始化过程中,hard lanerepair 在前,soft lane repair。

芯片在使用的过程中,会不断老化,某些信号通道会出现不稳定,速度降低等问题,hard lane repair只能解决出厂时存在的缺陷,而不能修复使用过程中出现的通道问题。每次芯片上电时,都会启动soft lane repair,修复此刻发现的问题,采用冗余的信号线替换已经不满足需求的信号线。

hardrepair

什么是hardrepair?

Hard repair 同样处于芯片初始化流程中,在存储模块出厂前厂家会进行功能测试,发现有问题的模块和信号线后会生成相应的数据data0,并且将data0烧入到存储模块中,芯片初始化流程中,存储模块会将data0读取到相应的寄存器中repair_register,从而实现用冗余模块替换问题模块,保证存储功能正常。出厂后data0的数据就是固定不变的,这就是hard repair过程。

softrepair

什么是softrepair?

但是芯片在使用过程中,随着时间推移,存储内部在不断老化,有些存储单元出问题了,有些输入输出线出问题了,此时我们也希望存储能够自动修复,此时就需要soft repair了。soft repair同样处于芯片初始化流程中,但是在soft repair完成之后,存储模块中会存在相应的硬件电路判断模块是否有新缺陷,如果有缺陷,则产生相应的数据data1,data1传送给修复寄存器(repair_register不止一个),从而实现用冗余模块替换问题模块,保证存储功能正常。

hard repair与soft repair的区别?

芯片上电后,都会依次经历hard repair和soft repair。

Hard repair 中的数据时出厂就固定的,而soft repair的数据是每次上电后初始化流程中,存储模块自己检测产生的。

Hardrepair 只能修复出厂时的硬件缺陷,而soft repair 能够修复芯片使用过程中产生缺陷。

例子:

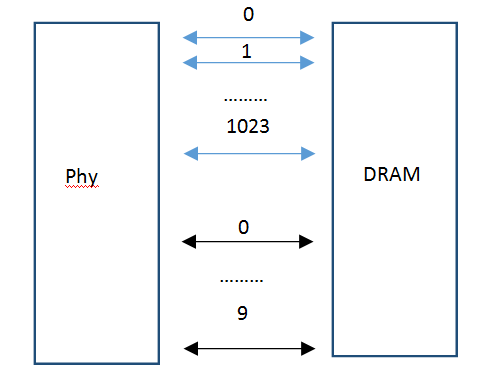

如图所示,存储DRAM和PHY模块间有1024根有效数据线和10冗余信号线。出厂时,检测发现有2根有效信号线有问题(短路,断路,传输速率不达标),此时产生修复数据data0,烧入到DRAM中,芯片上电后,hard lane repair 开始,将data0读取到修复配置寄存器中,使用冗余信号线中的两条替换有问题的两根信号线,这就是hard lane repair。

Hard lane repair 完成后,会进入soft lane repair,此时存储芯片DRAM依靠内部的硬件检测电路检测到有5根信号线有问题,此时产生修复数据data1,将data1写到修复配置寄存器,使用冗余信号线中的5条替换有问题的5根信号线。

macro

理解下 efuse macro

概述

efuse是什么?

之所以成为eFuse,因为其原理像电子保险丝一样。

efuse只能从0到1。主要功能是存一些不想被别人修改的数据(如密钥,出厂信息等等),其次是冗余修复。

eFuse的全称是“电子熔断器”(electronic fuse),是一种可编程电子保险丝,是一种用于存储信息和保护芯片的非易失性存储器件( ( non-volatile memory ))。它的原理是基于电子注入和热效应。在eFuse中,短电流脉冲被应用于热致电子发射,这会使电流通过一个非常小的导线。该电流会引起电线中的材料熔断,形成一个永久性的开路。这个过程是不可逆的,一旦eFuse被熔断,就不能再次编程。

Efuse是一次性可编程存储器(One time programmable),在芯片出场之前会被写入信息,在一个芯片中,efuse的容量通常很小,一些芯片efuse只有128bit。

2004 年IBM 发明了eFuse, 不同于之前的可编程ROM, eFuse 不需要『体外编程器』,它利用EM ( electromigration ) 效应来实现『熔断』。eFuse 的发明可谓是革命性的,它不依赖于工艺,不需要新材料,不需要新工具,它结合了独特的软件算法和新的熔丝技术,根据条件的改变和系统需求动态调整和适应自身行为,在无需人工干预的情况下,可以监测并调整芯片的功能,以提高其质量、性能和功耗。最初因为『被编程』能力有限,eFuse 使用受限,但当与内建自测试 ( BIST ) 结合之后,它开始大放异彩。可以认真读一下当年IBM 的新闻稿。

由于SOC可能会支持不同的启动方式,如xip启动可以直接从外部的norflash开始启动。因此在rom中集成bootrom镜像之后,还需要保证芯片每次启动时都必须从bootrom开始执行,否则攻击者还可以通过xip方式绕过整个secureboot流程。而一般xip启动模式都是在调试阶段用于问题定位的,因此在产品调试完成,启动secureboot前必须要关闭该模式。通常它可以通过OTP或EFUSE中的特定bit实现。

字段中的任何eFuse位都只能从0编程为1(融合),但是读取操作没有限制。OTP在安全中的应用一般可以存放一些固定不变的值,比如:

- 每个设备唯一的根密钥(Master Key)

- 设备唯一ID(Device Unique ID)或者MAC 地址

- 一些安全配置或者秘密值(软件的Hash值,启动模式等)

以上链接讲了efuse和secure boot的关系。

芯片第一次 boot 时,软件 bootloader 根据以下步骤使能 Secure boot:

...

bootloader通过烧写 efuse 中的 ABS_DONE_0 永久使能 secure boot。

...

浅析安全启动(Secure Boot)附带EFUSE解析_efuse介绍及安全启动浅析

一般 eFUSE 的大小在 1KB 左右,OEM 从 CPU 厂家购买了芯片,组装了产品后,一般都要焼写 eFUSE 的内容,包括产品的运行模式:测试、开发、生产等。面向终端消费者的产品都会被焼写为生产模式。这个模式下 bootROM 会禁用很多权限,更大面积地限制用户的能力。

另外一个很重要的焼写内容就是根密钥了,一般有两种根密钥:一个是加密解密用的对称密钥 Secure Boot Key,一般是 AES 128 的,每台设备都是随机生成不一样的;另一个是一个 Secure Boot Signing Key 公钥,一般用的 RSA 或 ECC,这个是每个 OEM 自己生成的,每台设备用的都一样,有些芯片会存公钥的 Hash 来减少 eFUSE 的空间使用。

只有 Secure World(后面会介绍)才能访问 eFUSE 的寄存器。除了读写 eFUSE 的基础寄存器之外,还有一些控制寄存器可以禁止别的程序访问 eFUSE,来保护其中的密钥。因此 eFUSE 中的根密钥以及 bootROM 将作为 Secure Boot 的根信任。

efuse的作用及应用场景

eFuse可以被用于多个应用场景,例如芯片保护、电源管理、电路校准等。

在芯片保护方面,eFuse可以用于防止电路被过电压或过电流损坏,也可用于防篡改、防破解等;

在电源管理方面,eFuse可以用于控制电流和电压,确保电路正常工作;

在电路校准方面,eFuse可以用于校准电路参数,例如时钟频率和电流偏置等。

总的来说eFuse的优点是体积小、功耗低、可编程性强、可靠性高、不易被擦除等,因此在集成电路中得到了广泛应用。

Efuse还可用于存储MEM repair的存储修复数据

也可用于存储芯片的关键信息:如芯片可使用电源电压,关键时钟频率,芯片的版本号,生产日期。在厂家生产好die后,会进行测试,将芯片的信息写到efuse中去。

eFuse 应用范围很广,从模拟器件的调整、校准、修复到系统软件的现场更新,且被广泛应用于安全领域,但由于eFuse 的『编程结点』可以通过电子显微镜看到,因此其存储的内容可以被轻易破解。

传统eFuse 的熔丝由多晶硅栅极层制成, 随着工艺几何尺寸的缩小和High-K 材料的使用,现在eFuse 的熔丝改由金属制成,随着时间的流逝,编程期间产生的『熔丝碎屑』会反向生长,这限制了eFuse 的可读次数。eFuse 的形状类似于领结,中心是一条窄金属条,较大的端头用作通孔和散热器的连接,受限于该形状,随着晶体管尺寸的减小,eFuse 的尺寸不能按比例减小,因此随着Macro 尺寸变大,eFuse 的密度并不能同比例增加,很少会超过4KB.

顺应安全性和密度的需求,Antifuse 诞生。

简单就 eFuse功能 作以总结介绍,具体如下文:

(1)Efuse被广泛利用最重要的一个原因就是能够对有缺陷的芯片进行修复,而且在修复的过程当中不需要外界的干预。对于芯片的生产以及考虑到生产的成本,最重要的一点就是芯片生产的良率,若生产出有缺陷的芯片,而又不能修复。那处理的结果就只能是报废,这样的处理方式在很大程度上增加芯片的成本。Efuse技术的出现,即通过改变电路的某些电压,或者特意去关闭一些功能模块,这样即使芯片出现缺陷,但是依旧能去实现芯片要实现的某些功能。这样即使有生产出来的芯片有缺陷,通过Efuse技术去发现错误,并且对错误进行修复,这样一来芯片还是可以正常使用,所以Efuse技术在提高芯片的良率以及降低芯片的成本上有很大的贡献。另一方面,通过找到芯片易出错的地方,有助于以后芯片的改进,以前的熔丝都是单排的,只能进行一次的编程,而随着工艺的改进,现在Efuse采用的都是多排阵列,这就实现了Efuse的自我修复。

(2)利用Efuse可以降低芯片的功耗以及增加芯片的可控性,由于Efuse可以进行编程,从而可以实现芯片关闭某些工作模块,当我们不需要某些模块时可以利用Efuse的编程来限制或者是屏蔽某些功能,从而可以降低芯片的功耗,也能进一步增加芯片的可控性。

(3)可提高芯片的安全性,利用Efuse技术,密码随时都可以进行修改,能有效的降低黑客的入侵。

(4)Efuse技术还可以降低制造的成本。在第一个功能应用中我们通过对芯片的修复,能减小芯片的报废而降低一部分成本,另外一个降低成本是通过芯片的集成多种不同的应用功能模块,当客户选择不同的功能时,不需要重新设计与制造,只需要通过Efuse技术来选择功能模块。这就在另一个层面来达到降低成本的效果。

(5)随着工艺的更微小化,Efuse利用电位迁移的技术,不仅不会对周边的电路造成破坏,而且还能对在封装后的芯片进行编程,这使得Efuse在芯片中的应用更为广泛。

(6)类似启动程序、加密密钥、模拟器件配置参数等。可通过efuse 控制着系统启动方式。模拟电路受工艺制造等误差的影响,流片回来的芯片往往需要对作参数校准,调试完成后将确定的值烧写到OTP中,芯片上电后OTP的值被装载到寄存器中,模拟电路参数完成校准。通过运用eFuse技术,允许计算机芯片的动态实时重新编程。Efuse可用于存储MEM repair的存储修复数据,也可用于保存芯片量产信息,以便后续追踪,如芯片可使用电源电压,芯片的版本号,生产日期。

Efuse对于芯片而言就像一个指挥官,它能够控制芯片中很多信号的的传输或者将其停止,这样就使得芯片中的其他电路能够更快的运转,Efuse不仅再一次的拯救芯片,还能提高芯片的效率。

Antifuse

efuse是如何使用的

在芯片出厂之前Efuse会被写入信息,efuse的容量通常不会很大,一些芯片efuse只有128bit,也存在部分芯片efuse容量超过1Kbit的,主要看芯片需求。

如下所示128bit的efuse包含芯片电压字段、芯片版本号、芯片生产日期以及其他信息。

芯片在初次上电过程中会读取efuse中的电压字段数值,送到芯片外部的电源管理器,电源管理器在芯片初始上电前会提供一个标准的电压(假设为1.0v),在接受到efuse中的电压字段数值后会调节电压大小。如果芯片质量较好,电源管理器会将电源电压调节到较低值(0.8v),假设芯片质量一般,电压管理器将电源电压调节到稍高值(0.85v)。

完成电源电压调整后,芯片会重新进行上电复位操作。

以上链接介绍了efuse实际芯片的外围电路及芯片功能

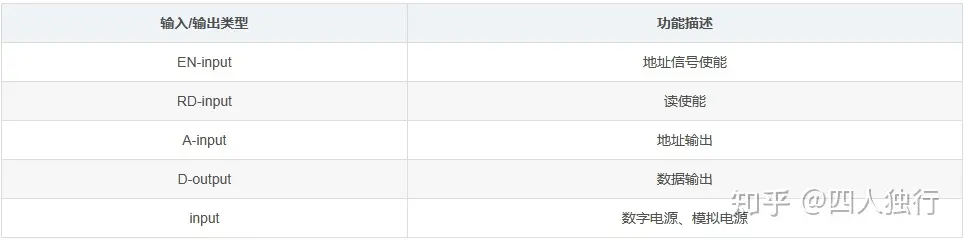

efuse的工作模式

相关信号

eFuse操作模式

eFuse宏有三种操作模式,具体如下:

(1)编程模式(Program mode)、

(2)读取模式(Read mode)、

(3)非活动模式(Inactive mode)。

eFuse模块三种模式选择由其读选择信息(RDEN)和程序选择(PGMEN)的逻辑电平共同决定。

工作模式:

Mode 编程使能

PGMEN 读取使能

RDEN 模拟电源

注意事项:

(1) 编程使能和读使能不允许同时为H。

(2) 除了在编程模式或读取模式下,不允许地址输入高电平,也就是说只有在编程或读取模式下才允许AEN为高电平。

(3) 在编程模式或读取模式下,当AEN为高电平时,不允许端口(地址)切换。

(4) 既不允许读取模式直接转换到编程模式,也不允许PGM模式直接转换到读取模式。

编程模式(Program Mode)

在燃烧前,初始Fuse输出为“0”,燃烧后写入“1”。当编程模式(读使能RDEN=L,编程使能PGMEN=H)时,由地址A[11:0](地址输入位)指定的EFUSE位将被AEN(地址使能位)的高脉冲烧毁。程序模式的详细时序见详解。D[7:0]在程序模式下未定义。

注意:一根Fuse只能烧一次。

读取模式(Read Mode)

如果RDEN=H,PGMEN=L,则EFUSE进入读取模式。读取模式的详细时序间详解。地址信号A[11]~A[9]为“无效”。4K = (4*1024) byte = 4096byte

2^9 = 512 组织成512×8位的一次性可编程非易失性电熔丝存储单元。其中A[11:0]为地址输入,A[0]A[8]是有效单元,D[0]D[7]是读取模式下的并行数据输出。

非活动模式(Inactivate Mode)

如果编程模式和读取模式都不活动,则EFUSE进入非活动模式。非活动模式下的首选待机条件为AEN = L,RDEN = L,PGMEN=L,D[7:0]在非活动模式下未定义。

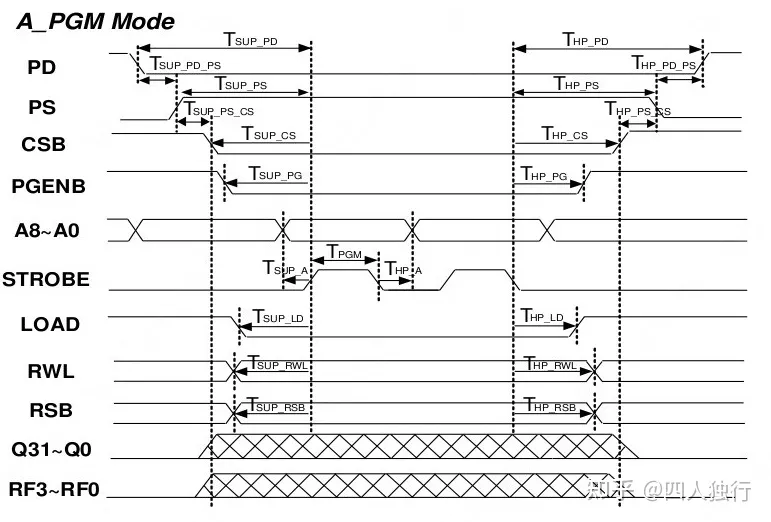

Efuse设计思路

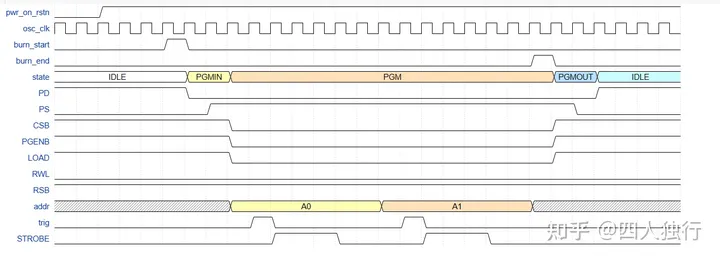

以烧录模式为例,时序图如下:

我们一般会在机台进行烧录,使用的接口可以是JTAG转APB,也可能是不太常用的SPI转APB或UARTM转APB,这三种接口都有一个缺点,就是配置delay比较长,所以说就堵死了我们只靠软件来进行配置的路。

包括中兴,华为等大公司采用的都是软硬件结合的方法来进行烧录,时序如下图:

burn_start进入烧录状态,PGMIN中包含对PD,PS,CSB,PGENB等信号的控制,以满足efuse接口时序的setup和hold时间,进入真正的PGM状态后,配置一次ADDR,发起一次triger,来保证ADDR和strobe的时序关系。最后烧录完成,发起burn_end进入退出时序,以便进行二次烧录。

当然还有更快的设计方法,就是ADDR提前写入软件寄存器,bit[x]=1代表这个地址需要被熔断,然后只需要一次triger就可以完成所有烧录,两者区别不大,因为机台对这点时间无感。

同样的read时序也可以参考pgm时序,软硬件结合(利用counter)来满足模块的setup和hold时序要求。

浙公网安备 33010602011771号

浙公网安备 33010602011771号