4. FSM

verlog

(非)阻塞赋值

阻塞赋值

阻塞赋值属于顺序执行,即下一条语句执行前,当前语句一定会执行完毕。

阻塞赋值语句使用等号 = 作为赋值符。

前面的仿真中,initial 里面的赋值语句都是用的阻塞赋值。

非阻塞赋值

非阻塞赋值属于并行执行语句,即下一条语句的执行和当前语句的执行是同时进行的,它不会阻塞位于同一个语句块中后面语句的执行。

非阻塞赋值语句使用小于等于号 <= 作为赋值符。

FSM

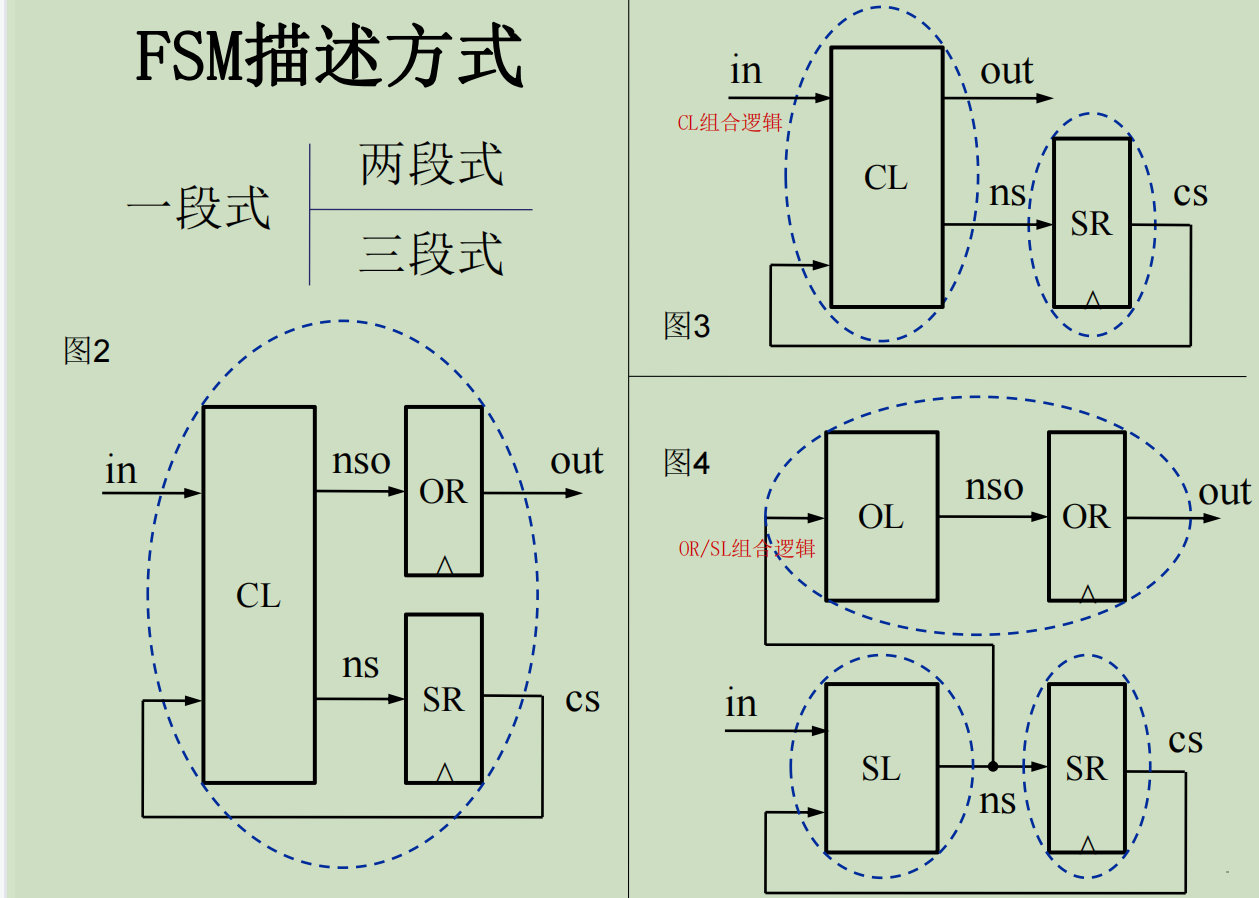

两段式

时序逻辑:cs=ns;缩减版激励方程

组合逻辑:out=f(cs)|穆尔型|f(A,cs)|米利型|为输出方程;ns=f(A,cs)为转化方程

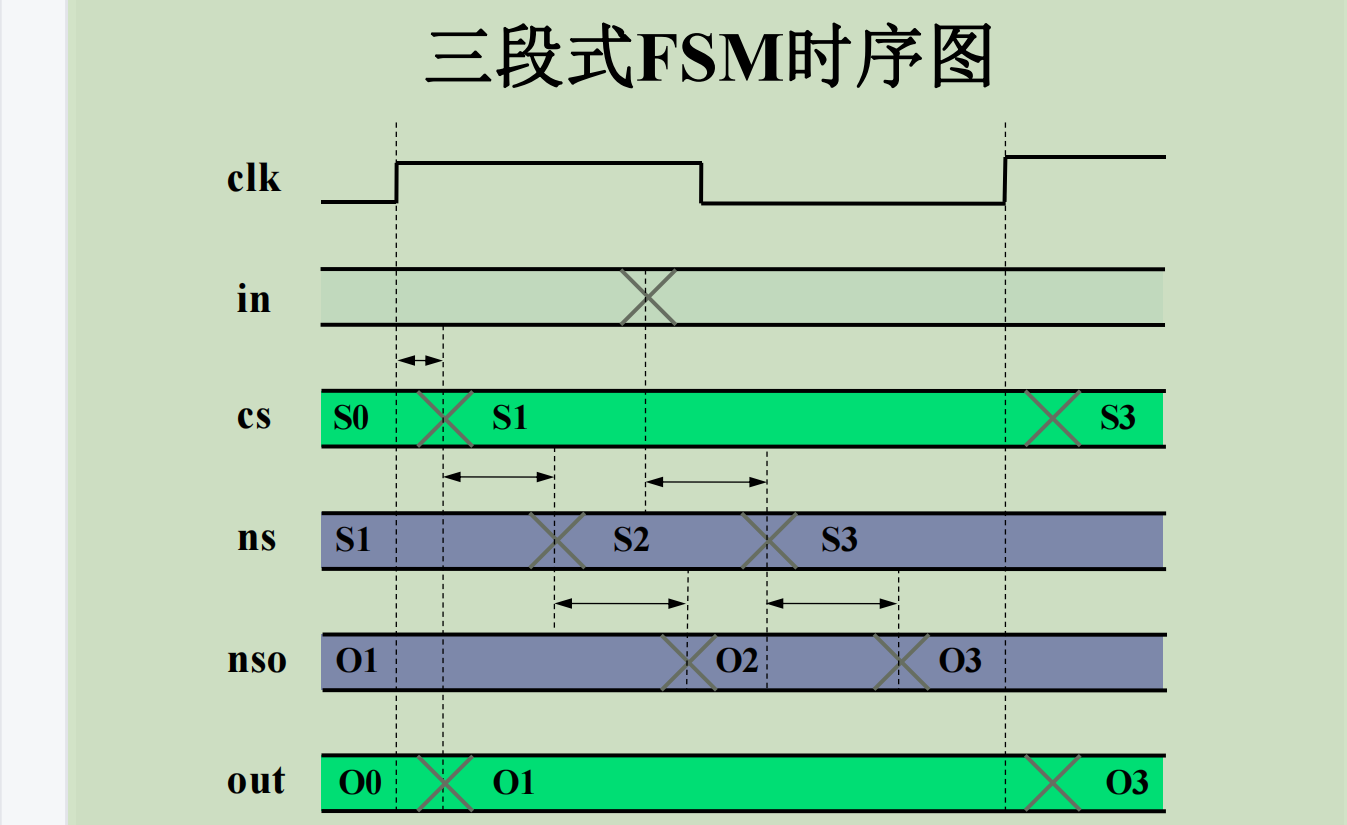

三段式——只能为摩尔型

out=f(ns)=f(cs),只能为摩尔型

关于integer

module top_module(

input [99:0] in,

output [99:0] out

);

always @(*) begin

for(integer i= 0;i < 100 ; i++)begin

out[i] = in[99-i];

end

end

endmodule

//integer也可以直接赋值给reg

for(i=1;i<=7;i=i+1) begin

#5 data_in=i;end

end

愿偿少年泪,犹趁未老时!

本文来自博客园,作者:clfire,转载请注明原文链接:https://www.cnblogs.com/sky1water/p/16786941.html