3. 时序逻辑——锁存与触发

疑问;

- 触发器在时序逻辑的哪一步被应用

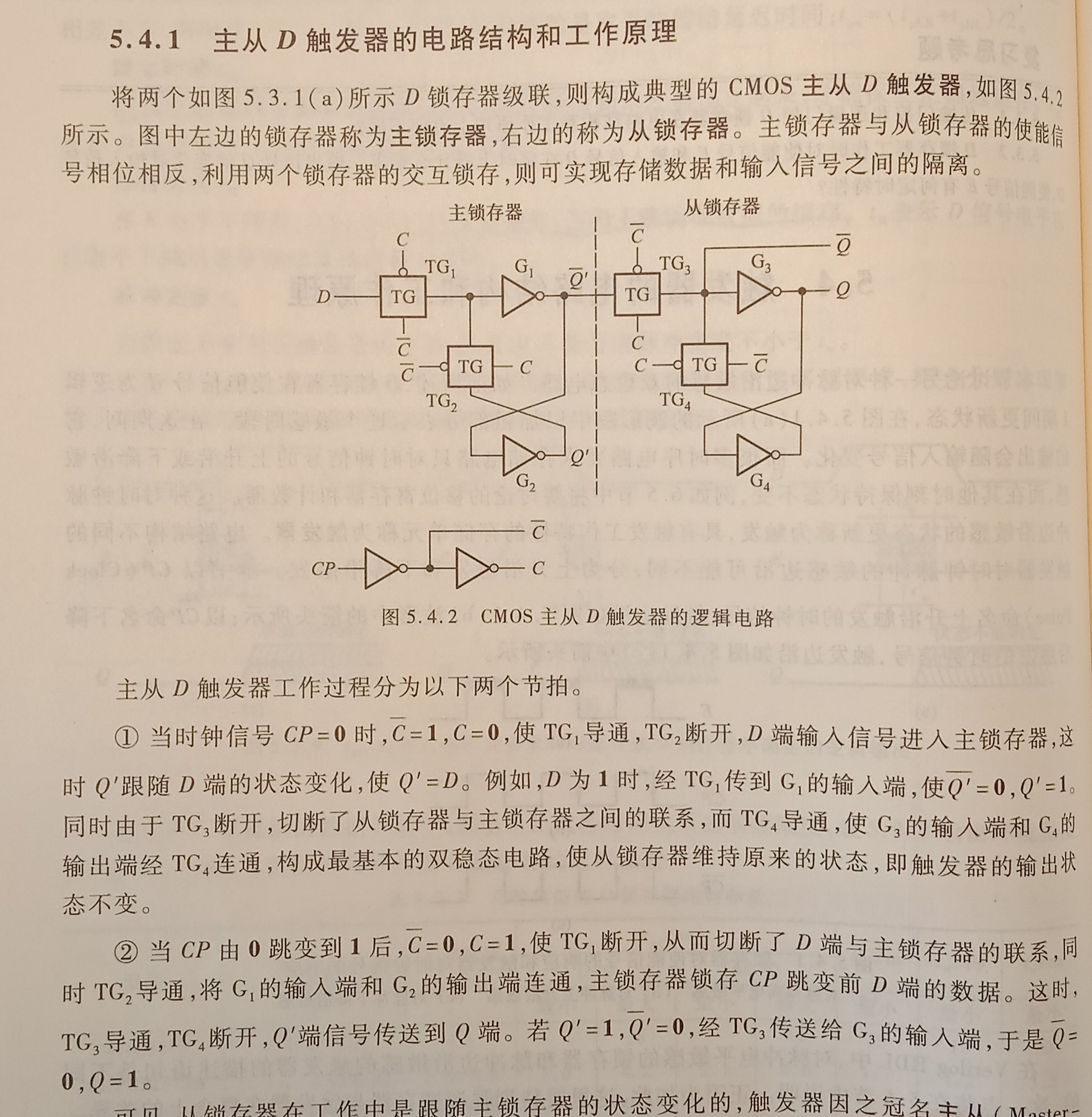

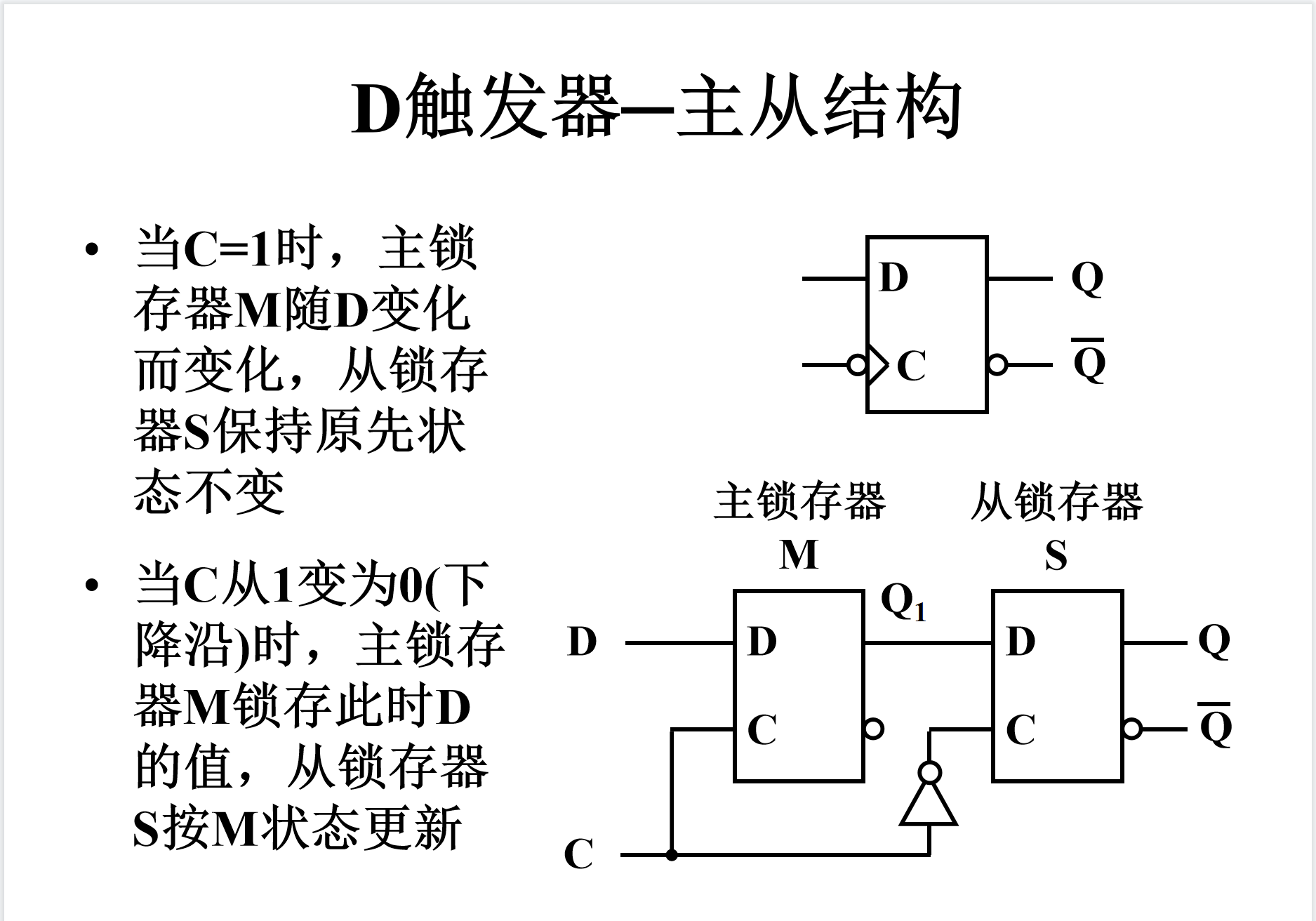

- 触发器如何保证在边沿改变

![image]()

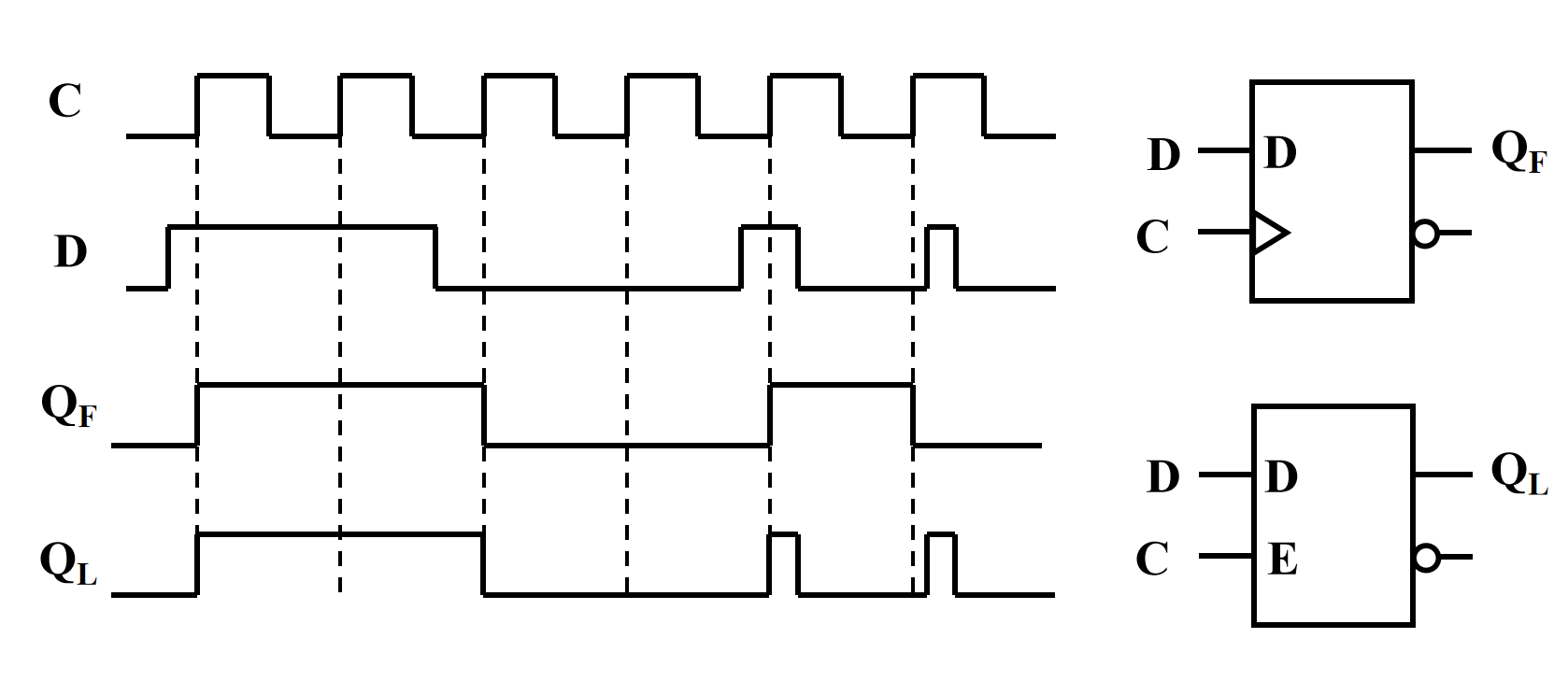

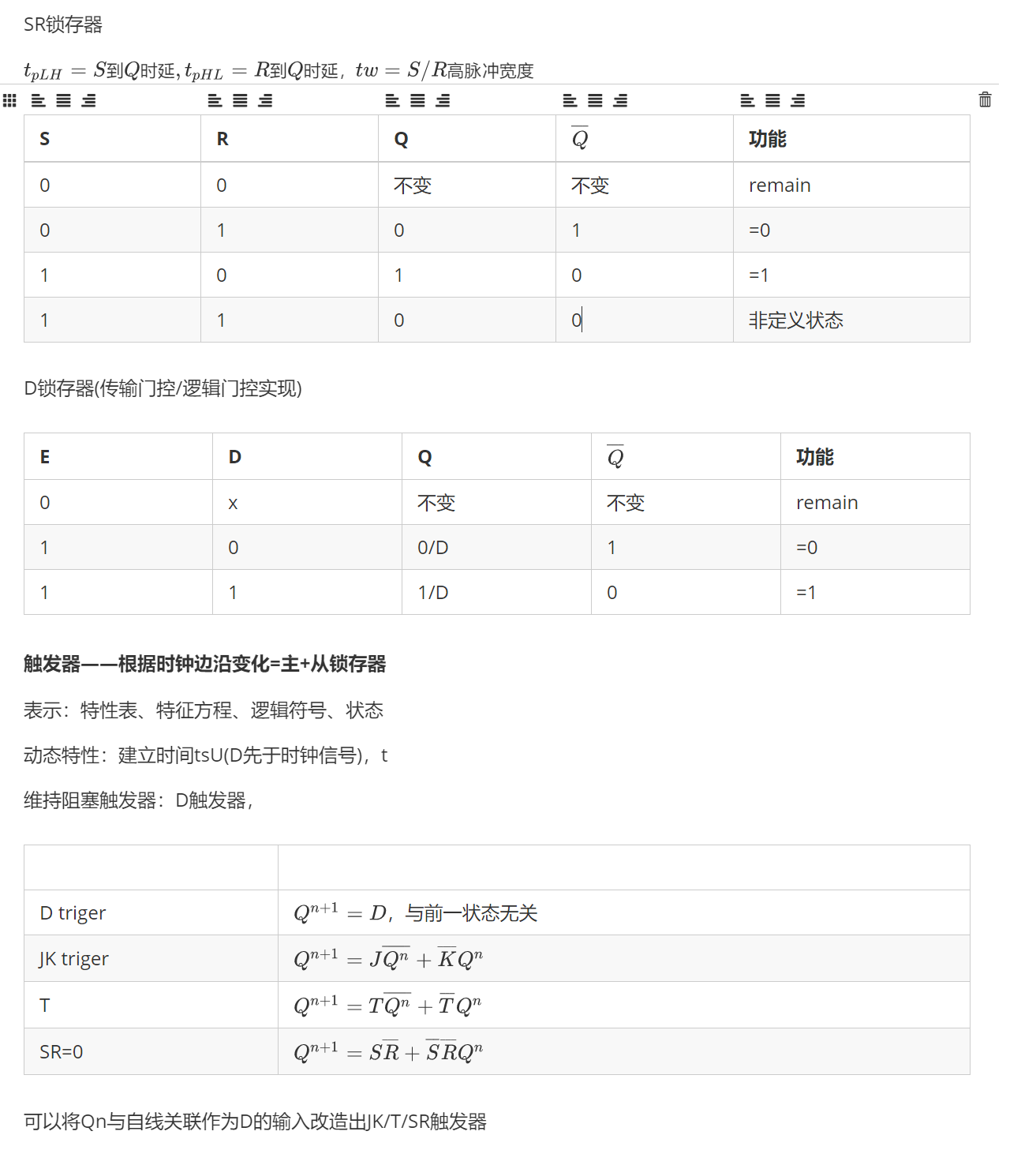

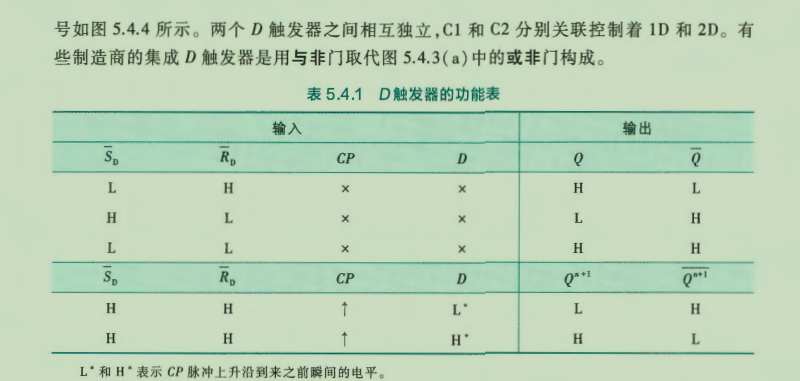

锁存器/触发器

- 锁存器是去掉输入信号,仍能保持状态的,直到改变信号

- 触发器只在间隔终端改变

![波形]()

![SR锁存器]()

![]()

![主从触发器]()

- 还有维持阻塞触发器、利用传输延迟的触发器

#D锁存器

module(Q,QN,D<E);

always@(E|D)

if(E) Q<=D

endmodule

#D触发器module D_flip_flop(

input [1:0] d,

input clk,

output reg[1:0] q,

output reg[1:0] qb

);

always @(posedge clk) //时钟上升沿触发D触发器

begin

q<= d ;

qb<= ~d ;

end

endmodule

#RS触发器

module SY_RS_FF ( R, S, CLK, Q, QB ); //模块名及参数定义,范围至endmodule。

input R, S, CLK; //输入端口定义

output Q, QB; //输出端口定义

reg Q; //寄存器定义

assign QB = ~Q; //assign语句,QB=/Q。

always @( posedge CLK ) //在CLK的上跳沿,执行以下语句。

case ({ R ,S }) //case语句,至于endcase为止。

1:Q <= 1; //当R,S的组合为01,则令Q=1。

2:Q <= 0; //当R,S的组合为01,则令Q=1。

3:Q <= 1'bx; //当R,S的组合为11,则令Q为1bit的数,数值为不定(x)。

endcase //case语句结束

endmodule //模块结束

#JK触发器

#T触发器

input T,

input clk,

output Q,

output QB,

always@(posedge clk)

begin

if(~reset)

begin

Q<=1'b0;

end

else

begin

if(T)

Q<=~Q;

QB<=~Q;

else

begin

Q<=Q;

QB<=~Q;

end

end

end

- 动态特性t:tpd(传输)+tSU(建立)+tH(终止)+tW(脉冲宽度)

细节

- 直接/异步清零:高电平则输出0;直接置数:高电平则输出1;

愿偿少年泪,犹趁未老时!

本文来自博客园,作者:clfire,转载请注明原文链接:https://www.cnblogs.com/sky1water/p/16778200.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号