2.组合电路设计(数电)

目录

根据逻辑功能设计逻辑图

- 画出真值表,给出input-output表达式

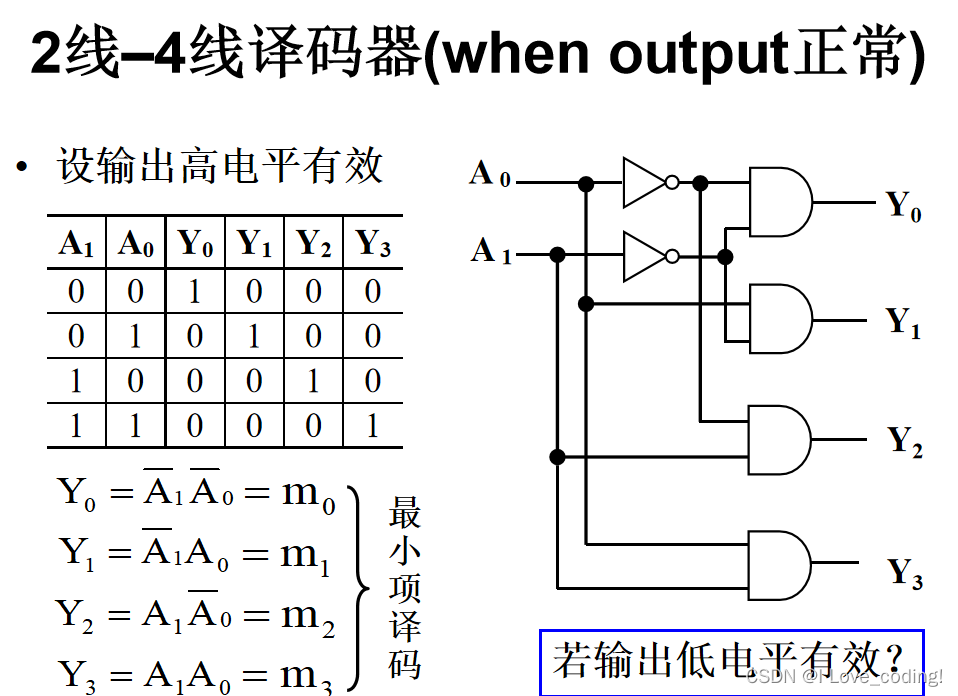

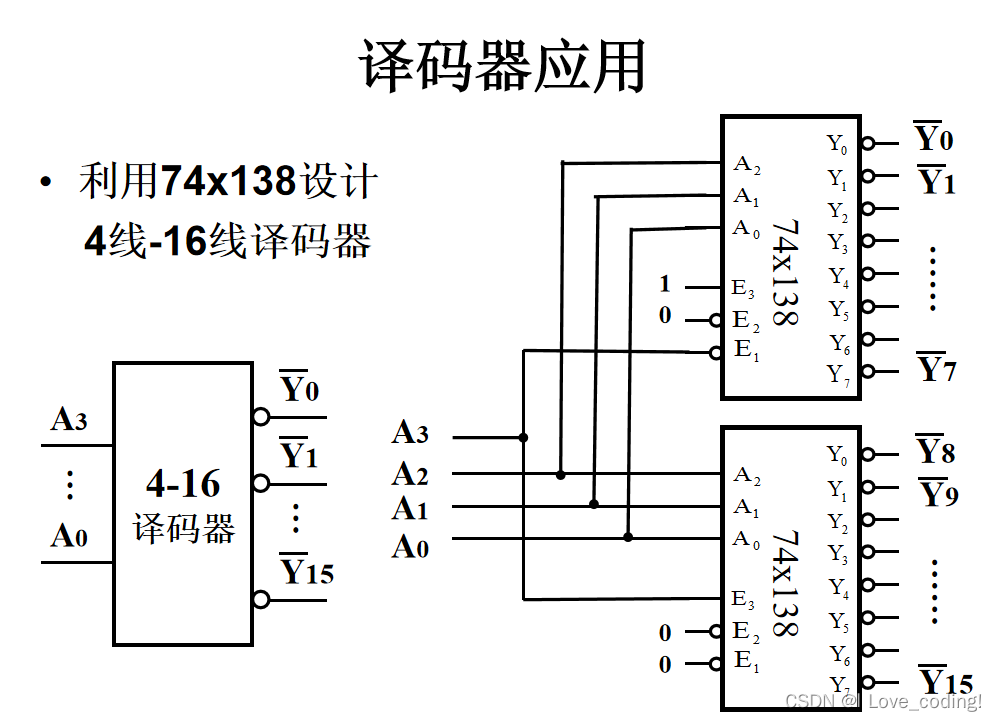

1. 编码器\(\iff\)译码器(&7段数码管)

- 2线-4线,3线-8线

- 优先编码器:Ii=1,outpu i,like 数据选择器

- 译码器取反,强电流

- 不看边界非门

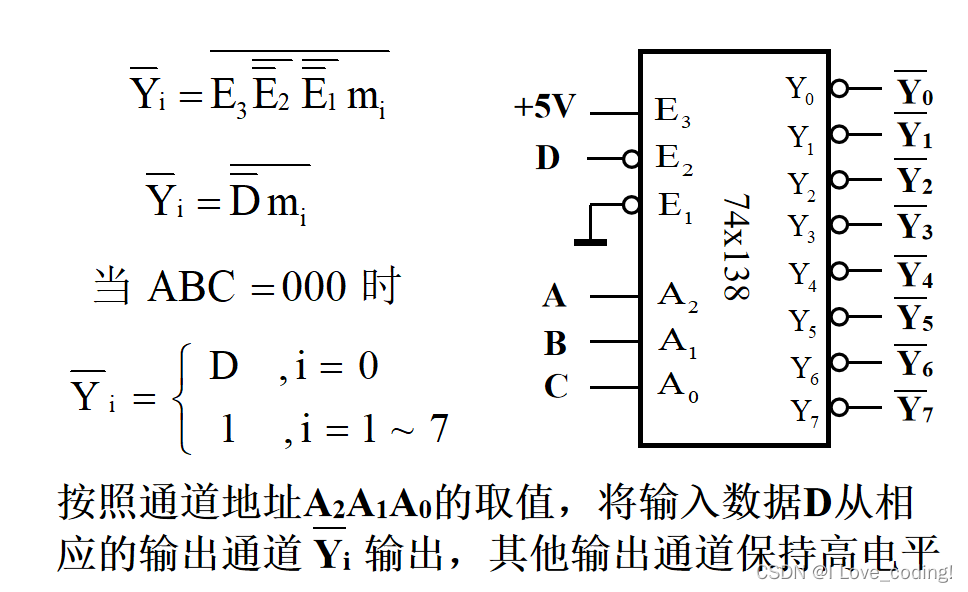

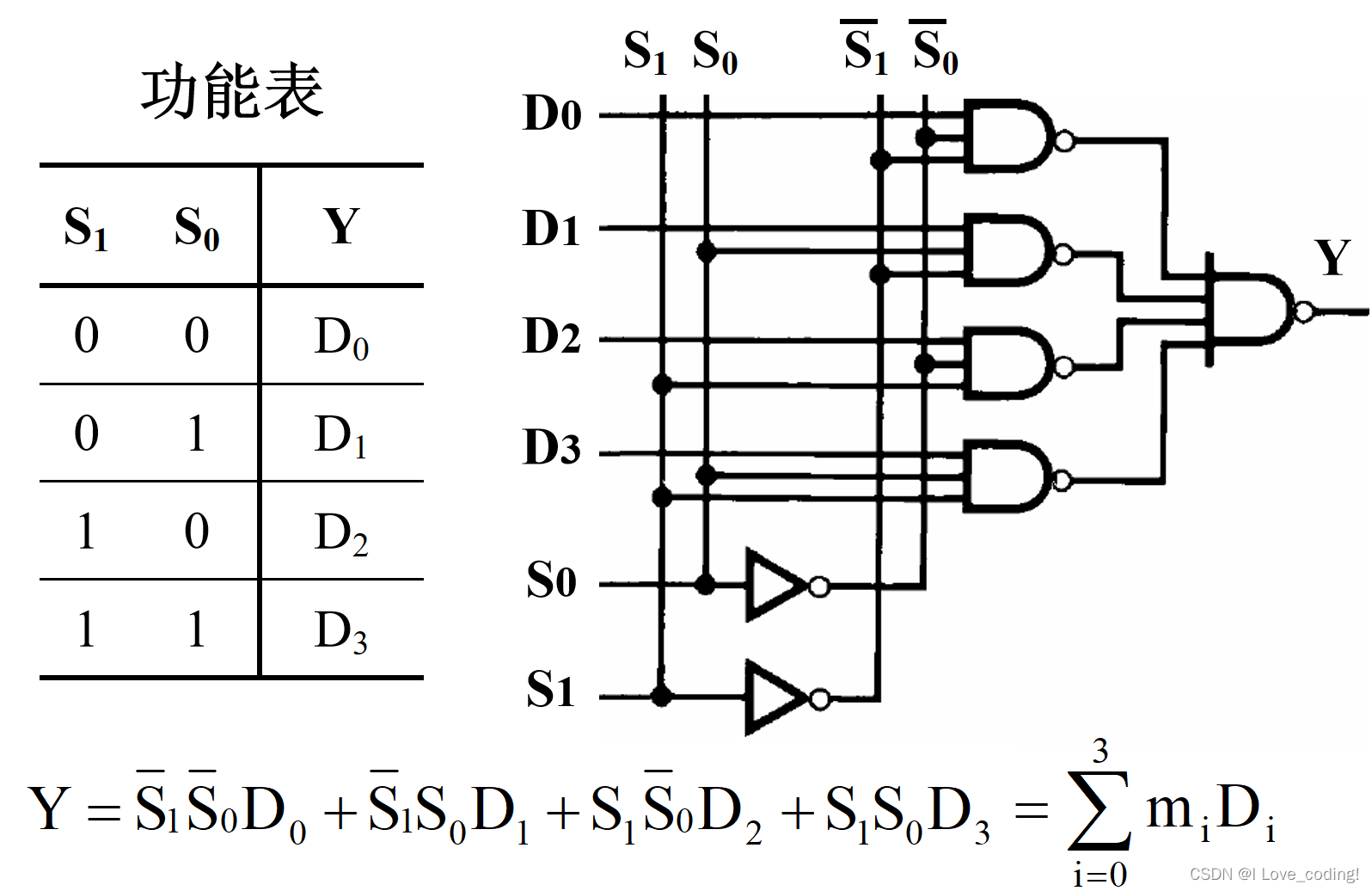

2. 数据选择器\(\iff\)数据分配器

- 数据分配器:将公共数据线上的数据分配到不同通道

数据分配器:从不同通道的数据选择一个输出到公共数据线 - 3-8译码器可视为对选择数据E2的分配器

- 数据选择器的与或式表达:\(\sum_{1}^{n} DiS1S2S3\)

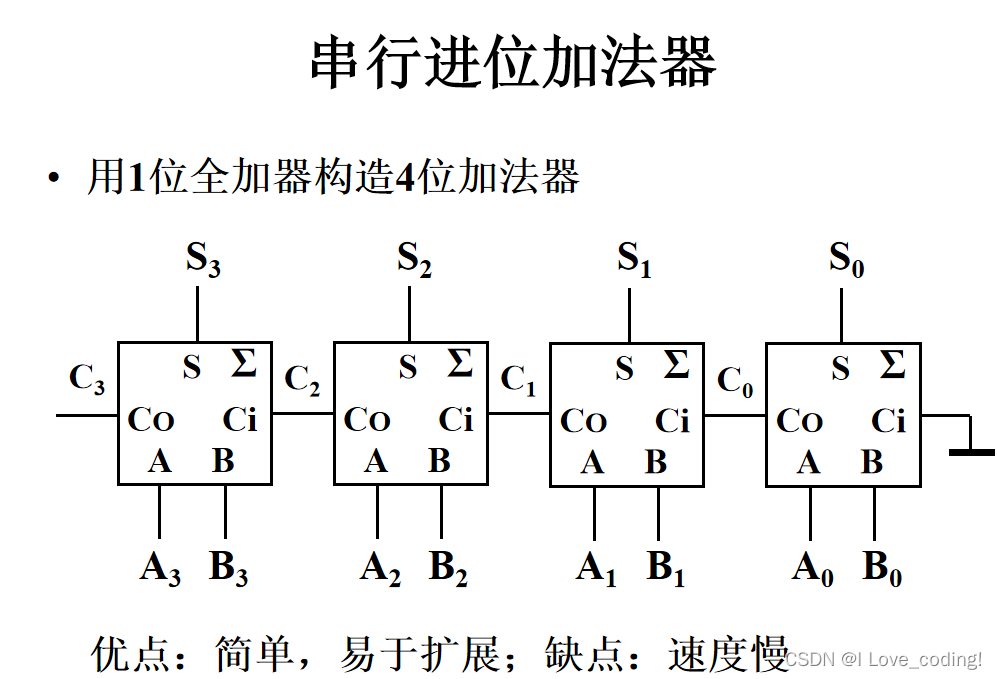

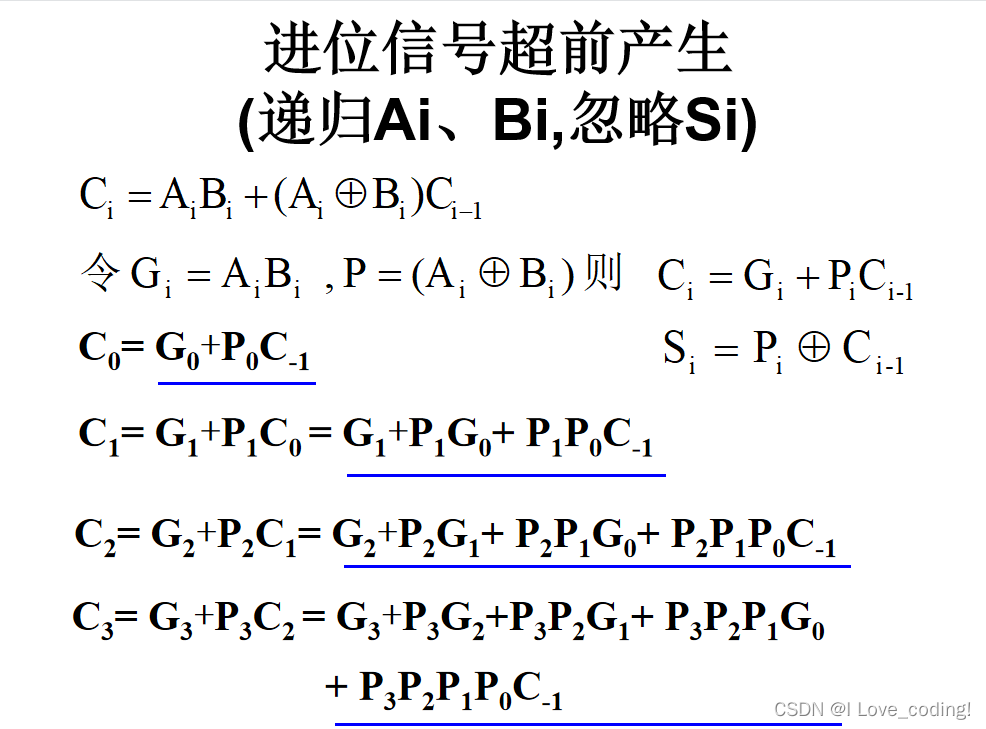

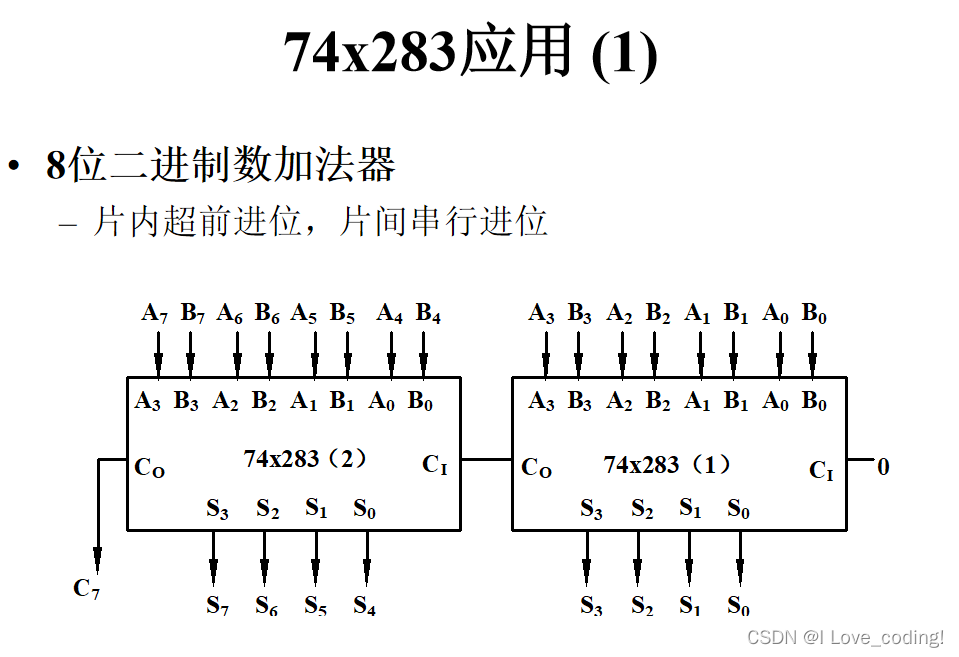

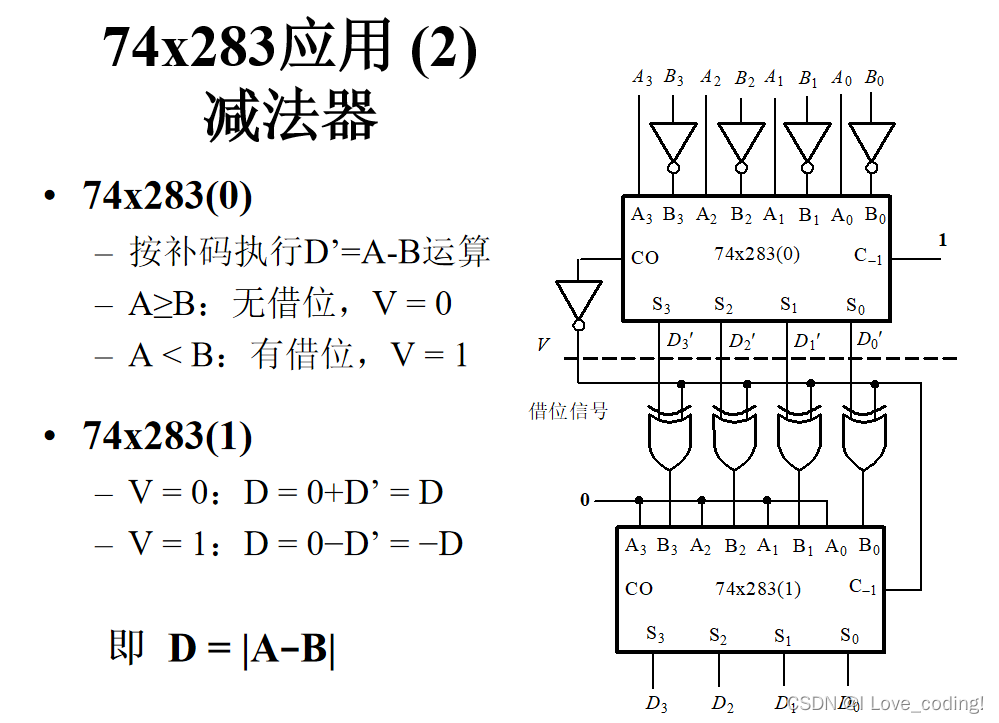

3. 加法器\(\rightarrow\)乘法器

4.数值比较器

- 实现余三码(0011~1100)

5.verilog规范

- module define input=wire,exemplify output=wire

- module transisition只能结构化表示,

愿偿少年泪,犹趁未老时!

本文来自博客园,作者:clfire,转载请注明原文链接:https://www.cnblogs.com/sky1water/p/16720537.html