AXI latency 理解【转】

转自:

一、Latency 基础:

AXI latency 是比较关键的部分,可以采用VIP的latency机制模拟硬件的latency 信息;其中latency机制的使用按照作用主体分为两块:一个是针对master VIP的,一个是针对Slave VIP的;

根据axi的握手机制:

写通道操作: master 负责操作:awvalid 、awaddr、wvalid 、 wdata 、 wlast 而slave 负责操作:awready 、wready

读通道操作:master 负责操作:arvalid、 araddr、ready 而slave 负责操作:arready、rdata 、rlast和rvalid

写响应通道: slave 负责发送 bvalid , master 负责操作bready,一旦master 拉高bready,那么bresp会立刻发送到master部分作为响应。

1)master vip + slave DUT;

vip作为master的情况下,主要操作包括axi 写、axi 读、axi 写响应;

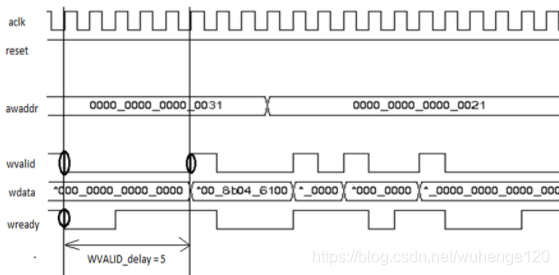

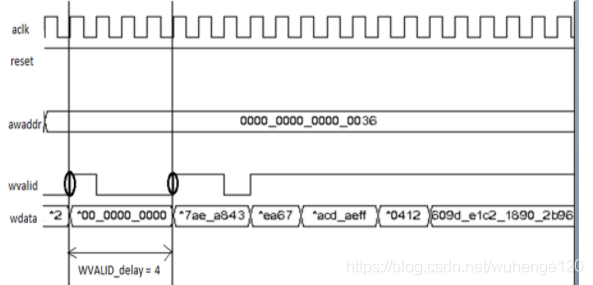

wvalid_delay:由master 主动控制,

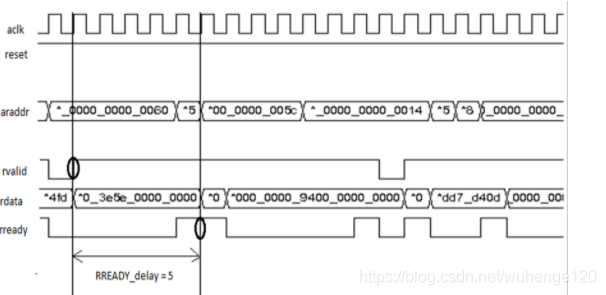

rready_delay:由master 主动控制;

2)master DUT + slave VIP:

vip作为slave 的情况,

wready_delay:由slave 来进行控制,什么时候给出ready信号,一遍master可以写入slave;

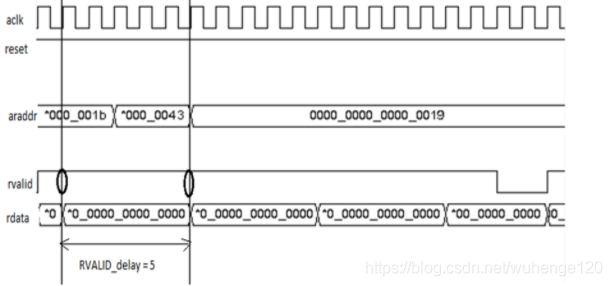

rvalid_delay:读数据时,由slave 来进行控制什么时候给数据。

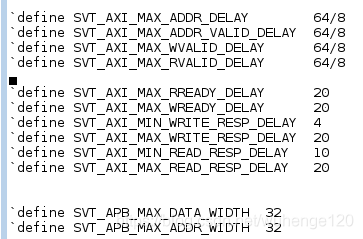

二、AXI latency 宏以及reference event

AXI delay control attributes

Description of address_valid_delay for reference

event PREV_ADDR_VALID for write address channel

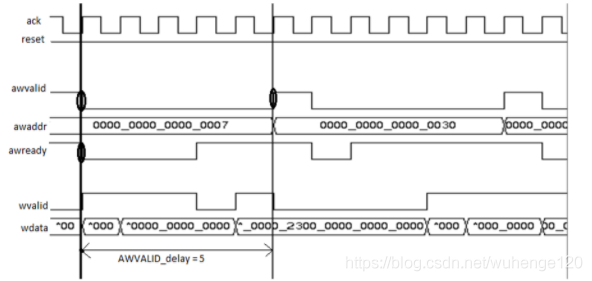

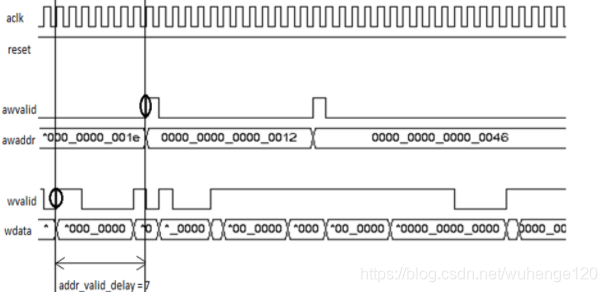

Addr_valid_delay defines the number of cycles the AWVALID signal is delayed with respect to the reference event PREV_ADDR_VALID. It is applicable only for the ACTIVE MASTER.

Description of address_valid_delay for

reference event PREV_ADDR_HANDSHAKE for write address channel

Addr_valid_delay defines the number of cycles the AWVALID signal is delayed with respect to the reference event PREV_ADDR_HANSHAKE. It is applicable only for the ACTIVE MASTER.

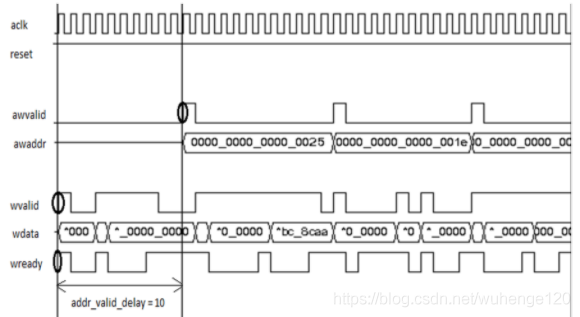

Description of address_valid_delay for

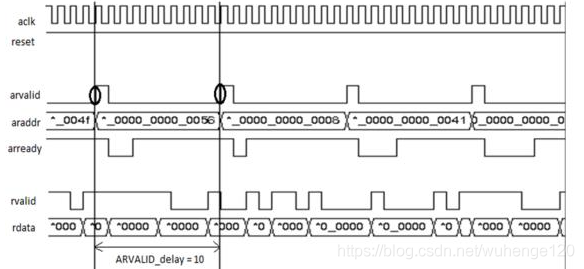

reference event PREV_ADDR_VALID for read address channel

Addr_valid_delay defines the number of cycles the ARVALID signal is delayed with respect to the reference event PREV_ADDR_VALID. It is applicable only for the ACTIVE MASTER.

Description of address_valid_delay for

reference event PREV_ADDR_HANDSHAKE for read address channel

Addr_valid_delay defines the number of cycles the ARVALID signal is delayed with respect to the reference event PREV_ADDR_HANDSHAKE. It is applicable only for the ACTIVE MASTER.

Description of bvalid_delay for reference

event LAST_DATA_HANDSHAKE for write response channel

Represents delay in terms of clock cycle for bvalid assertion with respect to the reference event LAST_DATA_HANDHAKE. It is applicable only for the ACTIVE SLAVE.

Description of bvalid_delay for

reference event ADDR_HANDSHAKE for write response channel

Represents delay in terms of clock cycles for bvalid assertion with respect to the reference event ADDR_HANDHAKE. It is applicable only for the ACTIVE SLAVE.

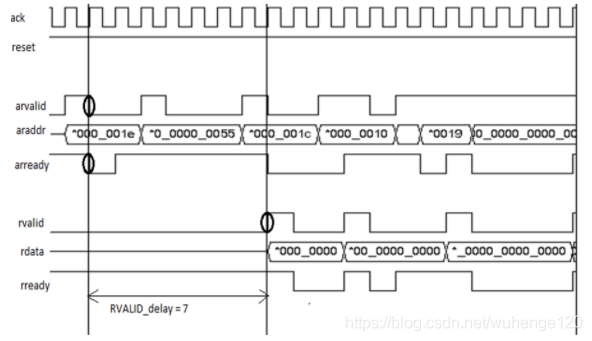

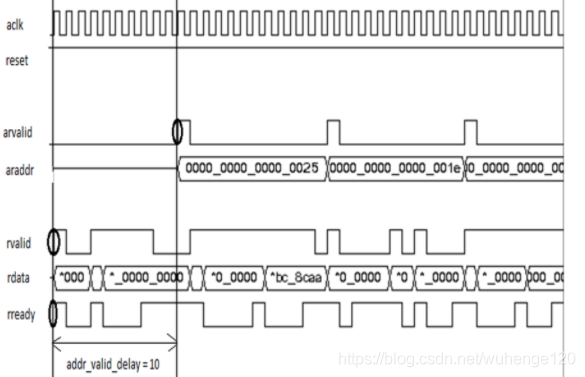

Description of first rvalid_delay for

reference event READ_ADDR_VALID for read data channel

Represents a delay for the first RVALID assertion with respect to the reference event READ_ADDR_VALID. It is applicable only for the ACTIVE SLAVE.

Description of first rvalid_delay for

reference event READ_ADDR_HANDSHAKE for read data channel

Represents a delay for the first RVALID assertion with respect to the reference event READ_ADDR_HANDSHAKE.

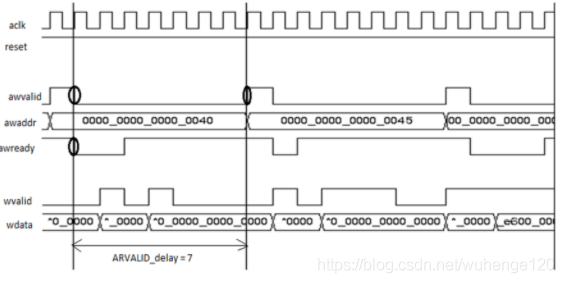

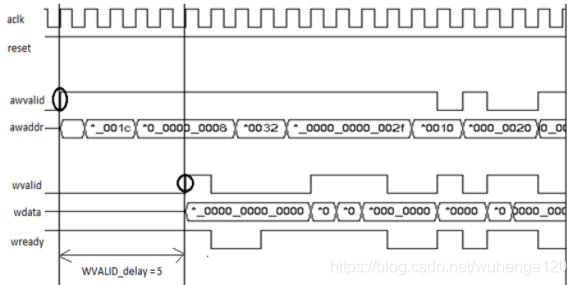

Description of first wvalid_delay for

reference event WRITE_ADDR_VALID for write data channel

Represents a delay for the first WVALID assertion with respect to the reference event WRITE_ADDR_VALID.

Description of first wvalid_delay for

reference event WRITE_ADDR_HANDSHAKE for write data channel

Represents a delay for the first WVALID assertion with respect to the reference event WRITE_ADDR_HANDSHAKE.

Description of first wvalid_delay for reference event PREV_WRITE_DATA_HANDSHAKE for write data channel

Represents a delay for the first WVALID assertion with respect to the reference event PREV_WRITE_DATA_HANDSHAKE.

Description of rready_delay for

reference event RVALID for read data channel

Represents a delay for the first RREADY assertion with respect to the reference event RVALID.

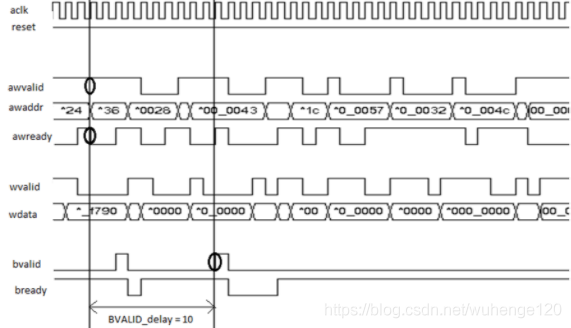

Description of wready_delay for reference event WVALID for write data channel

Represents a delay for the first WREADY assertion with respect to the reference event WVALID.

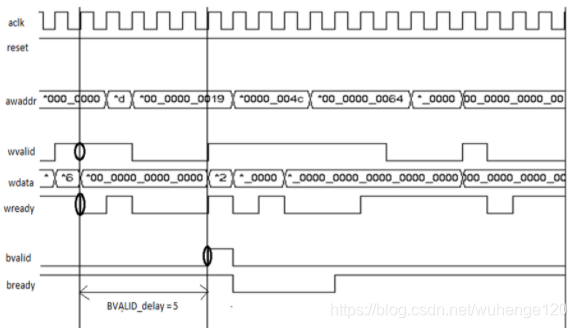

Description of bready_delay for reference event BVALID for write response channel

If configuration parameter svt_axi_port_configuration :: default_bready is FALSE, this member defines the BREADY signal delay in number of clock cycles. The reference event for this delay is assertion of bvalid.

If the configuration parameter svt_axi_port_configuration :: default_bready is TRUE, this member defines the number of clock cycles for which BREADY signal should be deasserted after each handshake, before pulling it up again to its default value.

Represents the bready delay for reference event BVALID for default_bready is TRUE. It is applicable only for the ACTIVE MASTER.

Description of next rvalid_delay for reference event PREV_RVALID for read data channel

Represents a delay for the next RVALID assertion with respect to the reference event PREV_RVALID.

Description of next rvalid_delay for reference event PREV_READ_HANDSHAKE

for read data channel

Represents a delay for the next RVALID assertion with respect to the reference event PREV_READ_HANDSHAKE.

Description of next wvalid_delay for reference event PREV_WVALID for

write data channel

Represents a delay for the next WVALID assertion with respect to the reference event PREV_WVALID.

Description of next wvalid_delay for reference

event PREV_WRITE_HANDSHAKE for write data channel

Represents a delay for the next WVALID assertion with respect to the reference event PREV_WRITE_HANDSHAKE.

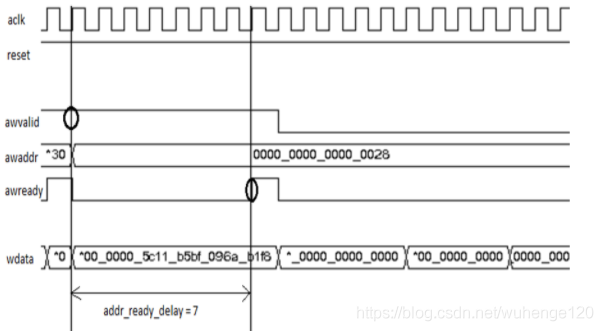

Description of addr_ready delay for reference

event ADDR_VALID for write address channel

If the configuration parameter svt_axi_port_configuration :: default_awready is FALSE, this member defines the AWREADY signal delay in number of clock cycles. The reference event used for this delay is addr_valid.

If the configuration parameter svt_axi_port_configuration :: default_awready is TRUE, this member defines the number of clock cycles for which AWREADY signal should be deasserted after each handshake, before pulling it up again to its default value. It is applicable only for the ACTIVE SLAVE.

Description of addr_valid_delay for reference event FIRST_DATA_HANDSHAKE_DATA_BEFORE_ADDR for read address channel

Addr_valid_delay defines the number of cycles the ARVALID signal is delayed with respect to the reference event FIRST_DATA_HANDSHAKE_DATA_BEFORE_ADDR. It is applicable only for the ACTIVE MASTER.

Description of addr_ready_delay for reference

event ADDR_VALID for read address channel

If the configuration parameter svt_axi_port_configuration :: default_arready is FALSE, this member defines the ARREADY signal delay in number of clock cycles. The reference event used for this delay is addr_valid.

If the configuration parameter svt_axi_port_configuration :: default_arready is TRUE, this member defines the number of clock cycles for which ARREADY signal should be deasserted after each handshake, before pulling it up again to its default value. It is applicable only for the ACTIVE SLAVE.

Description of addr_valid_delay for reference event FIRST_WVALID_DATA_BEFORE_ADDR

for write address channel

Addr_valid_delay defines the number of cycles the AWVALID signal is delayed with respect to the reference event FIRST_WVALID_DATA_BEFORE_ADDR. It is applicable only for the ACTIVE MASTER.

Description of addr_valid_delay for reference event FIRST_DATA_HANDSHAKE_DATA_BEFORE_ADDR

for write address channel

Addr_valid_delay defines the number of cycles the AWVALID signal is delayed with respect to the reference event FIRST_DATA_HANDSHAKE_DATA_BEFORE_ADDR. It is applicable only for the ACTIVE MASTER.

————————————————

版权声明:本文为CSDN博主「wuhenge120」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/wuhenge120/article/details/114824255

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· 阿里巴巴 QwQ-32B真的超越了 DeepSeek R-1吗?

· 【译】Visual Studio 中新的强大生产力特性

· 【设计模式】告别冗长if-else语句:使用策略模式优化代码结构

· AI与.NET技术实操系列(六):基于图像分类模型对图像进行分类

2017-05-17 关于platform_device和platform_driver的匹配【转】

2017-05-17 VS Code开发技巧集锦【转】